Teledyne e2v的宇航级DDR4的硬件设计指南

摘要

快速、高可靠和耐辐射的存储是复杂空间边缘计算系统的必备特性。DDR4 将使航天工业实现更高吞吐量的星上计算能力和更长的采集时间,从而支持全新的地球观测、空间科学和电信应用,例如超高分辨率图像、实时流媒体视频和星载人工智能。

我之前介绍过面向宇航应用的 Teledyne e2v 的耐辐射 DDR4 (DDR4T04G72),可提供 4GB 的存储容量,高达1.2GHz的时钟频率和 2.4GT/s 的数据速率(带宽为 172.8Gb/s),本文将更深入地介绍这款宇航级 DDR4 存储器的细节。

本文的第一部分将讨论 SDRAM的技术实现,然后扩展到 DDR4 的架构和结构,因为 DDR4 包含了最新的架构和硬件特性,需要首先考虑这些要素以确保设计的正确性。

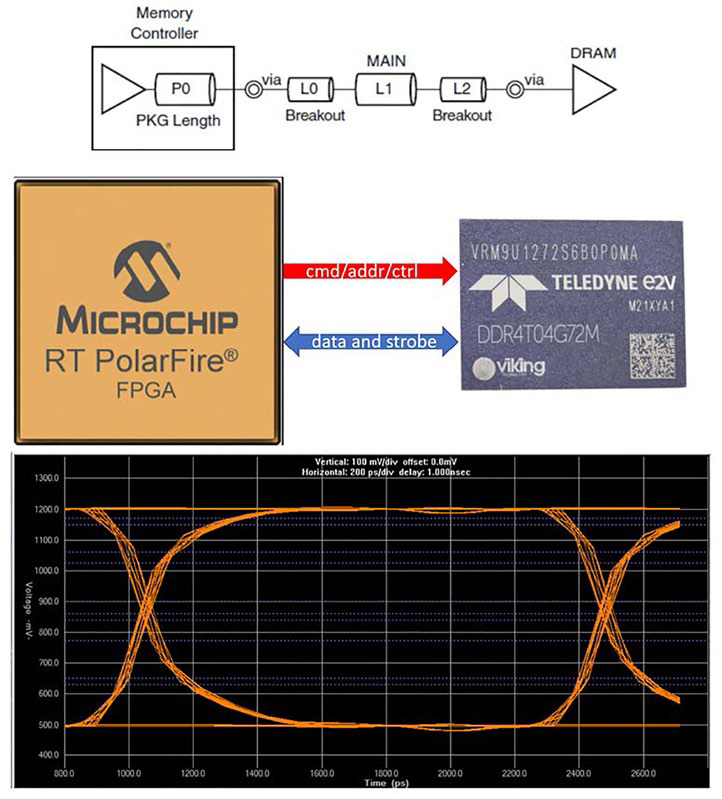

随后,我将重点介绍 PolarFire FPGA 和 Teledyne e2v DDR4T04G72 之间点对点的连接的例子,以及多个 DDR4器件如何与一片 Xilinx KU060 FPGA 连接。

最后,我将介绍DDR4 相比于DDR3 的优点,以及单模式和多模式的DDR4 配置及容量。

我之前介绍过这款面向宇航应用的 DDR4,可提供 4GB 的存储容量,高达 1.2GHz 的时钟频率和 2.4GT/s 的数据速率(带宽为 172.8Gb/s)。与前几代 SDRAM 相比,DDR4 包含新的架构和硬件特性,提高了容量、性能、可扩展性、系统可靠性和电气效率。除了上述内容,本文还将讨论时序和信号完整性,以及如何将这个存储器和FPGA 连接,以确保电子设计的正确性。

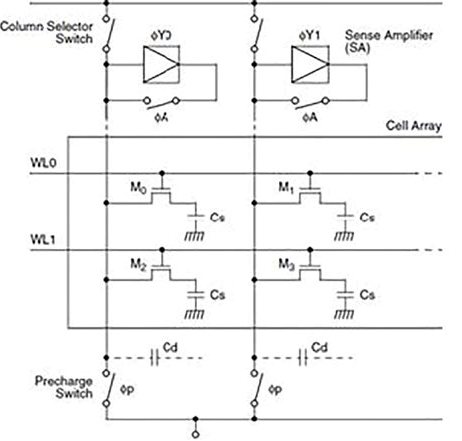

SDRAM 的架构由多个存储单元组成,这些存储单元组织在一个二维的行和列的数组中,如图 1 所示。要选择一个特定的位,首先需找到相关的行,然后是相关的列。一旦选通所需的行,就可以访问多个列,从而通过连续的读/ 写操作提高速度并减少延迟。

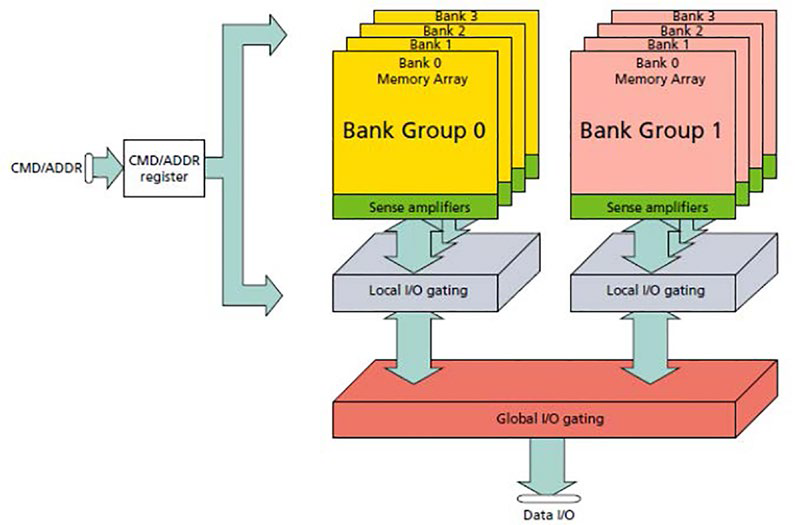

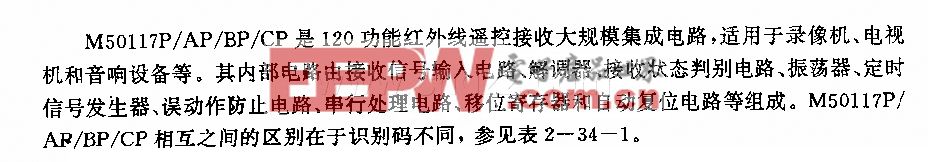

为了增加字的大小,存储器包含多个数组,而当请求读/ 写访问时,存储器只需要一个地址来访问每个数组中的某一位。为了增加总的存储容量,SDRAM 的内部结构包含许多 bank,如下图所示。这些交错的 bank 进一步提高了性能,每一个 bank 都可以被独立寻址。

图1 SDRAM 的bit cell 和 DDR 芯片的结构

SDRAM 的核心速度比它的 I/O 速率慢。在每个列指令期间可访问多个数据字,然后这些数据被序列化到接口。DDR4基于 8n 预取架构,每个时钟周期在 I/O 传输两个 n 位宽的数据字。一个读/写操作包括一个单独的 8n 位宽、4 个周期的在DRAM核心上的传输操作和对应的8 个n 位、一个半周期的I/O 端口传输操作。

DDR4扩展了上述 SDRAM架构,引入了 bank 组的概念,允许在一个组中预取8个,并在另一个组中独立执行另一个操作。实际上,DDR4时分复用其内部的 bank 组,以隐藏内部核心比 I/O 端口传输8个字需要更多的时间这一事实。与 DDR3相比,DDR4 通过更多的 bank 和更小尺寸的行,使器件能够以更高的速率访问不同的bank,从而提高性能。 DDR4 存储器的结构如下图所示。为了支持更大的存储容量而不增加额外的地址引脚,DDR4 使用全新定义的 ACT_n输入到命令管脚 RAS、CAS 和 WE 的复用地址。如果 ACT_n 为低,这些输入被分别用作地址 A16、A15 和 A14 脚。如果ACT_n 为高,它们则恢复为SDRAM 命令真值表中指定的正常功能。

图 1 EV12AQ600 的不确定性源和积累延迟

Teledyne e2v的4GB耐辐射DDR4T04G72是一款包含5个裸片的MCP,其中4个分别提供 1GB(8Gb)的存储(512Mb x 16 位),组成2组,每组有4个 bank,如上图所示。为了提高可靠性,它使用72位的数据总线,包含64位数据和8位错误检测修复。这个ECC功能在第5片裸片中实现。该器件使用一个内部的8n预取缓冲以最大限度地高速运行,并提供可编程的读、写和附加延迟。

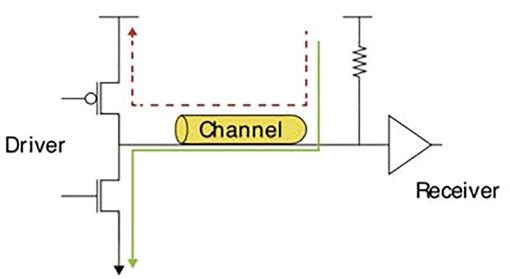

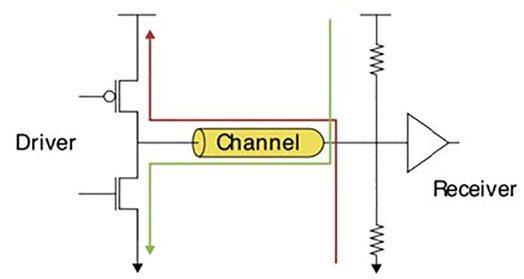

DDR4引入了一些硬件特性以降低功耗。首先,I/O供电(VDDQ)从DDR3使用的1.35V降低到1.2V。增加了一个独立的2.5V供电Vpp,用来激活内部字线并降低10%的功耗。数据总线的 I/O 电气接口从推挽 SSTL 变为下图所示的伪开漏(POD)信号。通过截止到VDDQ而不是1/2的VDDQ,信号摆动的幅值和中心可根据不同设计的需要定制。POD的I/O降低了驱动数据时的开关电流,因为只有0时才消耗功率。DDR4还提供数据总线倒置,以分配更少的位,降低热量和功耗。通过减少开关的次数,可减少噪声,并实现更干净的数据眼图。

图3 DDR3 的推挽 I/O 信号(左)vs. DDR4 的POD(右)

总的来说,降低的VDDQ电压、使用外部Vpp供电操作字线、使用POD信号和VDDQ截止,以及前面讨论的更小的行尺寸和激活电流,都使得DDR4的整体功耗比DDR3 SDRAM大大降低。在类似的数据速率下,DDR4 器件大约减少了30%的功耗。这使得用户可以实现更高的速度,或以更低的功耗实现相同的性能。我们可提供DDR4T04G72的功耗预测表和ICEPAK/ECXML热模型。

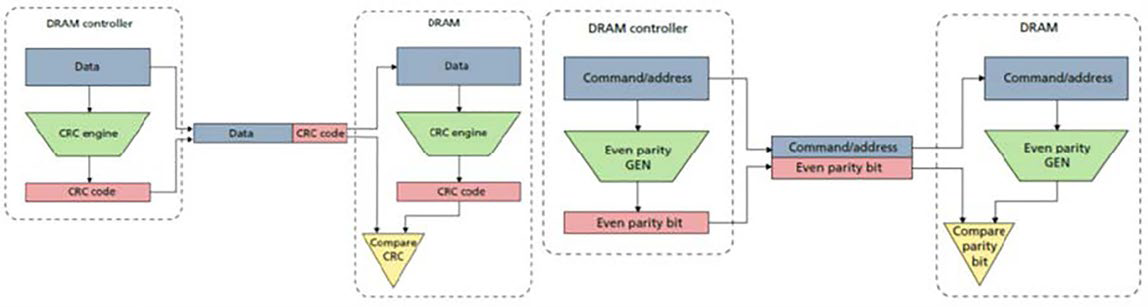

在系统的层面,DDR4提供了更高的可靠性、可用性和可服务(RAS)。数据总线在写操作时的CRC错误检测和命令、地址总线的奇偶校验如下图所示。与DDR3不同,DDR4可被配置为当检测到奇偶校验错误时停止命令。

图4 DDR4 提供的系统级错误检测

对于那些在存储器的生命周期里无法使用ECC修复的软错误,DDR4提供了一个“包后修复”的功能来纠正出现故障的行。这不仅提高了系统的可靠性和寿命,而且提供了一种进一步防止单粒子翻转的机制。

DDR4还提供了连接性测试模式(CT),用来在不调用SDRAM的初始化序列的情况下检查内存和控制器之间的PCB走线的连续性。传统的边界扫描测试在每个时钟周期串行移入和移出测试序列,与之不同,CT模式使用更快的并行接口。

DDR4的I/O接口是真正的源同步设计,使用双向数据选通DQS,每个时钟周期捕获两次数据。在写操作时,DQS由存储器输出,与数据相关;对于写操作,DQS由以数据为中心的控制器提供,提供同步参考。为了保证数据速率增加、幅度减小时的数据完整性,时钟和strobe信号是差分的,以抵消共模噪声。在PCB层面,DQS对数据总线有相同的负载,布线方式类似。其余的地址、命令、控制和数据信号依然工作在单端模式,更容易受到噪声、串扰和干扰的影响。

在PCB布线之前,需决定为布线不匹配留出多少时间余量,这一点很重要。我们可以考虑时间占整个周期的比例,例如时钟频率是1.2GHz 时,一个周期是833ps。对于FR4的典型飞行时间是6.6ps/mm,所以1mm的走线大约消耗整个周期的1.6%。如果您的设计并不要求实现性能的极限,您可以为整体的线长不匹配留出较大的余量,以提高布线灵活性,简化布线的工作。

当计算PCB的传递延迟时,需注意内层(带状线)和外层(微带线)的延迟不同,因为它们的有效介电常数不同。过孔引入了Z方向上额外的长度,需匹配的线上的过孔数目应该相同,并有着相同的跨度,以忽略它们对整体时间特性的影响。

在加工PCB之前,建议进行布线后仿真,以确认时间余量和信号完整性。Teledyne e2v可提供DDR4T04G72的IBIS和Spice模型,使您可在设计早期确认电气和时序是否满足要求。我是用Mentor Graphics(现在是 Siemens)的Hyperlynx Linesim和Boardsim分别验证布线前和布线后的信号完整性,优化终端和驱动能力,并验证时间余量,以便在投产前确认没有问题。目前,另一种EBD模型也正在开发中。

为了验证使用内部布线层的控制器和存储器之间的信号完整性,可参考PolarFire耐辐射FPGA与单片DDR4T04G72连接 的数 据线 的Linesim预测的眼图(图 5)。多个DDR4设备也可通过各自的IP控制器连接到单片FPGA上。

图5 PolarFire 和 DDR4T04G72 的点对点连接

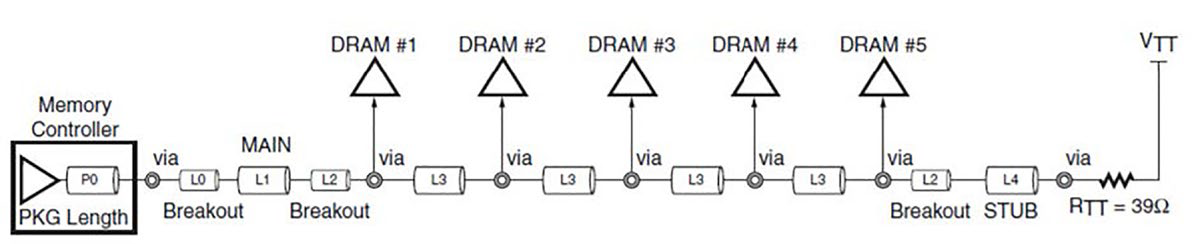

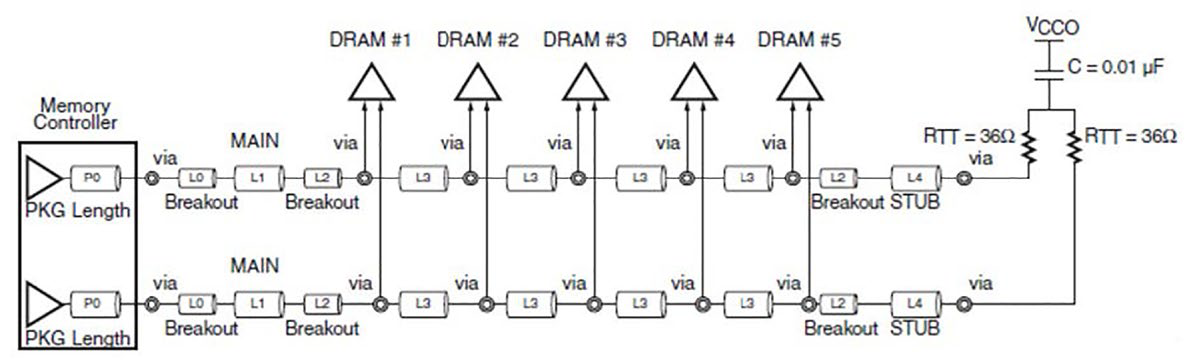

为了增加总体的存储容量,相同的软IP可控制fly-by或clamshell拓扑的多个DDR4器件,即公共时钟、地址、控制和数据信号,而每片SDRAM有各自的片选输入信号,如下图所示。在这种情况下,传输线更长,容性负载更大,因此需要通过仿真来确定所需的驱动器电流强度。每个KU060 DDR4控制器的最大数据总线宽度是80位,可访问最多5个外部存储器,而FPGA可实例化其中的两个IP。

图6 多个DDR4 器件与Xilinx KU060 FPGA 的连接

Xilinx提供了一个视频,演示如何实例化一个DDR控制器及其资源,以计算最大速率和可连接到FPGA的外部SDRAM设备的数量。PolarFire 的DDR4 IP提供了72位的数据总线宽度,允许上述的4 个DDR4T04G72的连接。

当DDR4T04G72连接到Xilinx的KU060或Microchip的PolarFire耐辐射FPGA时,数据速率分别为1.33GT/s和1.86GT/s时的存储容量和带宽如表1所示。可在FPGA中实例化的DDR4 IP的总数取决于您I/O使用的具体情况,所以请使用 Vivado® Design Suite 或 Libero® SoC确认您的配置。NanoXplore的NG-Ultra也将支持DDR4SDRAM。

表1 系统存储容量和带宽

Xilinx提供了一个视频,演示如何实例化一个DDR控制器及其资源,以计算最大速率和可连接到FPGA的外部SDRAM设备的数量。PolarFire 的DDR4 IP提供了72位的数据总线宽度,允许上述的4 个DDR4T04G72的连接。

当DDR4T04G72连接到Xilinx的KU060或Microchip的PolarFire耐辐射FPGA时,数据速率分别为1.33GT/s和1.86GT/s时的存储容量和带宽如表1所示。可在FPGA中实例化的DDR4 IP的总数取决于您I/O使用的具体情况,所以请使用 Vivado® Design Suite 或 Libero® SoC确认您的配置。NanoXplore的NG-Ultra也将支持DDR4SDRAM。

图7 DDR4 的命令、地址和控制信号的Fly-by 终端

图8 DDR4 的差分时钟输入的 Fly-by 终端

DDR4有片上的核心和I/O的电容,因此,没有必要为每对功率引脚分配外部电容。然而,需要为DDR4T04G72指定最小的PCB解耦,以防止SDRAM核心刷新、读写时造成供电下降。解耦还为读操作提供输出的驱动电流。

核心的频率越低,所需的电容越大,而在高频工作下的驱动开关则需要低电感和更小的电容。您已经完成了原理图设计、布线、预制时序和信号完整性检查,分包了PCB的组装,并验证了板子能正常加电。

现在可以开始使用存储器了。但是,在操作之前,必须先初始化DDR4,这样SDRAM才能识别其工作频率和延迟参数。 DDR3使用一个分压器创建Vdd/2,以作为参考来决定DQ信号是0还是1,如图3所示。DDR4使用一个内部电压参考,VrefDQ,它的值必须在初始化阶段由存储器控制器设置。此外,SDRAM需要定期校准输出驱动阻抗和ODT值,以最小化电压和温度的变化的影响,这一过程被称为ZQ校准。在使用DDR4前的最后一步是存储器训练,即计算SDRAM和对应控制器之间的读/写延迟。如图6所示,对于连接到FPGA的多个DDR4芯片,可能每个设备与控制器的距离都不同,导致时钟、strobe和数据之间的飞行时间偏差。写校准可以补偿这些偏差。在fly-back拓扑中,每个芯片在不同的时间接收命令、地址和控制,读写中心始终捕获眼图的中间位置,确保数据可以可靠地从SDRAM读取或写入到SDRAM。存储器训练在初始化时校准这些接口,确保操作之前有足够的余量。

总而言之,DDR4 将使卫星行业实现更高吞吐量的星上处理和更长的采集时间,并应用于全新的地球观测、空间科学和电信应用,例如超高分辨率图像、实时流媒体视频和星上人工智能。如前所述,DDR4 包含新的架构和硬件特性,需要首先考虑这些要素以确保设计的正确性。除了器件的数据手册,Teledyne e2v 还可提供 DDR4T04G72 的使用指南。

DDR4 将首次允许卫星和航天器制造商使用大存储带宽。在过去的 6 年里,我们的商业级应用伙伴一直在使用这种大存储带宽。与现有的经过认证的 DDR3 SDRAM 相比,DDR4T04G72可与最新的宇航级 FPGA 和微处理器配合使用,使得:

● 内存带宽增加62%(0.172 Tb/s,数据速率2.4GT/s),加倍当前的传输速度

● 存储容量增加25%

● 物理尺寸减少 76%

● 功耗减少30%

Rajan Bedi 博士是 Spaceships 公司的 CEO 和创始人,该公司设计和制造一系列先进的 L 到 K 波段的超高吞吐量星上处理器、应答机和 OBC,用于通信、地球观测、导航、互联网和 M2M/IoT 卫星。公司还提供宇航电子设计咨询、航空电子测试、技术营销、商业智能和培训服务。

Spaceships 的设计咨询服务研发定制的卫星和航天器子系统,并为客户提供建议,例如如何使用和选择合适的器件,如何设计、测试、组装和制造宇航电子系统等。我们在 FPGA 的宇航应用培训课程上教授半导体存储器的相关内容。

评论