5G毫米波基带数据传输的研究与实现

0 引言

随着全球移动通信技术向着网络化和宽带化趋势发展,5G 商用的步伐已经到来。5G 商用的基站和手机也已经开始部署与批量生产。现在,仪表除了能够分析6 GHz 以下频率的信号以外,还需要分析微波、毫米波等波形。毫米波传输的技术难点主要在于5G 极高速的传输速率导致信号带宽和基带信号处理速度都将大大增加,对极高速数据流的实时处理和解析使得测试变得更加困难,作为测试技术的先行者,测试仪表5G 功能毫米波测试技术开发也已提上日程[1]。

毫米波现在的信号带宽已经达到400 MHz,如此宽的信号带宽需求对信号的采样率提出了很高的要求,前端的AD 处理是信号成功采集的第一步。随着技术的快速发展,AD 处理能力也得到了较高提升,具有大于5 Gsps 采样处理能力的采集单元也已经问世,为毫米波的成功实现奠定了基础。实现过程中选定的AD 芯片一般具有较高采样率,简化了RF 信号到数字信号的接口要求。内部集成数字下变频器(DDC),以及数控振荡器(NCO)和输出数据提供了串行连接可配置的JESD204B 的接口。

基带接收处理模块是满足多通道接收、不同系统带宽、不同子载波间隔、多用户基带接收的指标要求,完成参数灵活可配单用户、多用户基带信号接收功能,满足5G 终端的低延时、高效率、高质量的处理能力。FPGA 是现阶段实现采用的主流方式,具有处理较强的数字能力,设计采用了Xilinx 公司的FPGA 芯片作为主要的实现平台。

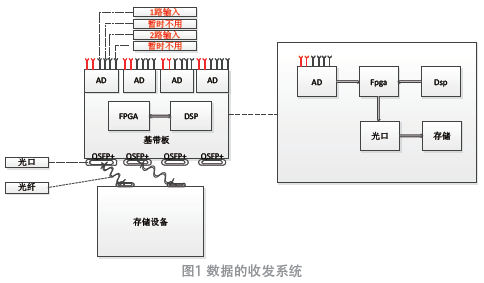

为了实现基带数据成功采集后的离线分析,采用FPGA 与DSP 互联功能把采集的数据经乒乓模式写入DSP,由DSP 随机取数进行离线分析,突破了高速信号不易实时分析的难题。毫米波的接收系统如图1 所示。

作者简介:袁行猛(1988—),男,工程师,研究方向:信号与信息处理。

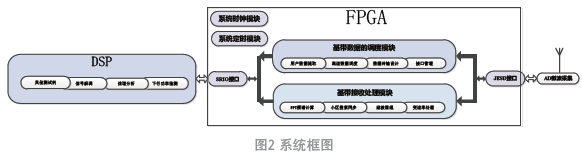

1 系统架构

基于乒乓切换的5G 毫米波基带数据传输系统如图2 所示,该系统实现了射频单元采集的毫米波数据到FPGA 的传输,高速数据经过处理缓存到DSP 中作为数据解析使用的数据通路。其中,数据采集部分使用高精度、高采样率AD 芯片,通过高速JESD 接口传输到FPGA 中,为了方便数据的处理与存取,要设计传输机制能正确存储数据的DSP。5G 毫米波的存储主要有两个难点;①高速数据接口设计:在收端,数据转换模块将高速采样的数据处理成指定速率的IQ 数据;②获取高速的IQ 数据后通过调度保证数据不丢失连续写入DSP 中。本次研究成功设计出高速接口交互与数据调度算法成功解决了这两个难题,并应用到测试仪表中。

2 5G物理层概述

物理层资源的灵活配置是5G 系统物理层资源的重要特征[2]。灵活的帧结构、时频资源的灵活配置以及灵活的时隙配置确保了5G 能满足不同业务需求,适应不同应用场景。

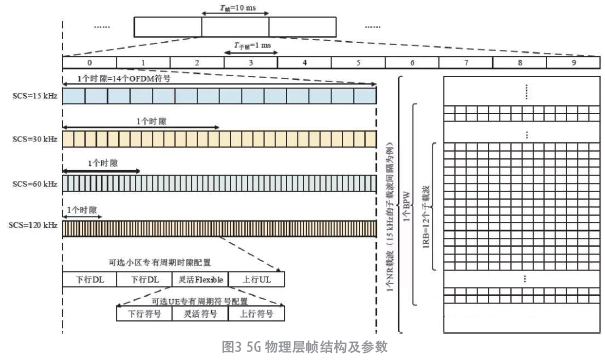

图3 为5G NR 的帧结构及相关参数。

在时域上,常规CP 下,每个时隙包含了14 个OFDM符号;在频域上,12 个子载波构成一个资源块(Resource Block,RB), 多个连续的RB 构成一个带宽部分(Bandwidth Part,BWP), 多个BWP 构成一个NR 载波。

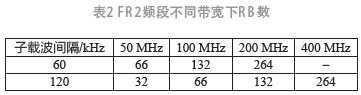

NR 支持从1 GHz到毫米波段范围的频谱,R15 中定义了两个频率范围(FR):FR1:450 MHz-6 GHz,通常指Sub-6 GHz,最大带宽为100 MHz;FR2:24.25 GHz-52.6 GHz,通常指毫米波,最大带宽为400 MHz。

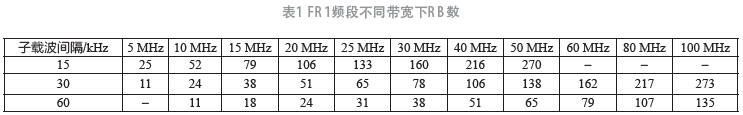

基于终端的能力,3GPP 限制单个小区有效子载波数不超过3 300(FFT 点数不超过4 096),因此不同子载波间隔情况下支持的小区最大带宽不一样,每种带宽配置下的最大RB 数如表1。

3 数据传输设计

由上节介绍可知,5G 毫米波的信号带宽已达400 MHz,对于接收来说,这需要前端射频具有较高采样率。本次设计采用491.52 MHz 采样率进行数据的采集[3]。根据5G 的参数集与帧格式可知,要想对5G信号进行分析解调需要至少10 ms 有效数据[4],因此10 ms 内的数据量已经达4 915 200 个IQ 数据,正常存取这么多数据,整个链路速率至少要15.7 Gb/s。设计中基带板的DSP 接口采用SRIO 口协议,有效速率只有16 bp/s,直接传输已接近理论最大值,很难保存连续有效的10 ms 数据。设计中采用射频与DSP 之间增加DDR4 作为缓存解决这一难题。

3.1 功能设计

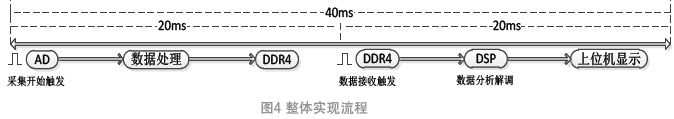

通过高采样率AD 板卡采集5G 毫米波段信号,全部在FPGA 中处理,连续采样的发端数据I、Q 各16 bit,组成32 bit 数据通路,对应的速率491.52 Mb/s线速率,此时的32 bit 位宽数据是一直有效数据,每10 ms 进行频谱与时域信号处理。紧接着每20 ms 乒乓切换模式,接收采样开始触发信号,开始从头采样数据,10 ms 数据持续不断地送入DDR4 中,DDR4 的速率最高可达1 Gb/s,速率完全可以满足存储需求,然后在下一个20 ms 对接收到的数据进行触发,并把10 ms 数据持续不断读出到DSP,此时读出速率可以降低,以满足SRIO 口速率要求;把数据连续读出到DSP,由DSP 进行部分毫米波数据分析解调,把解调结果通过网口传给上位机显示结果,具体实现流程如图4 示。

3.2 算法设计

1) 乒乓缓存

把整个信号分成40 ms,其中20 ms 作为信号采集和存储使用,另一个20 ms 作为信号的读取、分析以及传输解调结果使用,由此每40 ms 一个循环,其中每20 ms 作为乒乓切换功能使用,这里主要靠FPGA 产生定时采集与接收触发来控制整个实现流程。

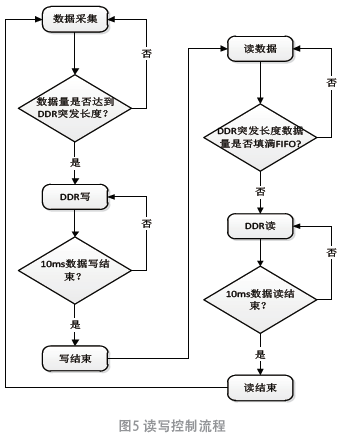

2) 数据流控制

我们考虑,由于数据采集速率很快,DDR4 的工作时钟很高,但DDR 读写操作时有突发长度的要求,所以分别设计时序控制,写操作之前放一个FIFO,要求其中数据量至少有突发长度时才往DDR 里面写。DDR 读操作时也同样设计对应的时序控制,由于DDR 读出时钟很快,一次读出数据量就是突发长度个数,这里同样设计一个FIFO,当FIFO 快达到自定义满标志时就停止从DDR 中读出数据,具体读写控制流程如图5 所示。

3) 在毫米波采集之后,需要进行数据的频谱与时域分析,数据速率为491.52 MHz,此时需要转化为122.88 MHz 采样率,在rx 端的数据处理之前进行4 倍抽取处理,这里采用2 个2 级半带抽取滤波器,处理过后的数据连续进行时频域分析。处理过的数据进行和有效数据的组合,本设计是放到10 ms 数据头位置,传给DSP 之后,由DSP 识别并取出。

4 仿真验证与实际应用

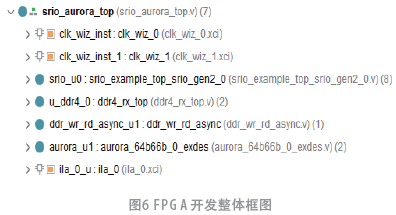

采用Vivado 2018.3 软件进行本次开发工作,开发的FPGA 芯片型号为xcku060-ffva1156-2-i,本次设计通过上基带板以及整个采集平台,最终验证本次设计的可行性。

图6 所示是设计的整体开发框架。

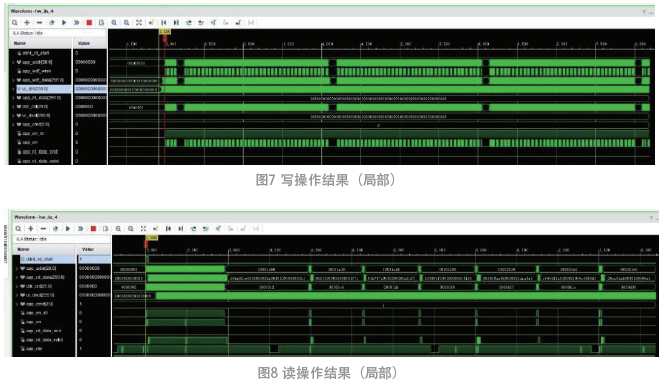

通过连接整机射频后实际采样,传输给DDR 后又读出到DSP 的时序图,图7 是DDR 写操作,图8 是上板后DDR 的读操作的真实结果。

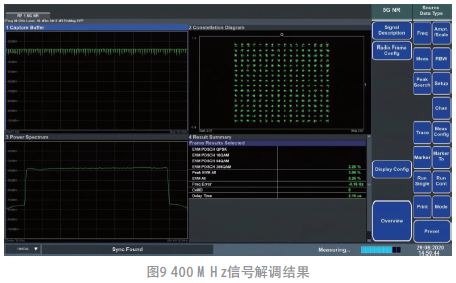

最后通过仿真传输给上位机显示,如图9 所示,5G毫米波波段,400M 带宽信号已经正常显示与解调,说明了设计的正确性。

通过仿真以及最终的显示结果可以发现,通过前端AD 采样后,经过本设计的传输机制,数据每40 ms 存取10 ms 有效信号,然后用20 ms 取数与分析,最终送到上位机显示,可以发现已经正常解调,从而说明设计的功能正常,满足5G 毫米波段400 MHz 信号的传输与解调。

5 结论

本研究完成了5G 毫米波基带数据的研究与实现功能。为了构建基带单元BBU和射频单元RFU 之间数据通路,需将具有较高采样率的5G 信号正常存取到DSP 用于分析解调。本设计主要研究开发了基于乒乓切换存取的机制、数据流控制机制,以及防止DDR 读取出错的预防机制。经过仿真和硬件验证了传输的正确性,确定了本研究的可行性。

参考文献:

[1] 何世文,黄永明,王海明,等.毫米波无线通信发展趋势及技术挑战[J].电信科学,2017(6):11-19.

[2] 张然.5G移动通信网络关键技术研究[J].信息与电脑:网络与通信技术,2018(3):168-169.

[3] 黄宇红,刘盛纲,杨光,等.5G高频系统关键技术及设计[M].北京:人民邮电出版社,2018.

[4] 欧洲电信标准协会IX-ETSI.5G;NR;Physical Layer;General Description(V15.0.0;3GPP TS 38.201 version 15.0.0 Release 15):ETSI TS 138 201-2018[S].2018.

[5] 同伟锋.基于DSP+FPGA的嵌入式视频采集系统的设计[D].西安:西安电子科技大学,2009.

(本文来源于《电子产品世界》杂志2021年4月期)

评论