功率因数校正最佳策略:如何选取合适的MOSFET?

导读:近年来,随着汽车、通信、能源、绿色工业等大量使用MOSFET的 行业的快速发展,功率MOSFET备受关注。MOSFET广泛使用在模拟电路与数字电路中,对于工业市场而言,较高的电流会增加系统中的能量损耗,举例对电力公司来说,这会导致输电过程中的过量浪费。而要达到完全相同的输出功率,功率因数较低的负载比功率因数较高的负载会消耗更多无功电流。所以,为功率因数校正应用,选择合适的MOSFET器件尤其重要。

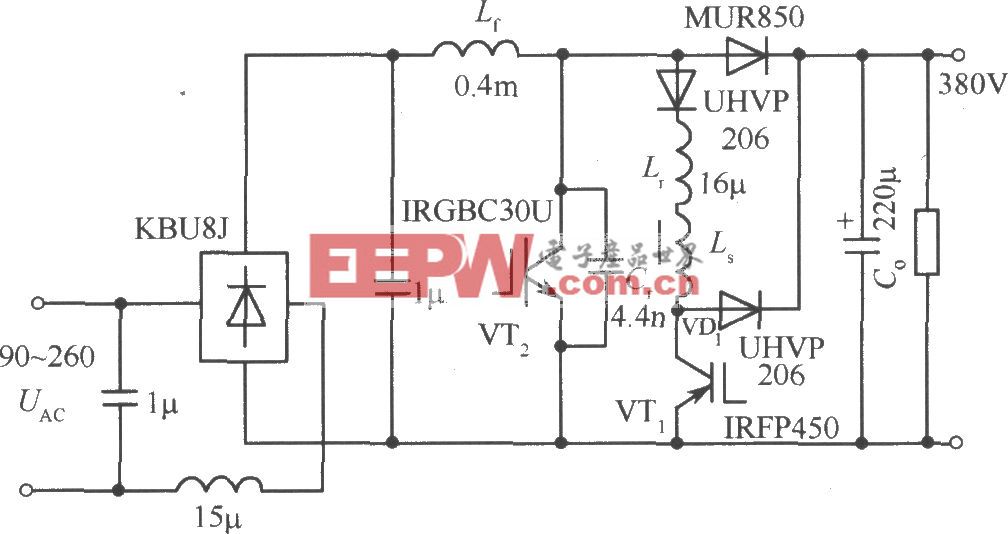

本文引用地址:https://www.eepw.com.cn/article/201710/369663.htm功率因数是实际功率(P = 瓦特)与视在功率(VA= 伏安)之比;目标是实现尽可能接近1的功率因数。要达到完全相同的输出功率,功率因数较低的负载比功率因数较高的负载会消耗更多无功电流。较高的电流会增加系统中的能量损耗,对电力公司来说,这会导致输电过程中的过量浪费。为此,对于输出功率为75 W或更高(依据EN61000-3-2标准)的任何电源,图1所示的功率因素校正 (PFC) 电路块都是一个重要而且常常是必不可少的子系统。PFC电路块用于使输入线电流与AC电压波形一致,且在大多数情况下将输出电压升高至标准的400 VDC。图2显示了PFC电路对线电流及其谐波电流的影响。

图1:PFC原理图

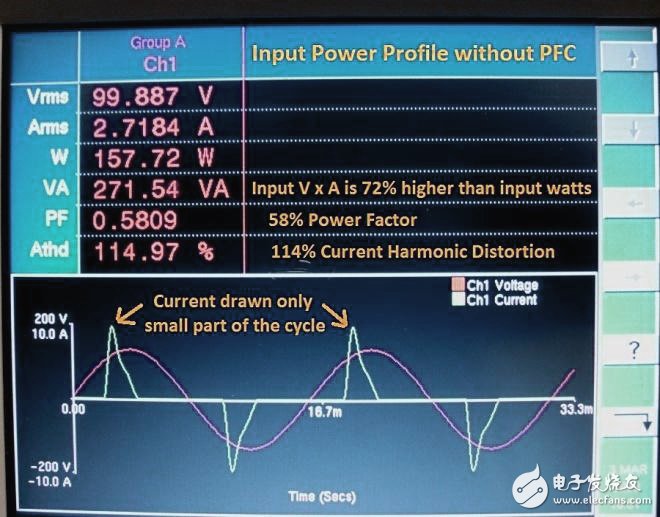

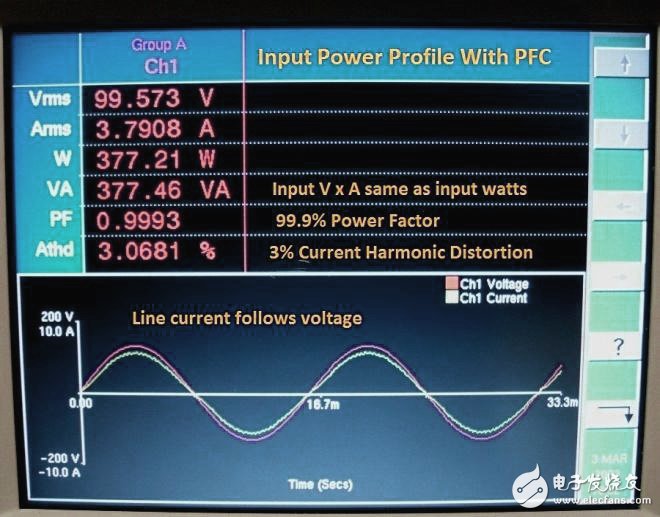

图2A:无PFC情况下的线电压及电流 图2B:有PFC情况下的波形

在图2A中,电流来自AC电源且只持续周期的较短时间。这导致较低的功率因数和115%的过量谐波电流。虽然系统只消耗158 W可用功率,但传输系统的相关值需要达到272 VA才能提供这一功率。图2B显示了使用相同输入功率曲线来实现PFC的优点。在功率因数为99.9%的情况下,谐波电流降至3%。电流来自AC线路且持续整个周期,同时也没有过量的VA浪费。

应当注意的是,PFC与谐波电流减少并非同义词。例如,在高电感性负载情况下,电流可能是滞后于电压的完美正弦曲线。因此其将具有较低的功率因数和高无功功率,且没有任何谐波电流。而谐波电流多的失真波形通常具有所有不良特性。PFC电路不仅能够校正功率因数,还有助于减少谐波电流。目前,关于电子设备功率质量有许多不同的标准。EN61000-3-2要求所有输入功率》 75 W的系统减少谐波电流。80 Plus电源认证要求功率因数达到0.9或更高。

在PFC电路中,MOSFET损耗约占总损耗的20%左右。通过选择正确的器件,PFC效率能够得到大幅提升。为PFC电路选择合适MOSFET器件的一种方法是使用针对特定应用的品质因数 (FOM),来最小化器件的总损耗。虽然FOM包括针对传导损耗的导通电阻值(RDS(on)) 和针对开关损耗的栅极电荷值 (Qg),但其并非二者的简单积。为了说明开关损耗,使用了该器件的Qgs和Qgd的一部分以及其输出电容值 (Coss)。

标准AC/DC电源的四个级是:

· 输入

· PFC前端

· 转换器

· 次级

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处!

为满足80 Plus“金级”效率标准的要求,所有级的合并损耗是额定输出功率的约12%。单纯PFC MOSFET损耗应限制到总输出功率的约2%或封装功率限值,(以二者中的较低者为准)。“TO”封装的最大功率损耗限值为:

· PowerPAK®SO-8L (5x6): 5W

· PowerPAK®8x8: 7W

· TO-220/TO-220F: 10 W

· TO-247: 20W

· Super TO-247/Tmax: 25W

因此,由传导损耗和开关损耗构成的最大封装功率限值不应超过上述水平。传导损耗用公式I2*R来计算,其中考虑到了器件的RDS(on)以及其温度系数。开关损耗不仅需要考虑Qg、Qgd和Qgs,还需要考虑Qoss,Qoss是Coss的积分函数。

传统的FOM,即RDS(on)(典型值)*Qg(典型值)并不考虑器件的Coss/Qoss,但这是一个非常重要的损耗,特别是在开关损耗大于传导损耗的轻负载情况下。开关损耗的这一成分是在充电(当器件断电时)和放电(当器件通电时)情况下产生的,必需在设计中加以考虑。Coss/Qoss越大,开关损耗就越大。此外,Qoss损耗是固定的并且独立于负载,这一点可从标准公式Poss = ½ CV2 x Fsw中看出,其中Fsw是开关频率。

在通用输入电源中,PFC MOSFET始终受到380 VDC至400 VDC的主体 (bulk) DC总线电压的限制。因此,输出开关损耗有可能在总损耗中占相当大的比例。高压MOSFET (HVM)的Coss随着所施加的VDS的不同而有相当大的变化。为说明输出电容器的非线性,可以使用Poss = ½ Coer x V2 x Fsw作为损耗计算公式。Coer是由产品说明书提供的有效电容,与MOSFET的集成Coss具有相同的存储能量和相同的损耗。所以,新FOM现在为Rds(on)(典型值) * (Qswitch (典型值) + Qoss),其中Qswitch是Qgd和Qgs的组合。

例如,我们使用一个最大封装功率损耗为8 W且对传导损耗和开关损耗的贡献各为4 W的TO-220 / TO-220F器件。这样Coss/Qoss损耗将占到总封装损耗的约20%,或总开关损耗的约40%,这是标准FOM公式没有加以考虑的一个较大损耗。

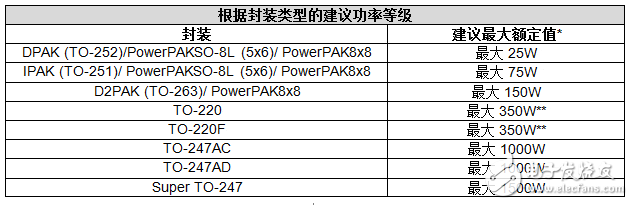

由于有许多可用封装选项,所以表1列出了针对不同封装的最大功率额定值。请注意,每种封装都有一系列器件可供选用,所以有可能对广泛的输出功率推荐相同的封装。为了实现SMT封装(如PowerPAK®SO-8L (5x6) 和PowerPAK®8x8)的最大可能功率耗散,有必要将PCB温度保持在最坏条件下的应用要求值。建议最大额定值因此受到系统热考虑事项而非封装损耗的限制。

表1:各封装类型下的最大功率级

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处!

评论