以太网供电浪涌保护电路设计方案详解

设计一款电子电路或定义一个完整系统时,确定这些应力源,并正确理解它们的机制以正确定义操作系统的环境是非常重要的。这样做可以使您定义简单的设计规则,并利用低成本的解决方案对敏感的电子系统进行充分有效的保护。以太网供电 (PoE) 设备是一种必须对敏感电源电路进行保护的系统。尽管 PoE 规范提供了过电流保护功能,但对那些会损害其他类型电源设备的电气瞬态来说,这些系统也很易遭受同样的损害。

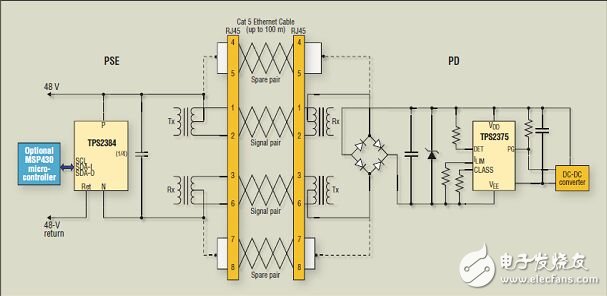

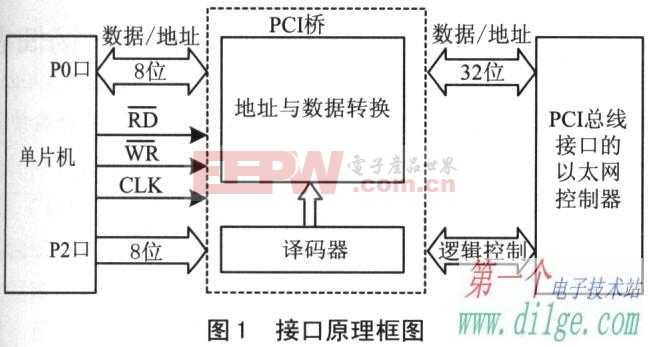

本文引用地址:https://www.eepw.com.cn/article/201710/369346.htm在 PoE 设备中,供电设备 (PSE) 将电源通过以太网线缆供应到用电设备 (PD) 中。如图 所示,通过以太网线缆数据通道所用的两条双绞线对的共模电压差进行供电。通过使用额外的备用双绞线对,可以提供更多的电力。PoE 的应用范围很广,其中包括办公和工业网络等环境。以太网线缆或设备通常为室内使用,但是也可以用于室外应用。

在本单端口 PoE 应用例子中,通过以太网线缆的信号对实现了电源供电;而通过备用双绞线对实现了更多电力供应。

PoE 应用中的瞬态

当前已开发了许多标准,对不同应用中的瞬态过压环境进行模拟或仿真。例如,根据 IEC 瞬态抗扰度标准,瞬态可以分为以下三大类: IEC 61000-4-2:静电放电 (ESD); IEC 61000-4-4:电气快速瞬态/脉冲群 (EFT); IEC 61000-4-5:浪涌。这些 IEC 标准也定义了应用于每一瞬态类别的抗扰度测试方法,并且它们还向瞬态抑制组件的厂家提供了一些符合特定组件特征的标准化波形和过电压电平。

静电放电 (ESD)

ESD 是由两种绝缘材料接触、分开而引起的电荷累加造成的;当带电体接近另一个电位较低的物体时,就会引起相应的能量释放。例如,当人走过地毯时,就可以产生超过 1.5kV 的电荷。 ESD 是一种共模电气事件,并且是通过电气路径,从一个元件到另一个元件的放电现象,最后以外壳接地结束。清楚地确定电流路径,并确保其对敏感电路不会造成损害是一项很重要的设计指南。一个更好的选项就是为放电电流提供一个替代放电路径,以绕过该敏感电路。

表 1、IEC 61000-4-2 波形参数。

另一个威胁因素是线缆放电事件。当以太网线缆充电,并放电到与该线缆相连的一个电路中时,就会发生线缆放电事件。线缆也能通过摩擦带电(例如,将线缆在地毯上拖曳)或通过感应(例如,来自持有线缆的带电人体)的方式进行充电。目前还未确定用特定的测试方法来定义线缆放电的标准。绝大多数的厂商都使用内部线缆放电事件 (CDE) 对设备 (setup) 进行测试以对他们的设计进行评估。极少数人认为只要通过 IEC 等级 4 测试,就已足够对此类放电进行保护了。

不过,那种认为只要设备通过 IEC 61000-4-2 等级 4 放电测试,就可以通过 CDE 测试的看法,之所以不是不变的真理,是因为两个测试中所用的带电电容有很大区别,即 IEC ESD 为 150 pF,而 CDE 的电容则要大的多,这取决于所用线缆长度以及线缆相对地面的高度。在集中式电容 (lumped capacitance) 之外,也有来自传输线路的分布式电容。CDE 中的放电通常会比 IEC 等级 4 中的放电释放更多的能量到所测设备中。

电气快速瞬态

一次电气快速瞬态 (EFT) 是开关和继电器、马达以及其他感应负载电弧接触的结果,这在工业环境中是很常见的。通常,该类型的瞬态是共模型的,并通过电容耦合引入通信线缆中。 IEC61000-4-4 将该瞬态定义为一系列非常短的高压尖峰,以 5kHz 到 100kHz 的频率出现。表 2 归纳了严重性测试等级。短路电流值通过用 50-Ω 电源阻抗对开路电压分压进行估算。

表 2、IEC 61000-4-4 严重性测试等级。

根据 IEC61000-4-4,通信线缆上的容性耦合钳是对通信端口的测试电压进行耦合的首选方法。其中包括一根以太网线缆,这意味着耦合不会产生到端口的任何电偶连接。另一个可行的耦合方法是直接通过 100-pF 的离散电容进行耦合。我们应注意到,由于它的重复特性,EFT 事件还可以造成通信系统的不稳定行为。

瞬态保护电路指南

保护电路不应干扰受保护电路的正常行为,此外,其还必须防止任何电压瞬态造成整个系统的重复性或非重复性的不稳定行为。为满足这些要求,我们为电子系统的电压瞬态保护设计规定了许多设计指南,瞬态电压源可以分为差分型、共模型,或差分和共模合一型。瞬态电压保护技术可分为屏蔽和接地、过滤、电气隔离以及使用诸如二极管的非线性器件等类型。阻断和转移 (diverTIng) 技术的结合使用实现了有效的电路保护。使用共模线圈可能是非常有必要的,但是所选的电压抑制器的设计还必须符合应用的速度和稳健性要求。例如,必须对有低ESR的高电压(高于或等于 2kV)使用能吸收直接瞬态冲击的分路(线路对大地接地)电容器。

PoE电路保护

尽管在本文中讨论的仅是通常在受保护设备内部署的二次侧保护,但我们应注意到,对于室外电信光缆来说,要求有一次侧电信保护设备。

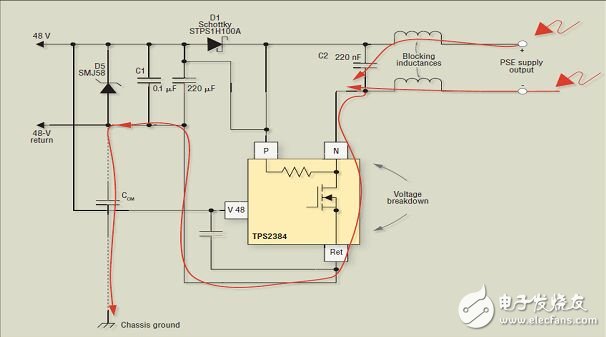

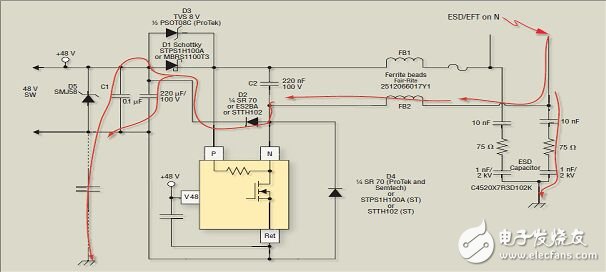

在PoE 应用中,PSE 是由 48-V 电源供电的。通常,PSE 会有一些与大地接地相连的共模电容。这些电容可以是离散电容,也可以是 PCB 板的层间电容,或两类电容的结合。由于 PSE 实际上并不是浮动的,因此施加于数据连接器上的任何共模电压瞬态都能造成 PSE 组件的电压击穿。对于 PSE 端口电源开关晶体管来说,尤其如此。图 2 显示了该效应,并显示了在没有保护电路时,造成对 PSE 电源开关晶体管损坏的大电流路径。CCM 表示系统的 48-V 线路与外壳接地之间的共模电容。这可以是 48-V 电源的正或负(48-V回路)线路。为简化原理图,仅在负极线路显示了 CCM。该配置适用于使用 AC 断接电路时的应用,该配置还要求使用 D1。AC 断接电路的工作会导致瞬态保护出现最坏的情况。

图 2、若没有保护电路,一次 ESD 或 EFT 事件就可以毁坏 PSE 的主电源开关。

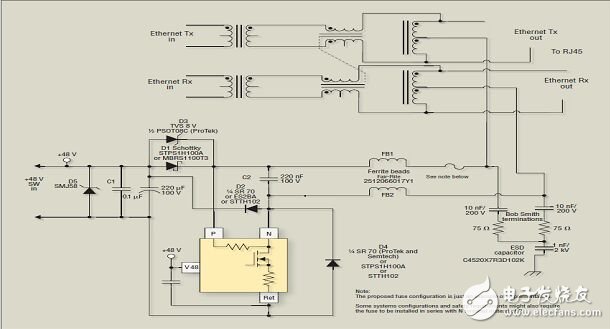

在使用 RJ-45 线缆的应用中,通常不会使用先前提到的线缆屏蔽保护技术。不过,图 3 中显示的解决方案对 PSE 集成电路实施了充分的保护。当使用 AC 断接电路时可采用该电路,若没有使用该电路,则不需要 D1 和 D3。

图 3、该保护电路配合使用阻断元件(电感器)和转移电路(BS 终端和钳位二极管)避免了 ESD 和 EFT 事件产生的浪涌损害。

关键组件的参数

认真考虑以下保护电路中的每一个主要组件的关键参数是非常重要的。对于钳位二极管 D2 和 D4 而言,关键参数是指前向恢复时间、瞬态电流能力以及前向电压瞬态。TVS 二极管 D3 的关键参数是响应时间、电流处理能力以及低阻抗。只有当 D1 用于 AC 断接功能时,才要求 D3。

若考虑到更为严重的浪涌问题,比如 GR-1089-CORE 标准(楼宇间的雷电浪涌设计规范)中定义的浪涌,则 D2、D3(1500-W TVS)以及 D4 需要使用更为稳健的组件。负电压瞬态要求有肖特基二极管 D1,同时也需要Bob Smith (BS) 终端或线路对接地电容器,因为最初的 ESD/EFT 瞬态是通过这些终端流向大地接地的。其他的主要组件是铁氧体磁珠 FB1 和 FB2。这些组件提供了防止 C2 在高频率时将终端短路的阻断阻抗。48-V 总线 (100nF) 上的去耦电容器以及桥接 TPS2384 的 P 与 N 终端的电容器必须是低阻抗陶瓷电容器。C1 和 C2 必须非常靠近钳位二极管 D1 和 D2。48-V 总线 (D5) 上的 TVS 二极管通常的放置位置与 48-V 输入连接器靠得很近。所有的器件都必须是表面贴装封装形式的,并带有很低的寄生电感。

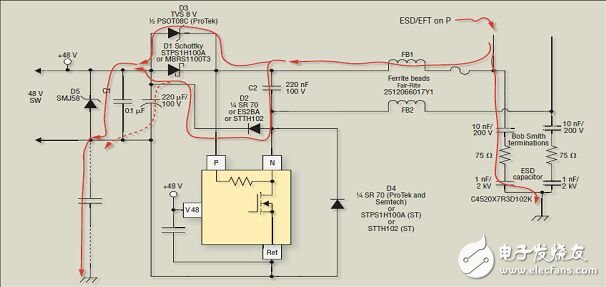

不管极性为正还是为负,保护组件均可避免瞬态电流进入 TPS2384 芯片的 N 到 RTN 路径,或 P 到 RTN 路径。不过,这些瞬态电流由于瞬态源的不同,可能会有不同的路径。图 4 和图 5 分别阐明了快速共模事件 ESD 或 EFT 的保护情况。

图 4、本图阐明了铁氧体磁珠和钳位二极管将正极ESD/EFT事件从TPS2384 芯片的P终端转移到底座接地的电流路径

在瞬态事件发生前,C1 和 C2 上的直流电压电平直接影响瞬态电流路径。在 ESD 或 EFT 模拟中,BS 终端与铁氧体磁珠一起在 ESD/EFT 抑制中发挥作用。此外,BS 终端还可用于 EMC 目的。这些电容器清楚地定义了 ESD 或 EFT 冲击时的最初路径。

图 5、本图阐明了铁氧体磁珠和钳位二极管将正极ESD/EFT事件从 TPS2384 芯片的 N 终端转移到底座接地的电流路径。

模拟可以提供在不同瞬态事件中可能的电压大小的指示功能。线路对大地接地电容器上的最大可能电压是 1kV,这表明选择额定值为 2kV 的电容器是安全的。模拟还表明,应用 8-kV ESD 时,若同时存在 150-pF/330-HHM,则 BS 终端上 1-nF 电容器的电压将小于 100V。对于Class 2 事件来说,在浪涌测试中,施加到该电容器的最高电压是 1kV。同理,对于 10-nF 的电容器来说,200-V 的额定值也是安全的。不过,因为没有定义一个 ESD 线缆放电模型,因此还没有进行过此类模拟。对于四端口的 PSE 来说,图 6 显示了一款推荐使用的电路板布局,其符合先前所述的所有设计指南。

图 6、PSE PCB 板的设计遵循了提高电子系统稳健性的布局指南,以提高 ESD/EFT 事件保护能力。

很明显,D2、D4、D3、D1、C1、C2以及电源输入和 RJ-45 连接器必须靠得非常近,以使瞬态电流回路所占空间以及其生成的阻抗尽可能的小。在多端口应用中,推荐对每一组的两个或四个端口使用与 C1 一样的去耦电容器,并使每个电容的放置都靠近其相关组。为抑制器器件提供足够的铜箔面积以促进散热也是非常重要的。另外一个注意事项是以太网接口电路通常要求数据线路驱动电路要有数据线路保护器。不过,本文的重点是阐述用于 PoE 电路的保护技术。

----------------------------------------

智能家电技术资料集锦——让家电设计迈入崭新时代!

评论