以太网收发电路设计方案详解

以太网收发电路由RJ45接口、耦合变压器、以太网收发器,以及收发器与调制驱动电路、接收解调电路之间的接口组成。其中以太网收发器是核心单元,直接决定了系统的工作性能。以太网收发器IP113IP113是二端口10/100Mbps以太网集成交换器,由一个二端口交换控制器和两个以太网快速收发器组成。每个收发器都遵守IEEE802.3、IEEE802.3μ、IEEE802.3x规则。为帧缓冲保留了 SSRAM,可以存储1K字节的MAC地址,全数字自适应调整和时序恢复,基线漂移校正,工作在10/100baseTX 和100baseFX的全双工/半双工方式。使用2.5V单电源,25MHz单时钟源,0.25μm工艺,128脚PQFP封装。

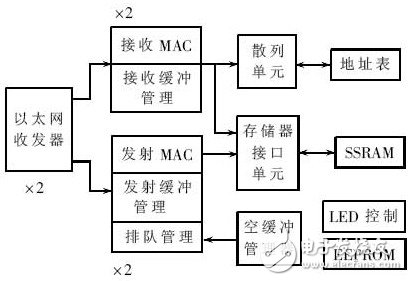

本文引用地址:https://www.eepw.com.cn/article/201710/369341.htmPort1的速率是自适应调整的结果,因而不需要外加存储器以缓冲数据包。每个端口都有自己的接收缓冲管理、发射缓冲管理、发射排队管理、发射MAC和接收MAC。各个端口共享一个散列单元、一个存储器接口单元、一个空缓冲管理器和一个地址表。

图2 IP 113内部原理框图

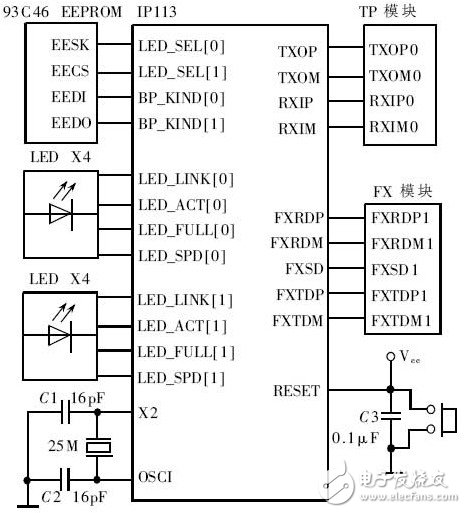

主要由以太网收发芯片IP113、专用配置芯片EEPROM 93C46、LED显示矩阵,以及IP113的Port1与TP模块、Port2与FX模块之间的接口组成。 IP113支持很多功能,通过设置适当的参数满足不同的需要,既可以由特定的管脚设定,也可以用EEPROM配置。为提高系统的整体性能,这里采用专用串行EEP ROM 93C46芯片。系统复位时,管脚LED_SEL[1:0]分别作为93C46的时钟EESK和片选EECS,BP_KIND[1:0]分别作为 93C46地址EEDI和数据输出EEDO,将93C46内部的参数读入IP113内部的寄存器。复位结束后,这些管脚均变成输入信号,以使IP113脱离93C46而独立工作。

图3 以太网收发电路

复位时,IP113首先读取93C46的00H中的内容,只有00H[15:0]=55AAH时,才会继续从EEPROM中读取参数,否则以缺省值或特定的管脚电平值设置工作寄存器。01H中的值设置LED输出控制寄存器,控制两个LED矩阵的亮、灭和闪烁,以分别显示两个端口的连接、活动、全/半双工和速率(10Mbps/100Mbps)。02H中的值设置交换控制寄存器1,选择系统的流控制方式和冲突保护。03H中的值设置交换控制寄存器2,控制系统的丢包、地址失效、优先级和算法补偿。04H中的值设置收发器控制寄存器,其中04H[13:11]的5 种取值:000、100、101、110和111,分别对应收发器的5种工作状态:NWAY、10Mbps(半双工)、10Mbps(全、半双工)、 100Mbps(半双工)和100Mbps(全、半双工)。05H~0AH中的值分别设置收发器确认寄存器、测试寄存器和验证方式寄存器。

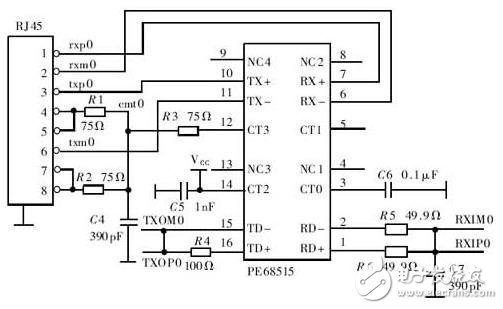

Port1的TXOP和TXOM是TP发射数据对,RXIP和RXIM是TP接收数据对。图4的TP模块电路中,RJ45接口将MLT-3码流以太网信号经过耦合脉冲变压器PE68515变为单极性信号。

图4 IP模块电路图

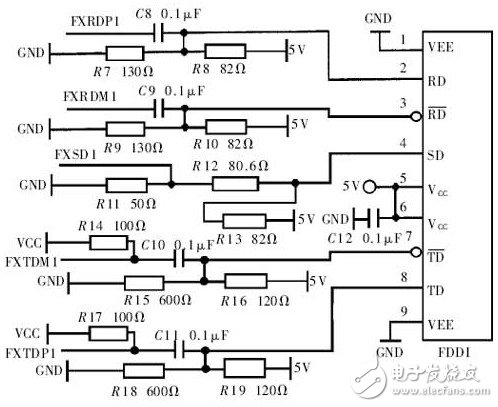

Port2的FXRDP和FXRDM是FX的接收数据对,FXTDP和FXTDM是FX的发射数据对。FXSD是光电检测信号,当接收到的光信号经光电转换后电平低于1.2V时,FXSD输出连续的PECL电平。图5是FX模块的电路图,电路中采用标准的FDDI数据接口。由于调制驱动和接收解调电路采用5V电源,而系统其它部分均使用2.5V电源,FDDI中的信号均是PECL电平,因此必须经电平转换(如图5所示),才能把这两部分联系起来。

图5 FX模块电路图

----------------------------------------

智能家电技术资料集锦——让家电设计迈入崭新时代!

评论