在FPGA开发中尽量避免全局复位的使用?(2)

在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。如果所有的触发器都使用这一全局复位信号,则GSR信号将形成一个高扇出的网络(有兴趣的朋友可以在综合工具中查看)。虽然在启动顺序中,它可以与一个用户自定义的时钟进行同步,但是想让它与设计中的所有时钟信号进行同步是不可能的;比如,一个Xilinx FPGA中可能含有多个DLL/DCM/PLL时钟处理模块,每个模块又可以产生多个时钟信号,在各个模块内部进行时钟信号的同步是可行的,然而想让所有时钟信号同步是完全不可行的——从DCM的分布上就可以看出来:中间相隔的长距离布线对高频时钟信号的延时显著增大,进行同步自然无法做到。于是,在时钟信号频率越来越高的情况下,全局复位信号便开始成为时序关键。解释如下:

本文引用地址:https://www.eepw.com.cn/article/201710/365660.htm

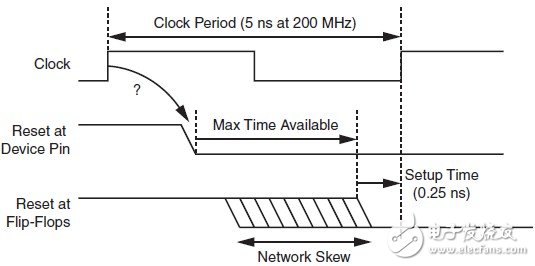

图1被两个时钟信号的边沿截断的复位信号的时序图

关键词:

FPGA

相关推荐

-

-

sandman555 | 2005-02-05

-

sandman555 | 2005-02-05

-

xiaohua | 2002-09-24

-

-

-

sandman555 | 2005-02-05

-

-

-

-

-

herbertwj | 2004-08-15

-

-

评论