设计心得:用FPGA打造最强网络防火墙系统,小心避过这些坑

项目背景及可行性分析

- 项目名称、项目的主要内容及目前的进展情况

基于FPGA的防火墙系统设计。基于FPGA平台,设计一个具有防火墙功能的系统,具备对进出网络数据包解析、过滤等功能。目前正处于总体设计与论证阶段。

- 项目关键技术及创新点的论述;

关键技术有并行运算,状态检测,CAM,规则匹配,及PowerPC嵌入式系统。本项目的创新点是将传统的软件防火墙系统移植到硬件平台,充分利用FPGA的优势,软硬件相结合,提高处理速度和性能。

- 技术成熟性和可靠性论述:

硬件防火墙开发模式就国内来说主要存在三类。一类是通过网络处理器(网络芯片), 一类是通过专用的FPGA编程,第三类是设计专用的ASIC芯片。相对于各种网络处理器,FPGA是设计ASIC芯片最重要的步骤之一。基于FPGA芯片的片上防火墙系统优势。框架结构灵活高效。开发者针对防火墙产品需求,有针对性定义数据通路、缓存单元、处理单元、内存总线、总线仲裁单元及其耦合构架,使之达到最优性能。数据线速处理。精心设计的框架结构,使得FPGA芯片的天然并行处理优势发挥到极致。数据在芯片内始终处于流动状态,多个处理单元在不同节点并行完成数据分析、处理、替换等操作,从原理上保证了数据线速处理。硬件可升级。最终产品保留FPGA芯片升级接口,随着网络应用环境与用户需求变化,更新芯片设计后,为用户提供硬件升级服务,最大程度保护用户投资。开发优势。所有功能集成在片内完成, 兼之FPGA I/O资源丰富特性,使得系统硬件布局极为简单,将网卡芯片、内存芯片与时钟直接与FPGA芯片连接即可,省却了传统主板繁杂的控制器、总线等结构,使得系统成本大幅下降。加之在FPGA中嵌入PowerPC硬核,使得片上系统的性能进一步提升。

项目实施方案

1.方案基本功能框图及描述

用框图的方式并加以简单的描述简述实施本项目的技术方案。

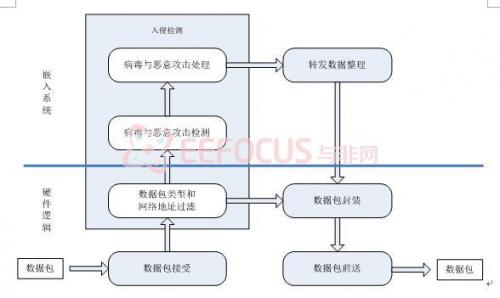

图1 方案基本功能流程框图

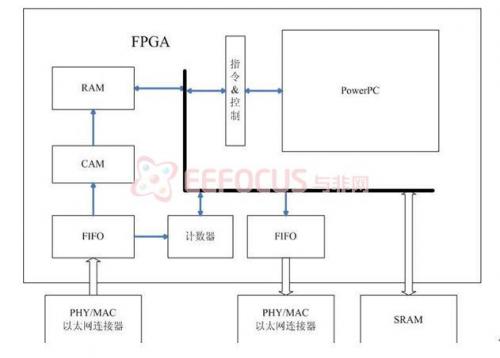

图2 系统结构框图

该方案采用FPGA硬件逻辑和嵌入系统的两层分层结构,如图1所示。

FPGA硬件逻辑及外围硬件主要实现的功能是:数据包收发、五元组(协议类型、源/目的IP地址、源/目的端口号)的数据分类以及固定字段模式匹配、转发数据的封装。

嵌入式系统实现的主要功能是:病毒与恶意攻击的检测、病毒与恶意攻击的处理、过滤规则管理、转发数据整理。

方案的核心部分是由实现入侵检测的三个模块组成。利用硬件匹配和数据负载匹配认别病毒和恶意攻击,为网络提供安全保护。

2.需要的开发平台

实现本方案所需要的基本功能、功能、接口,FPGA,PowerPC,双网口(一个采用开发板上的网口,另需一网络扩展板),SRAM,

所需要的目标FPGA开发平台,简述为什么需要此平台

高级板-Virtex-2 Pro

是否需要其它配套的开发工具

配套的下载,调试工具

2.方案实施过程中需要开发的模块

在本方案中需要研制、开发的功能主要模块,以及开发的方式

见图1、图2所示

3.系统最终要达到的性能指标

论述本项目最终完成时所设想达到的目标。

实现一个具有防火墙功能的系统。

需要的其它资源

1.设计输入输出功能子板

子板功能描述、接口说明、时间、方式

网络扩展板,RJ45,2007年10月

2.测试设备

列出在方案实施过程中所需要的测试设备

万用表、示波器、频谱仪、逻辑分析仪等

3.方针、开发工具

列出在方案实施过程中所需要的仿真、开发工具等。

ModelSim、Xilinx ISE,Sinffer

评论