FPGA设计中的功耗

随着FPGA的密度越来越高,设计者们正在节能降耗方面取得越来越多的进展。出现降低功耗这一趋势的另一个原因是FPGA正在越来越广泛地应用于智能手机、媒体播放器、游戏机、卫星导航设备以及数码相机/摄像机等便携式设备当中。对于消费电子设备以及医疗、工业,甚至军事设备来说,功耗也许算是选择FPGA时最重要的因素了。系统可靠性的提高和易升级性也是需要考虑的重要因素。选择过程中的其他标准还包括成本、容量、性能、功能、功率和封装等。

本文引用地址:https://www.eepw.com.cn/article/201706/349338.htm基于FPGA的系统设计有4个主要的功耗组成部分:

浪涌功耗

配置功耗

编程后静态功耗

动态功耗

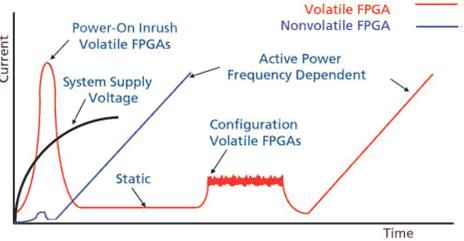

FPGA器件的功耗组成和降耗技术由于器件所采用的根本技术的差异而有所不同,比如有SRAM、混合SRAM、Flash和抗熔FPGA技术等。基于SRAM的FPGA器件包含了所有四个主要功耗组成部分,而具有非易失性的Flash和抗熔FPGA则只有两个主要的功耗组成部分(静态和动态功耗)。

浪涌功耗——当基于SRAM的FPGA通电时,就会引起电流尖峰,这是因为易失性SRAM晶体管最初的逻辑状态不确定。这种电流就是浪涌电流,并且为数百毫安级。基于Flash的FPGA由于采用了“上电即写入(LAPU)”的配置方式,因此浪涌功耗非常小。

配置功耗——配置功耗发生在SRAM FPGA写入程序的时候,这个时候系统加电启动并从flash或者EEPROM存储器中下载比特流数据。通常配置时间为几百毫秒,并且电流强度为数百毫安。

后编程静态功耗——该功耗是由于FPGA上大量的晶体管在器件没有进行任何工作时也会出现少量的漏电流。这种漏电流在采用深亚微米技术制造的器件中占到了功耗量的很大一部分。而基于Flash的FPGA不需要任何“保持电流”来维持配置数据,因此与其他任何类型的FPGA相比,其静态功耗都是最低的。

动态功耗——该功耗是器件正在工作的时候逻辑单元的开关电流引起的。动态功耗与工作电压和开关频率成正比。

FPGA节能技巧

选择基于Flash的FPGA,因为它是真正的单芯片解决方案,无需配置支持,不存在浪涌功耗,而且静态功耗低。

选择具有低功耗模式的FPGA,也称为睡眠模式,在该模式下时钟服务电路处于关闭状态,而且I/O被禁用,同时器件状态保持不变。这就极大地降低了静态功耗。

系统时钟频率对于FPGA器件的总体功耗有巨大的影响。时钟频率与带宽性能有直接的关系,但是为了在功耗和吞吐量之间实现最佳的平衡,可以为不需要快速时钟的元件提供一个较慢的始终频率。对于那些与带宽密切相关的元件,则提供更快的时钟频率。

图:易失性存储器FPGA与非易失性存储器FPGA功耗曲线图

评论