基于FPGA的电子摄像系统的稳像设计

电子摄像系统已广泛应用于军用及民用测绘系统中,但是效果受到其载体不同时刻姿态变化或震动的影响。当工作环境比较恶劣,尤其是在航空或野外操作时,支撑摄像机平台的震动会引起图像画面的抖动,令观察者视觉疲劳,从面产生漏警和虚警。所以在运行中,如何稳像成为十分重要的问题,特别是在长焦距、高分辨力的监视跟踪系统中更加突出。具璞蒿、实性性强、体积小巧等特点,得到更广泛的应用。

稳像系统的反应速度是电子稳像要解决的关键技术之一。传统的基于“摄像机-图像采集卡-计算机”模式的稳像系统、图像检测和匹配算法全部由计算机以软件方式实现。尽管当今计算机的性能很高,能够部分满足单传感器电子稳系统的实时处理要求,但在以下几个方面有着难以解决的问题:首先,其固有的串行工作方式使得单计算机难以适应其于多传感器视频处理系统的实时稳像,阻碍了在实际中的应用adw欠,传统的图像采集卡中能将采集图像数据实时传输给计算机,而不能传输给标准接口的视频监视设备lk之很多应用场合对听要求很高。因此,研制专用的电子稳像平台,既能实时地高速获取视频数据,又能将数据实时地传后续的图像处理系统,既有实际意义又有工程价值。

1 系统涉及的关键技术

摄像头输入的PAL制式电视信号首先通过视频处理接口完成对其解码、同步和数字化的工作,数字化后的图像信息进入到由FPGA实现的帧存控制器中,完成数据的交换(数据的缓冲),同时完成系统要求的去隔行和放大的操作,最后处理好的数据通过VGA控制器,完成时序变化,经视频、A变为模拟信号送到VGA监视器上实时显示。

1.1 视频处理接口

由于在进行视频处理时,多为从摄像头输入模拟信号,如NTSC或PAL制式电视信号,除图像信号外,还包括行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号等。因而对视频信号进行A/D转换的电路也非常复杂。Philips公司将这些转换电路集成到了一块芯片中,从而生产出功能强大的视频输入处理芯片SAA7111,为视频信号的数字化应用提供了极大的方便。

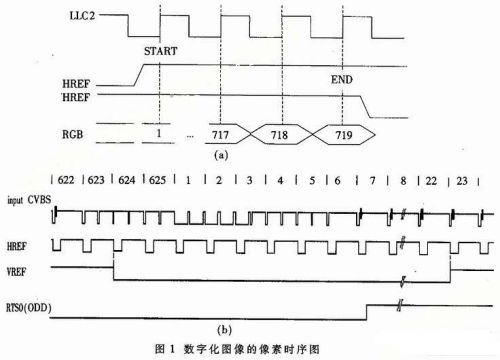

系统设计采用SAA7111对复合信号进行采样、同步产生、亮色分离并输出标准的数字化信号。SAA7111输出的数字化图像信息符合CCIR.601建议,PAL制式的模拟信号数字化后的图像分辨率为720×572,像素时钟13.5MHz。在本稳像系统中要求图像输出符合VGA(640×480,60Hz)标准,因此在采集数据时要对数据进行选择,避开行、场消隐信号和部分有效像素信息,在较大的图像中截取所需要的大小。SAA7111向帧存控制电路输出像素时钟(LCC2)、水平参数(HREF)、垂直参考(VREF)、奇偶场标志信号(ODD)和16位像素信息(RGB565).其中LCC2用来同步整个采集系统;HREF高电平有效,对应一行720个有效像素;VREF高电平有效,对应一场信号中的286个有效行;ODD=1时,标志当前场为奇数场;ODD=0时,标志当前场为偶数场。采用16位RGB表示每个像素的彩色信息。图1(a)为数字化图像中的一行像素的时序图。其中两个HREF分别表示有效行的起始与结束位置,实际为一个信号;可以清楚地看到一行中有效的720个像素与像素时钟LLC2的对应关系,在采集时通过帧存器控制电路选择其中部的640个像素进行采集。图1(b)为一帧数字图像的输出时序图。可以看到在第*~22行时,VREF处于无效状态,因此在后续的采集中,这部分的信息不予处理并通过ODD的电平区分奇偶场数据。

1.2 去隔行支持

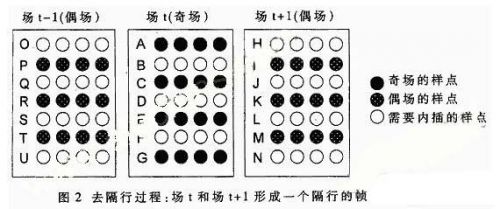

PAL制电视信号采用隔行扫描机制,采用人眼的视觉暂留来实现两场1/50s扫描312.5行的图像构成625行(一帧)图像。而标准的VGA显示模式采用逐行扫描方式,在一个扫描周期内实现对图像的完全扫描。因此需要对视频信号进行去隔行处理。视频信号在经过缓冲后,按照取样时钟把经过模数转换的数字信号送入存储器缓存,通过数据内插的方法进行数据扩展,即相邻行之间按照一定的算法进行加权,从而得到内插行的数据,再以适当的速度读取处理后的数据,即可实现倍行频/倍场频的扫描。倍行频扫描可以消除行间的闪烁现象,倍场频扫描虽然行扫描频率不变,但是场频加倍,即能消除行间闪烁现象,还可以消除场间的大面积闪烁。去隔行问题的实质就是在每一场中填补被跳过的那些行,其过程如图2所示。

实际上为实现去隔行已经提出了很多简单的滤波器。一种选择是用同一场中的垂直内插值,这是个一维二倍上转换的问题。理想的垂直滤波器是一个半带低通滤波器。然而,这个滤波器要求无限长度冲击响应是不可实现的。实际应用中使用的是短得多的滤波器。最简单的是行平均,它用丢失行的上一行和下一行的平均来估计该丢失行。在图2中,对于第t场,D=(C+E)/2。由于没有使用时域滤波,所以它沿时间频率轴具有全通特性。为了改进性能,另一种选择是使用更长的垂直内插滤波器,其频率响应更接近理想的半带低通滤波器。对于第t场的行,满意的内插方法是D=(A+7C+7E+G)/16。以上两种方法都是只用了垂直内插。一种替代方法是使用时间内插。值得注意的是,对于一场中每个丢失行,在同一帧的另一场中有一个对应行。一个简单的时间内插方案是复制此对应行,即D=K,J=C。这种方法称为场合并。因为每一个去隔行帧都由合并两场获得,但是这两场的时间内插是相反的(对于某些特殊图案可能会产生视觉人为失真)。由于只在时间方向上进行了滤波,因此在垂直方向上是全通的。

为了改进性能,可以使用一种对称的滤波器,例如,对前一场和后一场中的对应行去平均以获得当前场中丢失的行,即D=(K+R)/2。这种方法称为场平均。然而这种办法内插任何一场需要涉及三个场,需要两帧存储器。与场合并的方法相比,在存储器容量和延时上有不可忽视的增加。为了在时间和空间人为失真方面达到折衷,较好的方法是既用垂直内插也用时间内插。例如,通过对同一场中上一个和下一个像素以及前一场和后一场取平均进行内插的办法得到一个丢失的像素。综上所述,当成像的景物在相邻两场之间静止时,在奇数场中丢失的偶行数应该与前一个和后一个偶场中对应的偶数行完全一样。因此时间内插将产生精确的估计。另一方面,当景物中存在运动时,相邻场中对应行可能不在同一个物体位置上,时间内插将产生不可接受的人为失真。而同时使用空间和时间平均的方法将产生不太严重的人为失真,但在存储器容量和反应时间方面作出牺牲。

通过上述方案的对比及系统的具体要求,设计中采用了场合并的办法,具体实现由帧存控制器完成。

1.3 帧存控制器

帧存储器是图像处理器与显示设备之间的通道,所有要显示的图形数据先存放到帧存储器中,然后再送到显示设备进行显示,因此帧存储器的设计是图形显示系统设计的一个关键。传统上,可以实现帧存储器的存储器件有多种,如DRAM、SDRAM及SRAM等。DRAM、SDRAM属于动态存储器,容量大、价格全家但速度较慢,且在使用中需要定时刷新。对于基于FPGA的视频处理器,需要设计专用的刷新电路,增加了系统设计的复杂程度。SRAM速度高、接口简单、容量较小。随着集成电路技术的不断发展,容量不断增大,价格也不断下降。在需要高速实时显示的视频处理系统中的使用越来越普遍。

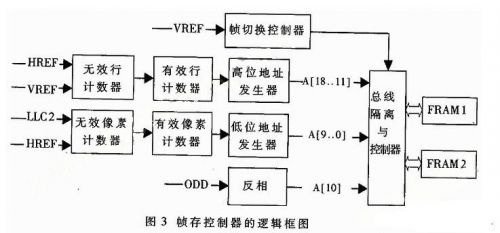

帧存控制器的设计对于实现两种不同视频系统之间的图像信号的存储、采集和显示显得非常重要。为了保证数据处理与采集的连续,设计中使用了两组帧存储器(FRAM1、FRAM2),由于数字化的图像每帧大小为640×480=307200(16bit)共300K×16bit的数据量,笔者使用每组512K×16bit的静态存储器,存储时间为12ns,可以保证快速地读出和写入图像数据。图3为帧存控制器的逻辑框图。

由于输入信号为隔行扫描的图像数据,显示输出需要逐行扫描数据,因此数据存入帧存储器时需要进行处理。设计中采用场合并行法,将两场的数据写入一个帧存中,构成一幅完整的逐行扫描图像,系统利用VREF信号对此进行控制,产生的帧切换控制信号控制数据在两个帧存中的切换。当VREF信号有效时,表明新的一场开始了,此时无效行计数器开始工作,控制不需要采集的图像行,计数到阈值后,有效行计数器开始工作,控制所要采集的图像行,并发出高位地十信号A[18..11];同样,当HREF有效后,无效像素计数器开始计数每行中的无效像素,然后有效像素计数器开始计数需要采集的行听有效像素;每次计满640个像素后,等待下一次有效行信号的到来,同时将有效行计数器加1。由于系统选用的帧存容量较大,因此利用ODD的反相信号作为帧存地址的A10,为每行图像提供了1024个存储空间(实际使用640个),可以简化数据写入与读出的控制电路。隔行的视频信号就会被逐行地存储到帧存体中。总线隔离与控制电路用来完成数据在帧存中的写入与读出的同步。由于采用SRAM作为帧存体,有效像素的写入与后续视频接口的读出不能在一个帧存体中同时进行,系统采用双帧存轮流操作的方法,系统采用双帧存轮流操作的方法:当数字化后的图像信息写入其中的一个帧存时,帧存控制器将另一个帧存中的像素顺序读出,送到显示设备,反之亦然。

1.4 视频图像的放大变换

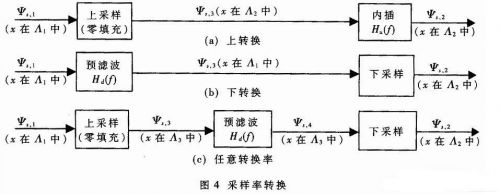

应用栅格理论几何变换处理过程可以按下面方式进行描述:给定一个定义于点阵Λ1上已采样信号,需要产生一个定义于另一个点阵Λ2上的信号。如果,Λ1中的每一个点也在Λ2中,那么此问题是上转换(或内插)问题,可以先将那些在Λ2中而不在Λ1中的点添零(即零填充),然后用一个作用于Λ2上的内插滤波器估计这些点的值;若Λ1)Λ2,即为下转换(或抽取)问题,可以简单地从Λ1中取出那么也在Λ2中的点。然而,为避免下采样信号中出现混叠,需要对信号进行预滤波,以将其带宽限制到Λ2*的沃格纳晶体。上转换和下转换的过程示于图4(a)、(b)中。更一般的情况,如果Λ1和Λ2互相不包含,就需要找到另一个即包括Λ1又包括Λ2的点阵Λ3,可以先将Λ1上采样到Λ3,然后再下采样到Λ2。此过程示于图4(c)。图4(c)中Λ3中的中间滤波器完成两个任务:首先,内插出Λ1中漏下的采样点;其次把Λ3中的信号频谱限制于Λ2*的沃格纳晶格。

由于系统中进行放大变换采用FPGA实现,因此本文讨论的重点在于如何简化实现并提高转换速度,上转换中的上采样过程为:

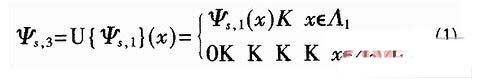

(1)式中Ψs,1和Ψs,3分别为原理图像和上采样信号;U(.)为上采样运算;Λ2Λ1表示在Λ2而不在Λ1内的点的集合。插值滤波器的定义如下:

(2)式中,d(Λ)为栅格Λ的采样密度;v*表示栅格Λ的转逆栅格的Voronoi单元,即栅格Λ原点的单位元,它向所有栅格点平移将会无重叠地覆盖整个连续空间。最简单的插值滤波为线性插值,也可以采用二加权滤波的方法。图像的缩放还可以采用3次样条插值和小波分解的方法,虽然这些方法在理论上可以取得很好的图像缩放效果,但计算复杂,即使采用快速算法,也难以实现视频图像的实时显示。

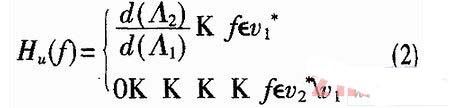

针对视频信号数据量大、数据流速度的特点,采用FPGA设计,可以完成帧存控制、视频信号的实时放大与叠加功能。基于运算速度与算法实现的难易程度分析,对视频信号的放大采用了简单的线性插值的办法,原理如图5所示。视频信号是以场或帧进行存储的,由于数据写入时存储地址与图像显示的空间位置有确定的对应关系,因此系统需要的放大处理就变为对帧存储体的地址线的控制问题。

对于本系统具体的4倍放大要求,将行同步信号先进行二倍行使能运算,并利用场同步信号对该寄存器进行复位,将生成后的二分频行同步信号控制行地址发生器,也就是产生帧存储器所需的高位地址;类似地利用像素时钟、行同步信号和场同步信号就可以得到所需的低位地址。由于在帧存控制器向帧存储器写入数据时采用了一行点1024个位置的办法,所以在低位地址后连接了一个比较器,当产生的低位地址小于640时,帧存储器的读信号有效,否则无效,以保证不会混叠入无效的数据。

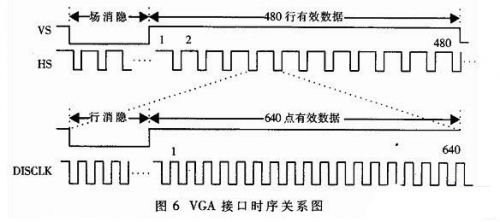

1.5 VGA接口控制器

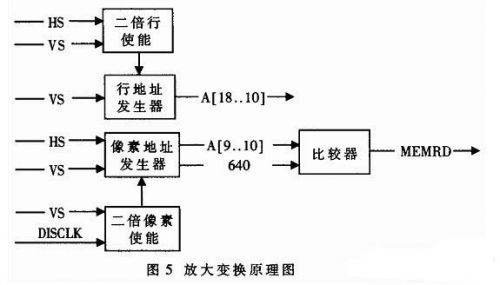

标准的VGA(640×480,60Hz)接口需要提供以下几组信号:3个RGB模拟信号、行同步信号HS和场同步信号VS。它的信号时序如图6所示。

图6中VS为场同步信号,场周期为16.683ms,每场有525行,其中480行为有效显示行,45行为场消隐区,场同步信号每场有一个脉冲,该脉冲的低电平宽度为63μs(2行)。行周期为31.78μs,每显示行包括800点,其中640点为有效显示区,160点为行消隐区(非显示区)。行同步信号HS每行有一个脉冲。该脉冲的低电平宽度为3.81μs(即96个脉冲)。因此,VGA控制器的任务就是按要求产生所需要的时序。

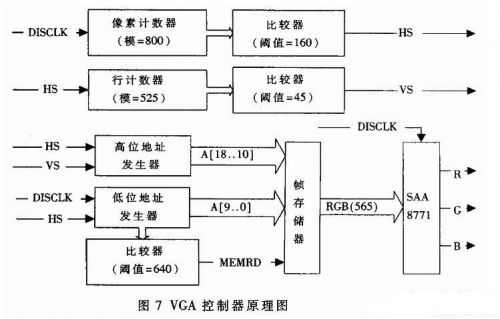

DISCLK为视频显示时钟,频率为25MHz,首先输入到模等于800的像素计数器中,输出的计数值与一个预先设好的比较器进行比较,当计数器的值大于160时,输出高电平,反之输出低电平,作为行同步信号;同理,利用一个模等于525的计数器对行同步信号进行计数和一个阈值为45的比较器可以产生所需要的场同步脉冲VS。

产生的行、场同步信号和像素显示时钟分别被送到两个地址发生器中,产生所需要的控制帧存储器的地址信号。由于前面介绍的帧存控制器中采用为每行数据提供1024个存储空间的办法,因此在数据读出时也要进行相应管理。低位地址发生器产生的地址数据与一个比较器进行比较。当地址小于640时,帧存储器的读信号MEMRD位低电平有效,否则无效,这样有效像素数据就被完整地提出。由于VGA是一个模拟的接口标准,RGB彩色信息需要输入模拟量,因此帧存储器输出的数字信息还要经过D/A变换。系统先用飞利浦公司出品的TDA8771AH,它内部集成了三个视频D/A转换器,基于电阻网络架构,转换速率最高可达35MHz。由于它专用于数字电视、视频处理等相关领域,因此使用十分简单,只需要提供24bit数字信息和一个转换时钟即可。VGA控制器原理图如图7所示。

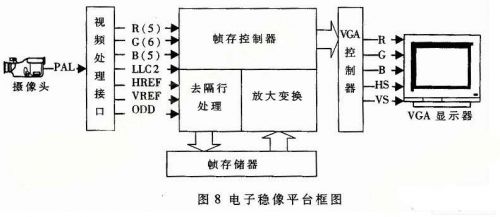

2 系统集成

综上所述,完整的电子稳像系统结构如图8所示。摄像头输入的信号采用PAL制式,经过视频处理接口后形成RGB565格式的数字视频信号和控制信息;帧存控制器作为整个平台的核心,在将数据写入帧存储器的同时,对数字化的图像信息进行去隔行处理,再将数据读出送往VGA控制器时进行放大变换。VGA控制器则负责将数据按照VGA标准时序送往显示器上。

在该平台上实现了文献中K0等人提出的一种最简单的基本位平面的电子稳像算法,对于8位的灰度图像,可以表示为:利用第4层进行运算,其依据是在多帧图像进行BPM运算后发现,该层的误差结果较平滑。然而,K0的BMP-b4算法在不同的图像序列和信噪比的情况下,并不能总得到一个最优解;在某些情况下,b4、b5或b6会得到更好的结果。

目前资料显示电子稳像技术作为近年新兴技术还处于试验研究阶段,因其适用范围广阔而展现了乐观的研发前景。

评论