基于FPGA的动态局部可重构实现方法

1 Xilinx的EAPR局部重构流程

EAPR(early access partial reconfiguration)与基于模块(module based)流程相比,有以下的主要区别:

I 移除了Virtex-II器件局部可重配置(PR)中对于局部可重配置区域必须是整列的要求,EAPR设计流程中,允许PR区域为任意矩形区域;

II 总线宏使用基于SLICE来实现,而不是基于TBUF的总线宏,这就使得允许使用的总线宏的密度更密;

III EAPR流程中允许基于模块设计中的全局信号直接穿越局部可重配置区域,而不必使用总线宏。这一改进显著地改进了时序性能,并简化了PR设计的编译进程;

IV 移除了需要在基于模块的设计中对AREA_GROUP RANG进行面积约束的限制,这样就给PR设计的布局布线提供了更大的灵活性;

V 现在的EAPR设计流程及工具支持Virtex 4和Virtex5 器件。

2 建立局部重构

局部重构的设计和实现流程可分为以下步骤:

①设计输入与综合:按照Xilin的EAPR设计流程的要求输入与综合HDL代码,包括顶层模块和子模块设计,顶层模块设计完成顶层模块的设计输入与综合;子模块设计可进行子模块的设计输入和综合。

②初始预算(initial budgeting):指构思平面布局,完成对顶层模块和每个子模块的时序约束,顶层约束包括对整个设计的全局区域约束、对每个子模块的规模和区域的约束、对每个模块的输入/输出约束和对整个设计的时序约束等内容;

③子模块的激活实现(active module implementation):对每个子模块进行激活实现,对每个子模块内部的逻辑进行单独约束;

④合并实现(final assembly):将顶层设计与已激活实现的模块合并,形成一个完整的设计;

⑤验证:包括静态时序分析和功能仿真;

⑥检查设计:用FPGA editor工具检查布线跨越模块的边界;

⑦创建初始上电的配置文件;

⑧创建重构模块的配置文件;

⑨加载初始上电的配置文件;

⑩进行局部重估操作;

3 动态局部重构系统结构

在局部重构的建立完成后,必须依托嵌入式开发套件(EDK,Embedded Development Kit)来进一步完成设计,使系统具备自重构能力,也就是能实现真正意义上的动态局部重构。

3.1 将处理器系统作为内部模块的动态局部重构系统实现方案

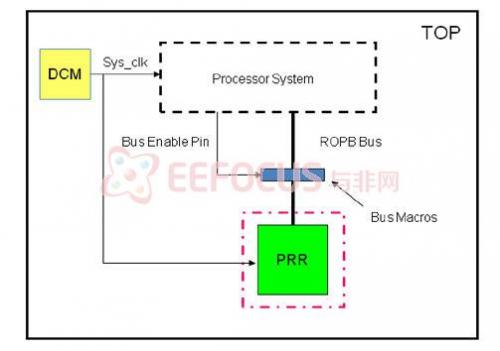

该实现方案借助嵌入式开发套件EDK建立一个处理器系统,同时借助Xilinx ISE工具建立一个顶层模块,该顶层模块包含了作为子模块的处理器系统和同样作为子模块的局部重构模块。完整的系统如下图所示:

图1 完整的系统视图

其中,PRR(Partial Reconfiguration Region)是局部可重构模块,它与处理器模块通过内部ROPB Bus连接,同时作为可重构模块与静态模块的连接还必须有总线宏Bus Macros。

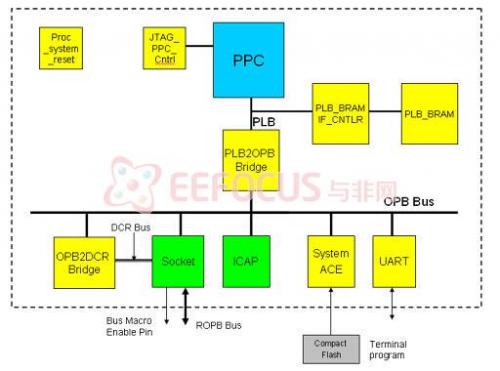

处理器系统内部结构如下图所示:

图2 处理器系统视图

3.2 SOPC动态局部重构系统实现方案

Xilinx已推出支持动态重构的FPGA产品,其Virtex-II Pro和Virtex-4、Virtex-5系列产品中已内嵌了PowePC处理器内核和内部配置访问通道(internal configuration access port,ICAP)。ICAP是配置FPGA内部结构的配置接口,为动态局部重构技术在片上可编程系统(system on programmable chip,SOPC)的应用提供了基本条件。

本方案利用PowerPC对OPB(on-chip peripheral bus)总线上挂的IP模块进行重构,从而实现了真正意义上的动态局部重构。

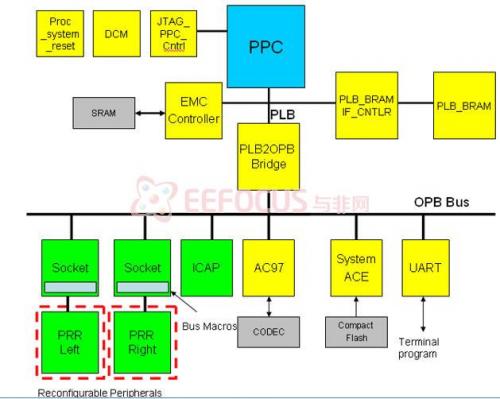

PRR Left和PRR Right为动态重构对象,它们被封装成两个挂在OPB总线下的IP模块,然后构建支持重构的SOPC系统,所构建的SOPC系统结构如图3所示:

图3 SOPC动态局部重构系统

其中,PRR Left和PRR Right是动态局部重构的IP模块;ICAP是挂在OPB总线下的IP模块,用来加载局部重构配置数据;System ACE是用来存放局部重构配置数据的Compact Flash与OPB总线的接口模块;UART负责与PC通信,显示输出。

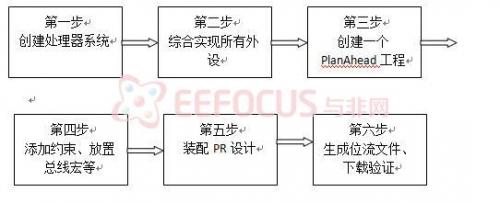

局部重构时,为了防止重构过程中局部重构操作破坏OPB总线的时序、保证重构前后PowerPC时序的连续性,先断开PRR Left/PRR Right与OPB总线的连接,再将Compact Flash内的重构配置数据写入ICAP。配置结束后,将PRR Left/PRR Right与OPB总线重新连接,最后对PRR Left/PRR Right模块进行复位操作,这样就完成了基于SOPC的动态局部重构。具体的设计和实现流程如图4所示:

图4 基于SOPC的动态局部重构流程图

3.2.1用嵌入式开发套件EDK构建处理器系统

在上文中的局部重构建立完成后,用Xilinx EDK工具构建处理器系统,图3中所示的挂在OPB总线上的IP模块都将以外设的形式加载到处理器系统中。其中,ICAP、System ACE、UART模块都有成熟的IP核提供,利用EDK中的Create or Import Peripheral工具将PRR Left和PRR Right两个IP模块以自定义IP核的形式加入到处理器系统中。

3.2.2 综合实现所有外设模块

借助Xilinx ISE工具综合实现所有外设模块,应该注意的是在综合过程中,只有顶层模块的I/O缓冲在综合时打开,其它子模块的I/O缓冲在综合时是不能打开的。

3.2.3 利用PlanAhead手工修改布局布线和装配PR设计

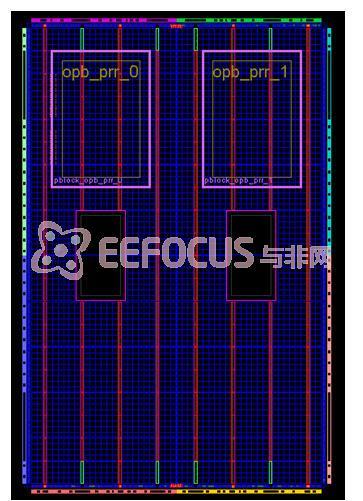

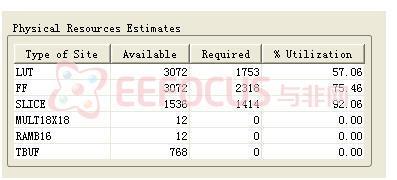

可重构模块硬件资源分配以及硬件资源分配评估、添加时序和管脚的约束都应该在这一步成功完成。利用PlanAhead工具和ISE集成的FPGA editor工具能够准确观察到整个FPGA底层的布局布线图,同时借助PlanAhead工具直观看到可重构模块和静态模块的布局布线图以及它们的资源占用情况[4]。图5所示的是系统的布局布线图,图6所示的是资源分配的情况。

图5 系统的布局布线图

图6 PRR Left重构模块的资源占用统计

在总线宏busmacros、全局时钟逻辑等手工放置好之后,将进入装配阶段,将所有静态逻辑和局部重构逻辑整合到位流文件中。在生成FPGA的初始化位流文件和局部重配置文件之后,利用EDK的Launch EDK Shell工具来生成加载FPGA时需要的System ACE文件。下一步就可以上板调试了。

评论