基于FPGA的运动鞋专用数据发送芯片及竞走电子裁判的设计与实现

1 设计摘要

FPGA芯片具有高速并行计算的特点。随着摩尔定律的发展,计算科学已经步入并行化的时代,具有并行处理能力的CPU/GPU随即面世。而FPGA芯片凭借其并行计算的能力,已经可以轻松将科学计算、逻辑运算、ASIC设计等应用并行化。我们以电子竞技裁判为切入点,将该特性普及化、应用于生活运动领域。本设计在每个竞走运动员的鞋子上都安装加速度传感器,在竞走过程中,将采集到的加速度数据通过射频发送给基于FPGA芯片设计的电子裁判,把复杂的算法、数据处理交给FPGA芯片完成,让电子裁判进行判断。这样,在数十名运动员进行竞走训练的时候,并不需要另外安排裁判员而准确测出犯规问题。大大地减轻人力资源以及从根本上提高了竞走训练的效率和灵活性,是FPGA并行化应用的一次全新尝试。

2 系统原理与技术特点

根据竞走比赛规则:

- 一个竞走运动员必须始终保持有一直脚落在地面上。

- 从前进脚落地的一刻起直到腿部达到垂直的姿势,腿部必须保持直线,膝盖不能弯曲。

我们把集成了加速传感器、射频收发器等专用芯片的运动鞋节点安装在每只专用训练鞋上,并将它固定在脚跟位置。那样,在竞走时,如果两只脚同时离地,两只脚的加速传感器都会捕获到一个同时向前的加速度。另外,由于是腾空,在竖直方向上的加速度,会和保持脚落在地面是不同的。因此,通过分析x、y、z三个方向的加速度数学模型,我们可以从中判别是否出现违规现象。

而我们的电子裁判系统是以基于FPGA芯片为基础,通过CC2500射频收发器无线接收每个运动员训练过程中传递过来的加速度。FPGA芯片收到所有运动员的采样数据后,调用相应的片内模块算法进行判断计算,依靠其并行化的特点,可以将每个运动员的数据处理并行化。如果有违规现象,可以通过亮灯或者喇叭鸣叫作出警示。最后甚至可以再将计算结果通过PCI Express总线或有线网络返回给PC机。以方便数据存储或进一步的数据分析,以监控每个运动的训练状况。

系统的技术特点有以下几点:

(1)完全的电子监控裁判系统,可以排除人为因素的疏忽错判漏判。并且在训练过程中不需要另外再安排人手,以更加灵活高效有弹性的安排训练时间和进程;

(2)利用FPGA的高速并行特性,可实现多种同类型计算的并行化,因此满足多运动员训练的同时监控,并快速作出判断;

3 系统软件流程

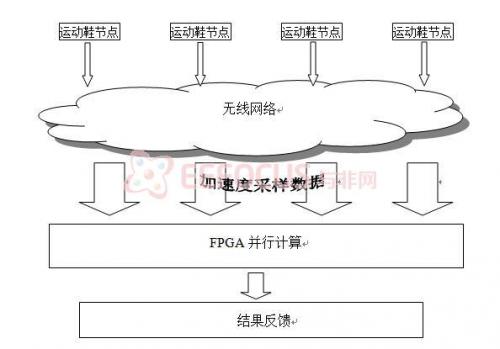

图 1 多节点数据判断的软件流程

上图所示为多节点回传采样数据并调用并行计算的过程,运动鞋节点与FPGA芯片的通信通过无线网络来完成。FPGA芯片根据接收到的采样数据、调用判断算法来判断违规现象并进行警示。

4 系统框架

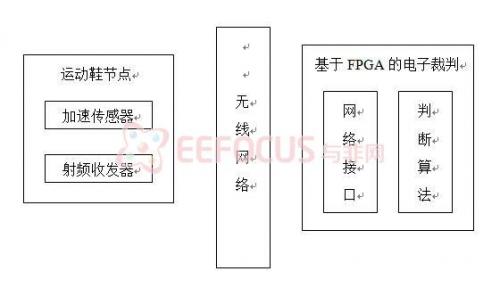

图 2 系统框架

上图所示为系统的组成结构。运动鞋节点主要有加速传感器的驱动程序,射频收发器的驱动程序;FPGA端主要有无线网络接口、犯规判断算法的Verilog HDL模块。

5 系统功能

5.1 运动鞋节点功能

(1)读写加速传感器数据

(2)无线发送采样数据

(3)异常处理

5.2 FPGA电子裁判功能

(1)接收网络数据

(2)根据采样数据调用判断算法,进行运动员违规识别

(3)对违规现象实行示警

(4)将计算模块回应的计算结果,通过PCI Express总线接口或有线网络将数据回送给PC

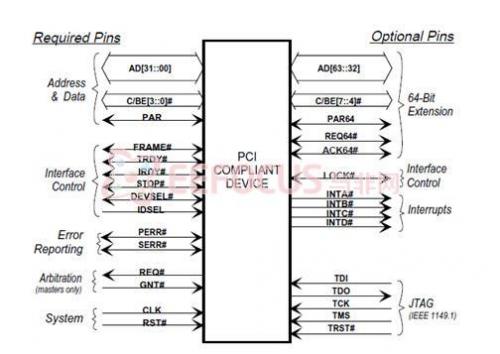

5.3 FPGA PCI Express总线接口IP核功能

(1)通过PCI Express总线读写数据

5.4 PC机数据优化模块功能

(1)根据具体的应用要求加入不同的优化算法模块

6 系统详细设计

6.1 运动鞋节点的设计

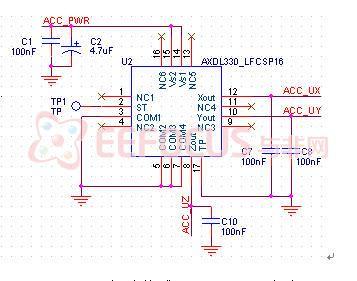

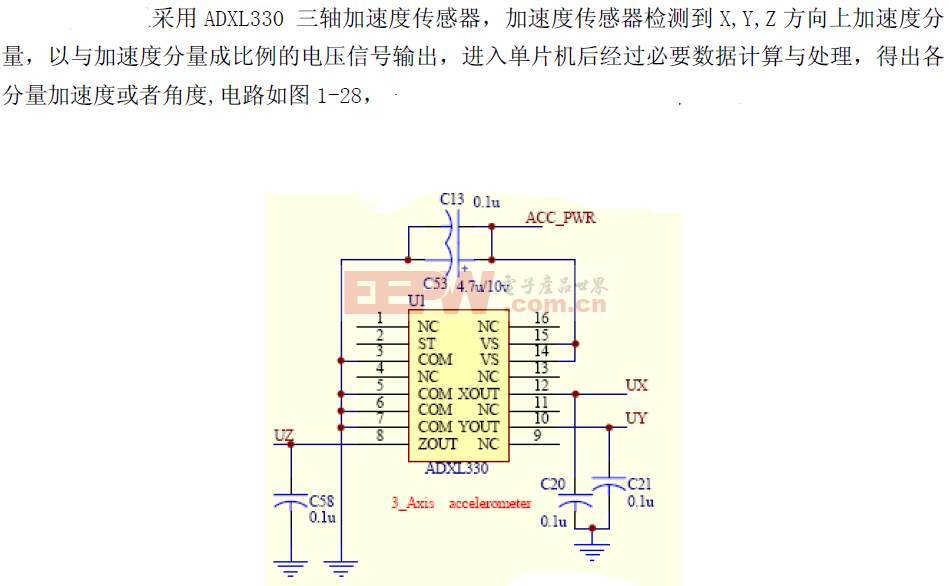

我们的运动鞋节点是以MSP430单片机为核心,并连接外部芯片加速传感器ADXL330。我们通过MSP430内部的ADC数模转换模块获得该ADXL330芯片的加速度数据。

图3 加速传感器ADXL330电路图

6.2 CC2500无线网络的设计

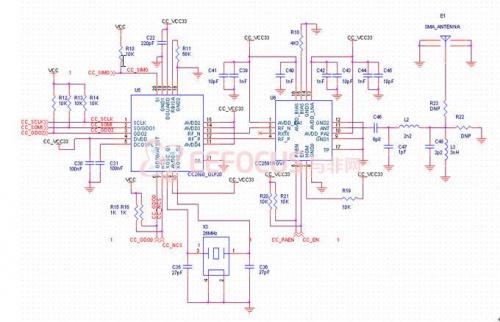

MSP430通过CC2500和CC2591相互协同工作,将从ADXL330读取的加速度数据通过无线网络传回给FPGA电子裁判作出判断。

6.3 FPGA电子裁判的设计

同样,在电子裁判端,我们用MSP430单片机和CC2500、CC2591芯片,接收无线网络传送过来的加速度数据,并通过串口与FPGA相连。但从串口的传输速度来看,通过串口传输是一个瓶颈。所以我们打算做一个有多点串口的FPGA板,每个串口连接一个MSP430,而每一个MSP430负责接收一部分的运动鞋节点的数据。

而在FPGA板上,我们写一个驱动,将串口数据存入自定义buffer里。这里的自定义buffer,是由VHDL语言写的锁存器组合而成。最后的FPGA判断算法模块,就是读取所有锁存器的数据,进行快速并行计算,得出违规结果。

6.4 FPGA端的PCI控制器模块设计

图5 PCI设备结构图

评论