基于FPGA的实时视频信号处理平台的设计,包括电路图及源代码

摘要:

介绍了一种实时视频信号处理平台的设计,该系统接收低帧率数字YCbCr视频信号,利用一片DDR2 SDRAM存储器作为帧缓存,对接收的视频信号进行格式转换、帧率提升、图像放大、色空间转换,使输入的视频信号可以在VGA显示器上实时显示;并研究了一体化摄像机光学镜头中变倍电机和聚焦电机的控制原理,实现了步进电机初始位置检测、图像变倍时变倍电机与聚焦电机的配合驱动,为了适应不同物距变倍跟踪,实现了灰度差分自动聚焦算法,实时计算当前帧图像的聚焦评价函数值,采用爬山搜索策略实现对聚焦电机的控制,使当前图像的聚焦函数值最大,实现图像的自动聚焦。整个设计采用VHDL语言实现,在Xilinx XUPV5-LX110T FPGA开发板上验证。利用该平台还可实现图像的压缩编码、解码、本地存储及以太网传输等功能。

关键词:视频处理;DDR2 SDRAM;帧率提升;自动聚焦;FPGA;一体化摄像机

1. 引言

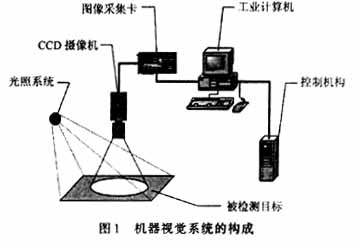

随着半导体技术的发展,图像传感器的分辨率有了很大提高,但由于处理数据量巨大,图像传感器输出高分辨率图像时帧率一般较低,其输出图像不能直接在VGA显示器上显示。为了使高分辨率图像传感器采集的图像在VGA显示器上实时显示,需要对其输出的图像进行帧率提升、色空间转换等后端处理。目前,市场上常用的视频处理芯片有PixelWorks公司的PW1226、Tvia公司的TrueView5725、Averlogic公司的AL250、威斯达公司的WSC2000等。采用上述视频处理芯片可实现视频图像的帧率提升、图像增强等功能,但由于其功能固定,不能适用于一些特殊应用场合,如图像存储、自动聚焦等。

一体化摄像机指内置光学镜头,具有变倍、自动聚焦功能的摄像机,其结构小巧、使用方便、监控范围广,已广泛应用在教学视频展台、视频监控等领域。变焦控制可实现图像的变倍、自动聚焦,是一体化摄像机中的关键技术之一。步进电机可将电脉冲信号转换成角位移,每接收一个脉冲信号就可驱动步进电机转动一个固定角度,实现物体的准确定位,通过控制脉冲的频率可控制电机转动的速度,步进电机已广泛应用于高精度控制系统中。一体化摄像机光学镜头中包含变倍步进电机与聚焦步进电机,变倍电机转动时,为使图像聚焦清晰,聚焦电机也应随之转动,具体转动步数与物距有关,具体参数可由镜头生产厂家提供的变焦跟踪曲线获得。为了适应不同物距的清晰成像,变倍跟踪结束后,还应进行自动聚焦,以显示清晰的图像。

图像聚焦程度与其高频分量有关,图像聚焦时,其包含的高频分量最大,图像最清晰,通常采用聚焦评价函数来描述图像的清晰程度。常用的聚焦评价函数主要有:高频分量法、平滑法、阈值积分法、灰度差分法、拉普拉斯像能函数等。为了提高聚焦速度,本项目采用灰度差分法实时计算每场图像的聚焦函数值,判断当前图像的清晰与否,采用爬山搜索策略,实现图像的快速自动聚焦。快速自动聚焦的实现与变倍跟踪曲线的精度、自动聚焦算法的优劣、搜索策略、电机驱动速度等因素有关。

由于FPGA 器件的可并行处理能力及其可重复在系统编程的灵活性,其应用越来越广泛。同时随着微处理器、专用逻辑器件、以及DSP算法以IP Core的形式嵌入到FPGA中,FPGA可实现的功能越来越强,FPGA在现代电子系统设计中正发挥着越来越重要的作用。本项目设计的实时视频信号处理平台利用XUPV5-LX110T FPGA开发板,并自制了视频图像采集板,采用22倍一体化光学镜头,利用FPGA开发板上的一片DDR2存储器作为帧缓存,已实现的图像的帧率提升、图像放大,并实现灰度差分自动聚焦算法,实时计算当前图像的高频分量,利用爬山搜索策略控制聚焦步进电机的转动,实现图像的自动聚焦,在该开发平台上还可实现视频图像的压缩编码、解压缩、本地存储、网络传输等功能。

2.设计性能指标

该平台可将CMOS彩色图像传感器输出的分辨率为736*576、帧率为12Hz的8位YCbCr视频信号放大到分辨率为1024*768、帧率为60Hz的24位RGB信号,经过Xilinx XUP Virtex-5LX110T开发板上的DVI转换器(CHRONTEL CH7301),可通过DVI接口在显示器上直接显示,或通过DVI-VGA转接口在VGA接口的显示器上显示。同时,实现了图像的变倍跟踪、自动聚焦功能,具体性能指标如下:

(1)输入视频图像分辨率736*576、帧率12Hz、8位YCbCr视频信号;

(2)输出图像分辨率1024*768、帧率60Hz,以DVI或VGA接口输出;

(3)具有黑白/彩色转换、图像冻结、OSD等功能;

(4)16倍光学变倍;

(5)变倍放大后具有自动聚焦功能,自动聚焦执行时间在2秒以内;

(6)支持输入图像的压缩编码、解码、本地硬盘存储及以太网传输。

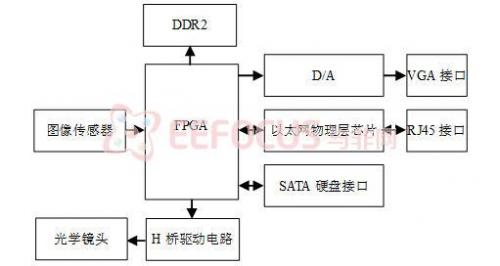

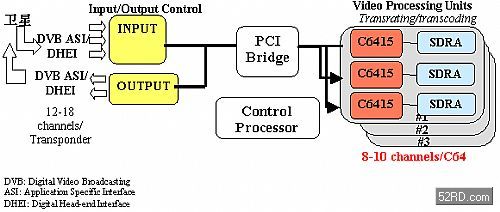

3. 系统方案

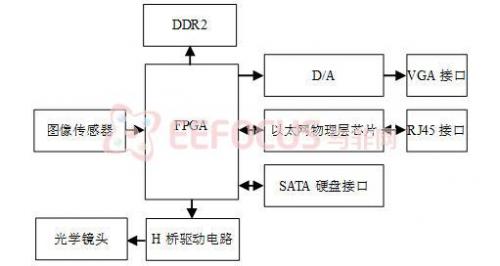

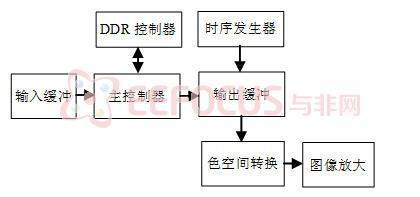

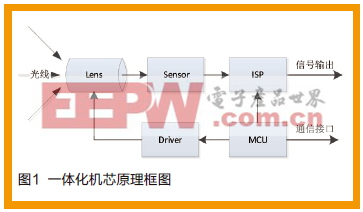

系统结构如图1所示。

图像传感器输出分辨率为736*576、帧率为12Hz的8位YCbCr视频信号,并输入到FPGA,FPGA利用外部一片DDR2存储器内的两个Bank空间作为帧缓存,采用乒乓存储机制将输入的视频帧率由12Hz提升到60Hz,将视频信号由YCbCr空间转换到RGB色空间,分辨率由736*576放大到1024*768,并产生1024*768@60Hz的行场时序扫描信号,FPGA输出的数字视频信号经D/A转换后,输出到VGA接口,从而图像传感器采集的图像可在VGA显示器上实时显示。

FPGA输出变倍电机和聚焦电机驱动信号,并经H桥驱动电路放大后输出到光学镜头,同时,光学镜头将变倍电机和聚焦电机的位置检测信号反馈输出到FPGA,用以检测当前电机位置。

系统上电后,FPGA判断光学镜头返回的变倍电机位置检测信号和聚焦电机返回的检测信号,若检测信号为低电平则驱动电机向靠近图像传感器方向转动,直至检测信号为高电平,在电平跳变处停止,同理,若检测信号为高电平,则驱动电机向远离传感器方向转动,直至检测信号为低电平,在电平跳变处停止,以上则完成对电机的初始化。初始化结束后,则驱动电机转动到一固定放大倍数位置。电机变倍时,变倍电机转动一定步数,同时驱动聚焦电机转动对应步数,具体步数可根据变倍跟踪曲线获得,变倍结束后,FPGA从输入的视频信号中提取亮度Y信号,采用灰度差分聚焦算法,实时计算当前帧图像的高频分量,图像完全聚焦时,图像聚焦评价函数值最大。利用爬山搜索策略,控制聚焦电机的转动,使当前图像的聚焦函数值最大,即当前图像最清晰,从而实现了图像的自动聚焦,从而可保证每次变倍结束后得到清晰的图像。

该视频信号处理平台可对输入的视频图像进行压缩编码(H.264、AVS等算法),通过硬盘控制器模块实现压缩图像的本地存储,并通过内部以太网控制器模块将压缩后的数据输出到FPGA开发板上的以太网物理层芯片,进而通过RJ45网络接口进行以太网传输,还可通过以太网接收压缩的视频数据流,进行解码,并通过后端处理在本地播放。

4. 系统设计

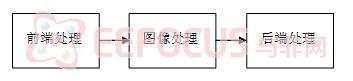

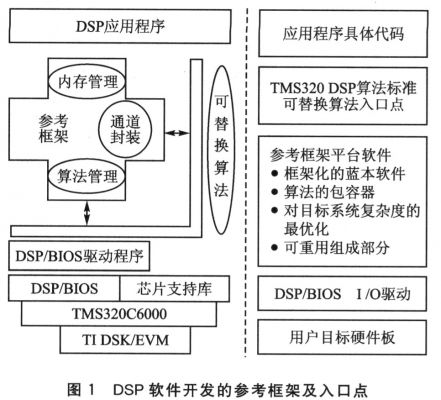

本项目采用现代EDA设计常用的“自顶向下”的设计方法,进行功能划分并按模块化设计原则,FPGA内部功能模块如图2所示。

数字视频信号输入到FPGA后,首先进入前端处理模块,前端处理模块主要实现了对外部光学电机的控制,该模块对输入的视频信号进行格式转换并提取亮度Y信号,根据亮度Y信号实现了灰度差分自动聚焦算法,并实现了步进电机初始位置检测、图像变倍时变倍电机与聚焦电机的配合驱动,为了适应不同物距变倍跟踪,利用灰度差分自动聚焦算法获得的当前帧图像的聚焦评价函数值,采用爬山搜索策略实现对聚焦电机的控制,使当前图像的聚焦函数值最大,实现图像的自动聚焦。

图像处理模块可实现图像的压缩编码(可实现H.264、AVS等压缩算法)、本地硬盘存储,并通过以太网控制器实现压缩图像的网络传输,该模块还可通过以太网接收压缩视频流,进行解码,并通过后端处理模块进行图像显示。

后端处理模块接收前端处理模块输入的视频信号,或接收图像处理模块解码的视频信号,主要实现了图像的帧率提升、图像放大、色空间转换,使输入的低帧率YCbCr视频信号在DVI接口显示器或VGA显示器上实时显示。下面详细介绍各模块的功能及实现方法。

前端处理模块

该模块接收输入的YCbCr格式8位数字视频信号,进行格式转换,转换成16位YCbCr(4:2:2)格式,根据亮度Y信号,采用灰度差分算法计算当前帧图像的高频分量。

该模块输出变倍电机和聚焦电机的驱动信号,经H桥驱动放大电路后输出到光学镜头,同时,光学镜头将变倍电机和聚焦电机的位置检测信号反馈输出到该模块,用以检测当前电机位置。

系统工作时,首先判断光学镜头返回的变倍电机位置检测信号和聚焦电机返回的检测信号,若检测信号为低电平则驱动电机向靠近图像传感器方向转动,直至检测信号为高电平,在电平跳变处停止,同理,若检测信号为高电平,则驱动电机向远离传感器方向转动,直至检测信号为低电平,在电平跳变处停止,以上则完成对电机的初始化。初始化结束后,则驱动电机转动到一固定放大倍数位置。电机变倍时,变倍电机转动一定步数,同时驱动聚焦电机转动对应步数,具体步数可根据变倍跟踪曲线获得,变倍结束后,该模块计算当前场图像的高频分量,判断当前图像的清晰度,并采用爬山搜索策略驱动聚焦电机,以实现图像的自动聚焦,从而可保证每次变倍结束后得到清晰的图像。

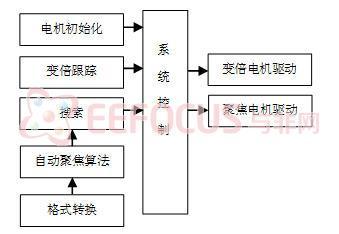

前端处理模块可分为以下功能子模块:格式转换、电机初始化、变倍跟踪、搜索、自动聚焦算法、系统控制、电机驱动等,如图3所示,下面将详细介绍各模块的实现方法。

格式转换

该模块功能是将输入的8位视频信号转换成16位YCbCr(4:2:2)格式视频信号。实现方法如下:在输入视频信号的行同步信号有效时,在第一个像素时钟同步下,将第一个8位数据写入8位寄存器1,第二个像素时钟同步下,将第二个8位数据写入8位寄存器3,同时将寄存器1的数据输出到8位寄存器2,第三个像素时钟同步下,将第三个8位输入数据写入寄存器1,同时,将寄存器2、寄存器3的数据写入到16位寄存器4,一直按此规则进行写入,则寄存器4输出16位YCbCr(4:2:2)格式数据,输出速率为原像素时钟的2分频。其内部寄存器格式如图4所示。

(2) 步进电机初始化

该模块功能是实现电机初始位置的判断,并驱动电机转动到某一固定位置。

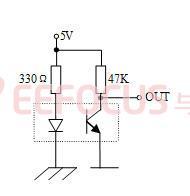

由于每次系统掉电时,步进电机的停止位置不固定,所以每次系统工作时,首先要进行步进电机位置的判断并驱动步进电机转到某一固定位置,如一倍放大位置。步进电机中用电机位置检测器来判断电机的位置,位置检测器电路如图5所示。其工作原理为,当电机驱动的检测器运动到发光二极管与光敏三极管之间时,阻挡二极管发出的光线,则三极管处于截止状态,输出信号为高电平;当检测器离开中间位置时,发光二极管使三极管导通,则输出信号为低电平。由于二极管和三极管位置固定,所以输出信号电平跳变位置是固定的。

图5 电机位置检测电路

系统上电后,根据电机位置检测器返回的状态信号判断当前电机的运动位置,若返回低电平则驱动电机向图像传感器方向移动,直至检测信号为高电平,在检测信号跳变时,停止电机转动;若检测信号为高电平,则驱动电机向远离传感器方向移动,直至检测信号为低电平,在检测信号跳变时,停止电机转动,由于检测信号跳变位置是固定的,所以系统上电后可驱动电机转动到预设置的固定位置。

(3) 变倍跟踪

(4) 自动聚焦算法

通常采用聚焦评价函数来描述图像的清晰程度,常用的聚焦评价函数有:高频分量法、平滑法、阈值积分法、灰度差分法、拉普拉斯像能函数等。灰度差分法利用图像的相邻像素灰度值差的绝对值之和作为聚焦评价函数,灰度差分算法实现简单,由于没有复杂的运算,易于在FPGA上实现,算法公式描述为:

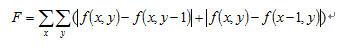

该算法实现时,缓存四行数据,实现内部功能模块如图6所示。

图6 自动聚焦算法实现内部模块

读写控制模块控制四个行缓存中数据的读写,每场图像第一行数据写入到行缓存1,第二行数据写入到行缓存2,第三行数据写入到行缓存3,第四行数据写入到行缓存4,同时,将行缓存1、2、3中数据读出到算法实现模块,第五行数据写入到行缓存1,同时,将行缓存2、3、4中数据读出到算法实现模块,按此读写规律进行直至一场图像结束。算法实现模块接收从行缓存中读出的数据,并将每个行缓存读出的数据赋值给内部相连的三个寄存器,则第二行中间寄存器对应算法中的 像素,根据聚焦评价函数值公式即可求出当前场的聚焦函数值,并将当前场图像的聚焦函数值与前一场图像的聚焦函数值相比较,如当前场图像的聚焦函数值大于前一场图像聚焦函数值,则输出比较信号为高电平,表示当前场比前一场图像清晰,反之输出低电平,表示当前场图像比前一场图像模糊。

像素,根据聚焦评价函数值公式即可求出当前场的聚焦函数值,并将当前场图像的聚焦函数值与前一场图像的聚焦函数值相比较,如当前场图像的聚焦函数值大于前一场图像聚焦函数值,则输出比较信号为高电平,表示当前场比前一场图像清晰,反之输出低电平,表示当前场图像比前一场图像模糊。

(5) 搜索

该模块根据自动聚焦算法模块输出的相邻两场图像聚焦函数值的比较结果,来控制聚焦电机的转动方向,当输出图像的聚焦函数值最大时停止转动,则实现图像的自动聚焦。

该模块具体实现过程为,变倍结束后,在图像场同步信号的消隐期间,使聚焦电机朝预定义的固定方向转动一步,在下一场图像场同步的下降沿采集自动聚焦算法模块输出的聚焦函数值比较结果信号,若该信号为高电平,则表示当前图像比前一场图像清晰,则电机转动方向正确,继续向该方向转动一步,同理,在下一场图像的场同步下降沿采集聚焦函数值比较结果信号,若为高电平,则继续向该方向转动,若为低电平,则向相反方向转动一步后停止电机转动,则自动聚焦结束;若第一次采集的聚焦函数值比较结果信号为低电平,则表明首次设定的转动方向错误,则向相反方向转动两步后,在下一场图像的场同步下降沿判断聚焦函数值比较结果信号,若为高电平,则继续沿该方向转动,若为低电平,则向相反方向转动一步后停止电机转动,则自动聚焦结束。

(6) 系统控制

该模块主要对初始化模块、变倍跟踪模块、搜索模块输出的变倍电机和聚焦电机的驱动信号(包括转动方向、步数)进行选择输出,系统上电后,首先是初始化模块产生的驱动信号有效,初始化结束后,其它模块才可正常工作,图像变倍时,变倍跟踪模块输出的电机驱动信号有效,变倍结束后,搜索模块产生的电机驱动信号有效。

(7)电机驱动模块

本项目选用的光学镜头具有变倍和聚焦两个步进电机,光学变焦22倍,步距角18°,每步位移量0.02mm,转速600~800pps,采用2-2相驱动励磁方式,驱动脉冲变化如表1所示。

表1 步进电机驱动脉冲

1 | 2 | 3 | 4 | |

A+ | H | H | L | L |

A- | L | L | H | H |

B+ | L | H | H | L |

B- | H | L | L | H |

若驱动脉冲按1à2à3à4方向循环发出,则步进电机带动的镜片朝靠近图像传感器方向移动,反之朝远离图像传感器方向移动,从而可通过产生不同的驱动脉冲控制电机的转动步数及转动方向。

该模块根据系统控制模块输出的电机驱动信号(转向,步长)来产生对应的A+、A-、B+、B-电机驱动脉冲。该模块内部为模值为4的计数器,输入转向控制信号为高电平时,该计数器加法计数,转向为低电平时,计数器减法计数,根据输入的步长控制输出驱动脉冲的持续时间长度,计数器值对应不同的驱动脉冲信号,则可产生不同方向、不同步长的电机驱动脉冲。

图像处理模块

图像处理模块可实现图像的压缩编码、解码、本地存储及以太网传输。其内部功能模块如图7所示。

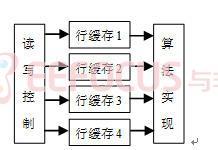

后端处理模块

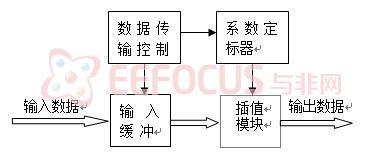

后端处理模块主要实现了图像的帧率提升、图像放大。其内部结构如图8所示。

该模块接收16位的YCbCr(4:2:2)格式视频信号,并输入到输入缓冲,输入缓冲写满一行、即736*16数据后,触发主控制器读取,主控制器将从输入缓冲中连续读取一行数据并输出到DDR控制器模块,由于DDR存储器为双沿触发,所以主控制器模块将接收的16位数据转换成32位宽。DDR控制器分别在260MHz时钟上升沿、下降沿将数据写入到DDR存储器的Bank0中,并从Bank1中每次连续读取一行图像数据,即736个数据,输出到输出缓冲中。当一帧图像都写入到Bank0中,则下一帧图像数据写入到Bank1中,并从Bank0中读取数据,一直按此规则进行读写切换。同时,时序发生器模块产生1024*768@60Hz的行场扫描信号,在行场信号都有效时,在输出像素时钟同步下,从输出缓冲中读取视频数据,由于写入输入缓冲中的数据速率较低,在写满一帧图像的时间内可从DDR中读出5帧,则输出图像的帧率可由12Hz提升至60Hz。色空间转换模块将16位的YCbCr(4:2:2)格式视频信号转换成24位的RGB信号,并通过图像放大模块将分辨率由736*576放大到1024*768。

输入缓冲模块

该模块内部包含一个异步先进先出(FIFO),宽度为16位,深度为2048,接收格式转换模块输出的16位图像数据,写入速率为原视频输入像素时钟的2分频,当写满一行图像数据(736*16)时,触发主控制器产生读使能信号,在520MHz主时钟同步下,连续读取736个数据。

主控制器模块

该模块为视频处理的主要控制模块,接收输入缓冲模块发出的读触发信号,产生输入缓冲的读使能信号,从输入缓冲中读取数据,并转换成32数据宽度,转换方法与格式转换模块原理相同,转换后的32位宽数据写入到DDR控制器模块。该模块同时接收输出缓冲模块发出的写触发信号,并向DDR控制器模块发出读请求信号,接收DDR控制器模块输出的32位宽的数据信息,并将32位宽数据转换成16位宽,写入到输出缓冲,每次连续写入数据个数为736。

当从输入缓冲模块接收完一帧数据,并写入到DDR存储器Bank0空间后,第二帧数据将写入到Bank1空间,同时从Bank0中读取数据,写满一帧数据后,进行读写切换,由于写满一帧的时间为输入图像的场周期,即83ms,读取一帧的时间为输出视频的场频,即16.67ms,则在写满一帧数据的时间内,可连续循环读出5帧数据,提高了帧率。

DDR控制器模块

该模块工作时,首先对DDR2存储器进行初始化,设置迸发长度为4。由于选用的DDR2存储器的行宽度为13位,所以设置刷新周期为64ms/213,即7.8125us。

该模块主要功能是接收主控制器模块发出的写命令、写地址、32位宽的写入数据,将数据写入到对应存储单元,由于DDR存储器为双沿触发,在内部260MHz时钟的上升沿和下降沿分别将低16位和高16位数据写入到DDR2存储器,同时接收主控制器模块产生的读命令、读地址,并读取对应存储单元的数据,输出到主控制器模块。

时序发生器模块

该模块主要功能是根据VESA标准,产生1024*768@60Hz的行场扫描信号,并在行场信号都有效时,产生输出缓冲的读使能信号。

输出缓冲模块

该模块内部包含一个异步先进先出(FIFO),写时钟为520MHz的系统主时钟,写入数据来自主控制器模块从DDR控制器中读出的视频数据,每次连续写入一行数据,即736个数据,读时钟为时序发生器模块生成的输出像素时钟,读使能为时序发生器模块输出的读使能信号。

系统工作时,主控制器模块首先向输出缓冲中写入一行数据,在读使能信号有效时读取FIFO中的数据,当快读空时,触发主控制器模块从DDR存储器中再读取一行数据并写入到输出缓冲中,由于输出缓冲的读使能信号是输出时序信号的行场同步信号都有效时生成的,行同步信号有消隐时间,所以输出缓冲模块不会出现读空现象。

色空间转换模块

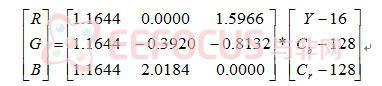

该模块将输出缓冲模块输出的16位YCbCr(4:2:2)格式视频信号转换成RGB空间(8:8:8)格式。首先将16位YCbCr(4:2:2)格式信号采用临近插值算法生成24位YCbCr(4:4:4)格式视频信号。根据CCIR-601标准,数字YCbCr色空间到RGB色空间转换的公式为:

其中,Y的取值范围是(16,240),Cb、Cr的取值范围是(16,235)。

该转换公式实现时,由于含有小数乘法,可将小数乘以211,取整进行乘法运算,将运算结果右移11位,可近似求得小数的乘法运算。

该模块生成的RGB视频信号经外部D/A转换后,可直接输出到VGA接口,则图像传感器采集的图像可在VGA显示器上实时显示。

图像放大模块

该模块实现图像的分辨率由736*576放大到1024*768。

本项目选用一种特定比例的图像放大算法。特定比例的图像放大算法的出发点是利用给定的放大比例寻找一个简单、易于实现且具有较高精度的核函数。其基本原理是,选择两个互质的整数q和p,使其比值q/p与给定的放大比例尽可能接近。于是放大算法简化为:利用原始图像的p个离散值求得连续核函数模型参数,并用采样率q对连续核函数模型重新采样,得到放大后的q个像素值。在水平和垂直方向上重复循环若干次可得到整幅图像的缩放结果。

将水平和垂直放大比例分别记为SC_X和SC_Y,则有:

SC_X = 1024/736 ≈ 1.3913

SC_Y = 768/576 ≈ 1.3333

因4/3 ≈1.3333与SC_Y近似,IZAS算法的列处理过程选择将3行原始图像滤波插值扩展为4行,即选取垂直放大比例。SC_Y0 = 4/3

7/5 = 1.4与SC_X接近,IZAS算法的行处理过程选择将5列原始图像滤波插值扩展为7列,即选取水平放大比例,SC_X0 = 7/5

垂直方向放大将3个原始像素放大生成4个新像素,其核函数公式:

f0 = g0

f1 = 1/4 g0+3/4 g1

f2 = 2/4 g1+2/4 g2

f3 = 3/4 g2+1/4 g3

其中g表示原始输入像素数据,f表示放大处理后输出的像素数据。

水平方向放大将5个原始像素放大生成7个新像素,其核函数公式:

f0 = g0

f1 = 2/7 g0+5/7 g1

f2 = 4/7 g1+3/7 g2

f3 = 6/7 g2+1/7 g3

f4 = 1/7 g2+6/7 g3

f5 = 3/7 g3+4/7 g4

f6 = 6/7 g4+1/7 g5

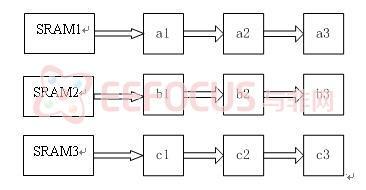

插值模块的实现需要一定的行缓存,来缓存三行数据,然后可根据插值算法来实现。设计中利用FPGA内部的块RAM存储器(Block RAM)来作为行缓存。

该模块内部功能模块如图9所示,数据传输控制模块控制对输入缓冲数据的更新和读取,并且在系数定标器模块选择相应的插值系数送给插值模块进行插值计算。本项目采用的IZAS放大算法计算每一个目标图像像素值需要原始图像相邻3行像素,因此输入缓冲模块采用3个双口SRAM来实现。可将原始图像的相邻3行像素写入双口SRAM中,计算出利用这三行数据能插值出的所有目标像素,然后更新较早写入双口SRAM对应的一行像素数据再进行插值计算。系数定标器模块含有从分辨率736*576放大到分辨率1024*768所对应的插值系数。

图9 图像放大模块内部结构图

数据存取控制处理由数据传输控制模块配合系数定标器模块和输入缓冲来实现。控制模块选择当前行数据存入哪一个双口SRAM并产生读写地址。例如水平方向要进行2倍放大时要读取2个原始像素,计算出4个插值像素,而在进行7/5倍放大时要读取5个原始像素,计算出7个插值像素。因此在进行2倍放大时连续读取缓冲里面的2个原始像素后要停顿2个像素周期再读取新的原始像素,而进行7/5倍放大时连续读取缓冲里面的5个原始像素后要停顿2个像素周期再读取新的原始像素。

当一帧中的第一行图像数据到来时,数据传输控制模块先将此行数据写入SRAM1中,不读取另外两个SRAM,第二行数据到来时控制模块将此行数据写入SRAM2中,第三行数据到来时控制模块将此行数据写入SRAM3中,当第四行数据到来时将此行数据写入SRAM1中,当第五行数据到来时,将此行数据写入SRAM2中如此反复完成数据的缓冲。另外因为图像在垂直方向也要进行4/3倍的放大,即把三行数据计算出四行,所以每缓冲三行后要停止一行缓冲。

图10 插值算法模块内部寄存器

插值模块内部对R、G、B信号各有1组9个8位的寄存器,如图10所示。这9个寄存器分成a,b,c三组,分别接收来自3个双口SRAM(SRAMi,i = 1,2,3)的输出数据。在输入时钟的同步下,寄存器a1在接收到SRAM1输出的数据之前,先完成寄存器ai 给ai+1的数据赋值操作,另外2组寄存器依次类推。

当输入到SRAM1和SARM2的数据分别满1行时,寄存器组a和b开始接收数据并进行插值滤波,同时输出放大后的数据。SRAM3同时缓冲下一行数据,缓冲结束后新的一行数据开始往SRAM1中缓冲,如此交替循环。根据上述公式滤波R、G、B三个通道之一的插值计算的结果,以寄存器组a为例说明如下:

fR0 =a1

fR1 =5/7 a2+2/7 a1

fR2 =4/7 a2+3/7 a1

fR3 =6/7 a2+1/7 a1

fR4 =1/7 a3+6/7 a2

fR5 =3/7 a2+4/7 a1

fR6 =2/7 a2+5/7 a1

为提高计算精确度,可将系数扩大210倍后与像素数据进行乘法运算,然后将乘积进行右移10位操作。

图像行数由576放大到768时,放大比例系数可选为4/3,则根据上述公式,用X[n]表示原始行相素数据,用Y[n]表示列放大后行的数据,则放大行的计算公式描述为:

Y[0]=X[0];

Y[1]=0.25*X[0]+0.75*X[1];

Y[2]=0.75*X[1]+0.25*X[2];

Y[3]=X[2];

在FPGA内部实现上述算法,将X[n]右移2位得到0.25*X[n],将X[n]右移1位与X[n]右移2位相加得到0.75*X[n]。这样通过移位相加求和代替了乘法器,节省了系统资源并避免了浮点计算带来的舍入误差。

5.系统完成的关键设计

1. 实现了对DDR2存储器的控制,利用一片DDR2中的两个BANK空间作为帧缓存实现图像的帧率提升,将帧率由12Hz提升到60Hz。

2. 采用给定比例的图像放大算法将图像分辨率由736*576放大到1024*768,实现了图像的实时放大。

3. 实现了灰度差分聚焦算法,实时计算当前帧图像的聚焦评价函数值,采用爬山搜索策略实现对聚焦电机的控制,实现图像的自动聚焦。

4. 实现了对光学电机中变倍和聚焦电机的驱动控制,完成了图像的变倍跟踪功能。

5. 建立了视频信号从输入,校正,处理,格式变换,输出,显示的完整平台,在此平台上可以进一步开发各种图像处理应用(如编解码、分析、识别、跟踪等算法)系统。

6.评测与结论

本项目设计的实时视频信号处理平台实现了输入图像的格式转换、帧率提升、色空间转换等功能,并从输入图像的亮度信息中计算当前图像的高频分量,采用爬山搜索策略,实现了图像的自动聚焦,由于对整帧图像计算高频分量,该算法得到的聚焦函数值较好的反映图像的离焦极性,可适应不同的环境,由于FPGA的并行处理能力,本项目设计的变焦控制系统可同时控制变倍电机和聚焦电机,极大提高了变倍跟踪速度。

利用平台中的图像处理部分可实现图像的压缩编码、解码、本地硬盘存储、网络传输等功能,该平台可应用于高分辨率一体化网络摄像机、视频编解码芯片的研发。该平台中前端处理和后端处理模块已在Xilinx XUPV5-LX110T FPGA开发板上验证,并获得了满意的效果。

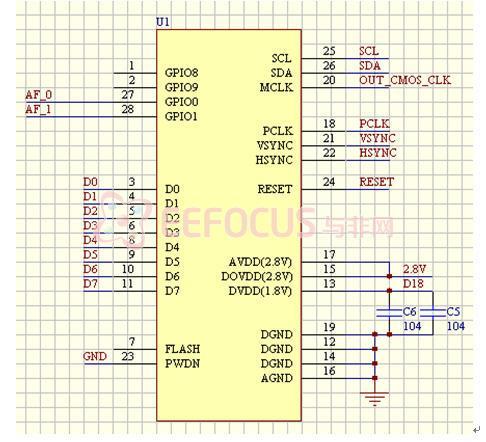

附录1 图像采集板原理图

1. 图像传感器原理图

附图1

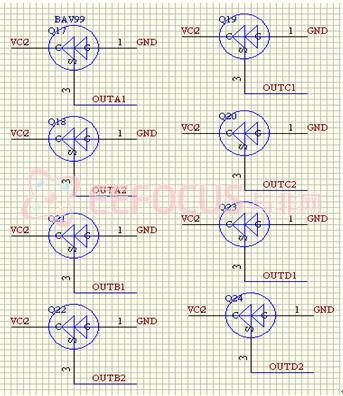

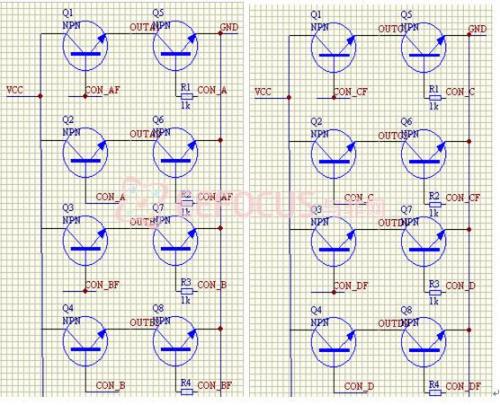

2. H桥驱动电路

附图2

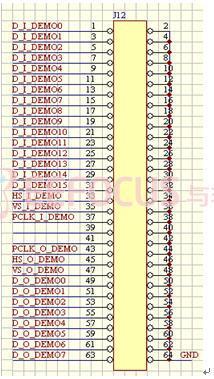

3. 图像采集板与XUPV5-LX110T FPGA开发板接口

附图3

附录2 项目中使用的光学电机

附图4

附录3 图像采集板外观图

附图5

附录4 图像采集板与XUPV5-LX110T FPGA开发板连接外观图

附图6

评论