拿来即用,指纹识别保密系统完整解决方案

1 作品背景

1.1 需求概述

在信息技术突飞猛进的今天,人们在享受进步的同时,也要遭受越来越多的数字危机。U盘, 由于其 拥有容量大、体积小、价格便宜等众多优点 ,已成为人 们移动存 储的首选设备。因此 U盘的数据安全问题也日益露出水面。世界各地关于 U盘数据泄露的事件层出不穷,既有企业私人的,也有政府军方的。1.2 现有安全方案调研

U 盘安全问题早已引起人们的关注,各大 U 盘制造厂家也都纷纷拿出自己的解决方案,经过调研,我们对市场上现有的 U 盘保密方案进行了如下总结。

在 U 盘市场上,近来又出现了基于指纹识别身份认证技术的产品,硬件上增加了指纹识别模块,但仍会依赖一段在 PC 上执行的程序,这段程序或预先安装在 PC 上,或来自 U 盘上的某块存储区域,国内代表作是亚略特系列 U 盘。除了解决了无需手动输入密码外,软硬结合方案的其他缺点依旧没有解决。

表 1-1 现 有解 决方 案比 较

解决方案 | 方案简述 | 优点 | 缺点 | 代表产品 |

机械方式 | 采用机械装置 锁住 USB 插头 | 通 用 性好 | 安全性差 | 不常见,只找到一款 日本产品 |

软件方式 | 通过在 PC 上运 行的软件程序 对磁盘分区或 文件进行加解 密 | 代 价 低,硬 件 上 无 需 做 变 动 | 1 通用性不佳,一般各厂家软件都不同,通用的软 件,如高强度 U 盘文件夹加密,只能做到文件加 密层次,安全性低于磁盘的分区加密。 2 受到 PC 病毒威胁。 3 手动输入密码位数有限,安全强度不高。 4 占用 PC 资源,加解密速度受限。 | 清华紫光系列 |

软硬结合 方式 | 将原本放在 PC 上运行的程序 存放到 U盘中, 插上后上传到 PC 执行 | 无 需 在 PC 上 安 装 软 件 | 1 通用性不佳,各 U 盘厂家由于各自硬件不同实现 方法也不同,且 U 盘硬件需改动,这种方案对老 U 盘束手无策。一般只能运行于 Windows XP/2000 系统。 2 安全强度未知,厂家一般都未公布自己的加密方 念 案和所用加密标准。 3 仍依赖于在 PC 上执行的程序进行操作,依旧受 PC 病毒的威胁。 4 主流产品依旧靠键盘输入密码。 | Kingston 08 鼠年纪 版, 台电 加密 大 师 U 盘 |

1.3 解决方案

我们的目 标是要制作这样 一个作品:作品在 整个系统中 类似一个读卡器 ,PC无需安装任何驱动和程序,U 盘无需做任何改动,针对不同厂家的 U 盘,不同的操作系统(本身插上普通 U 盘能工作),作品要有一定的通用性(最起码理论上要可行)。由指纹产生密钥,采用公认安全的加密标准 ,快速加解密,最终达到令人能够接受的传输 速率。无需上传任何程序至 PC 运行。

2 功能与指标

本作品连接在电脑 USB 接口与 U 盘之间,通过解析USB 协议,提取出需要加密的部分,对其进行加解密后置换,再转发。密码由用户的指纹特征数据经过处理后产生。

本作品对整个 U 盘进行加密(属于磁盘加密中的分区加密,相对文件加密而言安全度将更高)。加密后的 U 盘直接插在电脑上或输入的指纹不正确时,盘内数据将无法被访问。

为实现友好的用户操作界面,作品工作流程采用向导式。作品给用户提供三个按钮、一个工作模式选择开关来对其进行控制。提供两种工作模式:1)正常工作模式——流程中没有添加指纹、删除指纹的操作;2)管理工作模式——在进入正常工作模式前,用户可以进行添加、删除指纹的操作。通过 LCD 向用户提供操作提示信息。

本设备采用硬件方法实现了高速、高强度的加密标准—AES,具备高指纹识别率,达到全速 USB 设备传输速 率标准。同时本设备相对 U 盘、PC,是一个独立的设备,有很好的通用性,适用多数 U 盘和操作系统。

3 系统方案

3.1 系统框图

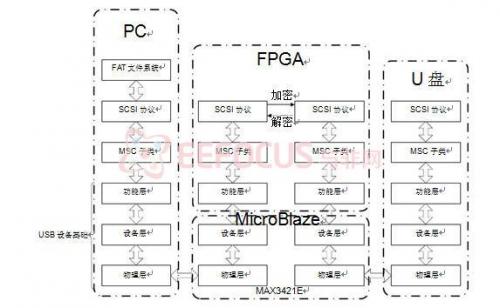

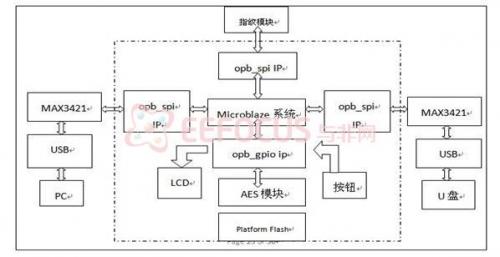

图 3-1系统总体示意图

本作品在 Xilinx Spartan3E FPGA 芯片 XC3S500E 上搭建以 Microblaze 软核为核心的微处理器系统,在 Spartan3E Starter Kit 开发板外扩展 USB 接口电路和指纹模块,结合开发板上的丰富资源来构成整个作品的硬件部分。其中 AES 算法在 FPGA 片内用 VHDL 实现。USB 协议解析、磁盘加密、密钥生成等软件部分通过为 MicroBlaze 处理器编写 C 代码实现。

整个 系统框图 如图 3-1 所示, 其中,虚 框内微处 理器系 统和加解 密模块在 开发板上 的FPGA 芯片内实现,指纹模块、USB 接口电路则在自行设计的外部电路板上实现。硬件开发平台为 Xilinx Spartan3E Starter Kit 开发板,主要开发软件 ISE 9.1i 和 EDK 9.1i。

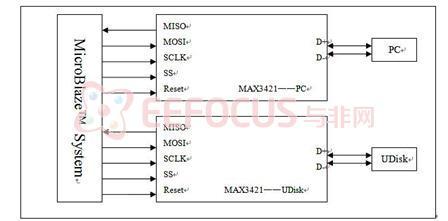

3.2 USB 接口方案

本模块电路以两片 MAX3421E 芯片为核心,分别与 PC、U 盘相连。USB 协议由底层到高层分为电气层、设备层、功能层,MAX3421E 可以实现从电气层到设备层数据的转化,从而使微处理器系统可以在设备层以上操作。该芯片内部不包含微处理器核。

目前市场上的 USB 接口芯片种类繁多,功能和应用场合各异,从 USB1.0 到 USB2.0,从主、从单功能控制器到主从集成控制器,从 带单片机核到功能单一的纯 USB 接口芯片。要在这么多的芯片中选择一款合适本系统的芯片必须通过如下的筛选:

1) 支持全速模式的传输,波特率达到 12Mb/s。

2) 片内不带有单片机核的单一 USB 芯片,因为在本系统中 FPGA 将作为中心控制器,

不应该有过多的单片机介入处理。

3) 最好有两种模式的集成以便选择,能分别提供到 PC 和到 U 盘的接口功能,即兼容

USB 主机和外设两种模 式。

4) 接口芯片与控制器之间最好使用串行通信,约宝贵的控制器 I/O 资源。

5) 外观上要尽量小巧,便于产品的小型化。

基于以上的五点,我们将选择的焦点放在了 Maxim 公司生产的 MAX3421E 上,它完全符合以上要求,是一款微处理器独立的 USB 接口转化解决方案,具备最大频率高达 26MHz的 SPI 接口,配备收发各有 64Byte 的双缓冲,有助于提高 USB 的传输速率。芯片采用 5mm×5mm 的 TQFP 封装,有利于产品的小型化。

3.3 微处理器系统

微处理器系统采用 Xinlinx 公司推出的 32 位处理器 IP 软核 MicroBlaze 作为CPU,这是最适合本开发平台的解决方案。MicroBlaze 支 持 CoreConnect 总线的标准外设集合,具有兼容性和重复利用性。

设计中 Microblaze 通过 OPB 总线和相应的接口转换 IP 核连接使用片内外硬件资源。

微处理器系统通过 SPI 总线与指纹模块通信,获得指纹特征数据。

微处理器系统通过 SPI 总线与 USB 接口电路相连,解析并控制流经作品的数据流。

微处理器系统和加解密模块之间通过并行 GPIO 接口通信。

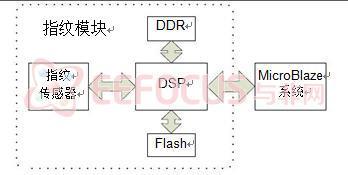

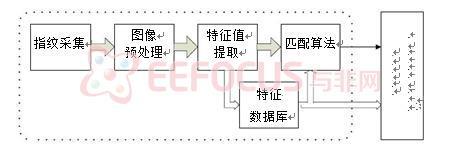

考虑到 FPGA 片内资源有限,指纹模块内部实现了指纹采集、指纹图像的预处理、特征提 取、存 储读取 指纹特 征数 据、匹 配等算 法。 能响应 微控制 器系 统的注 册、删 除、 识别验证、传输存储的特征数据等命令。

在选择指纹传感器类型 时我们的调研结果如表 3-1,最后确定采用 射频原理指纹传感器AES2510,其能采集识别 真皮层指纹,对各种指纹类 型适应性强,解决了人造 假指纹问题,增加了安全性。采用刮擦式设计,面积更小,成本更低,且能采集到足够大的指纹图像。

采用运算功能强劲的 DSP 芯片 TMS320VC5416 作为核心控制处理芯片,外接 Flash、DDR芯片构成模块固件执行和存储数据的硬件平台。 向微控制器系统提供 SPI 接口通信。

表 3-1 各 种类 型指 纹传 感器 对比 表

采集技术 | 贴膜光学 | 不贴膜光学 | 电感电容压感 | 热敏 | 射频 |

人造指纹的判别能力 | 很坏 | 坏 | 较好 | 好 | 好 |

手指识别率 | 较好 | 坏 | 坏 | 较好 | 好 |

脏手指识别率 | 坏 | 坏 | 坏 | 较好 | 好 |

油手指识别率 | 较好 | 较好 | 坏 | 较好 | 好 |

老人识别率 | 较好 | 坏 | 坏 | 较好 | 好 |

气候变化适应能力 | 较好 | 坏 | 坏 | 较好 | 好 |

抗震动适应能力 | 坏 | 坏 | 好 | 好 | 好 |

抗静电适应能力 | 好 | 好 | 坏 | 坏 | 好 |

表面耐磨 | 坏 | 好 | 坏 | 较好 | 好 |

温度范围 | 0-40℃ | 0-40℃ | -5~40℃ | 夏天不能使用 | -30~70℃ |

3.5 密钥生成

作品中密钥生成算法采用 ANSI X9.17 标准。之所以选择 ANSI 9.17 算法来将指纹特征数据转换为密钥,主要有两点原因:1)作品中已经实现了 AES 加密模块使得该算法实现非常方便;2)相对研究过程中我们曾使用过的 SHA512 算法而言,该算法有效地减少了代码量和执行代价,节省了空间。因为 FPGA 片内允许的最大代码量为 32K,若超过 32K,就得将代码放至片外 DDR 中执行。这样的缺点是程序执行速度相对片内将大大变慢,此外,FPGA 配置、程序自动加载到 DDR 中执行也将是个问题,一是 需编写 Bootloader 程序,二是 DDR 消耗资源较多,大概占 20%片内资源(在本作品开发平台上),在本作品现有架构上加上 DDR 之后根本没有资源再加挂一个 Flash,故 Bootloader 程序也无法编写和使用 。

3.6 加解密模块

加解密模块采用 AES 算法,通过 VHDL 设计的数字电路实现。该模块从 MCU 系统获得密钥和明(密)文,处 理后返回密(明)文。由于采用硬件电路实现,因此 可以获得很高的工作速度,同时也使 FPGA 中剩余的逻辑资源得到了充分的利用。

在设计该模块电路及其 通信协议时,还充分考虑了其移植性,密钥扩展和加 解密模块是可以分离的,因此 在某些逻辑资源受限情形下,可以将密钥扩展部分放到微 处理器系统中以软件方式实现,而不影响整个模块的工作速度。

在设计该模块时亦反复 权衡了工作速度与资源消耗两个指标,在资源许可的 情况下尽量

提高工作速度。

3.7 USB 协议解析及磁盘加密

图 3-2系 统加 解密 协议 栈到

图 3-2 描述的是整个系统对 USB 数据的处理过程。USB 接口芯片 MAX3421E 通过连接PC 的 USB 接 口 获 得 底 层 的 差 分 数 据 信 号 , 对其 进 行 转 化 , 利 用 SPI 总 线 接 口 向MicroBlaze 系统提交解析后的数据包。然后 MicroBlaze 进行后续向上的进一步解析。在 SCSI层解析出的数据包是要写入到 Flash 中的数据块、地址及其数据长度等信息。调用 AES 模块,对 数 据 加 密 , 之 后 把 它 按 照 加 密 前 的 方 式 转 发 , 在 物 理层 再 次 通 过 工 作 在 主 机 模 式 的MAX3421E 发送给 U 盘。

4 实现原理

本章将围绕图 3-2 做详细的阐述。

4.1 USB 物理、设备层解析

有四种 packet(令牌、帧开始、数据包和握手)进入 MAX3421E,通过读取 MAX3421E的寄存器可以获得以上四种 packet 的信息,将它分为配置数据和传输数据分别处理。配置数据是 PC 控制 U 盘的,流向只可能从 PC 至 U 盘,而传输数据则是双向的。要从这些数据中区分出哪些数据是将要被存到 Flash 中的,哪些是控制 U 盘操作的。对于那些控制 U 盘操作的数据,MicroBlaze 直接转发给 U 盘,而从 Flash 读来的或者是要写到 Flash 中的数据就需要进行加解密再转发。

从主机发来的数据包根据它们不同的类型发往不同的 USB 端点。USB 端点是 USB 设备特有的一种硬件的接收发送单元。USB 主机与 设备之间都是通过端点来传输数据的。端点是桥 梁 和 纽带 , 不 同的 端 点 其传 输 数 据 的能 力 不 同, 适 于 不 同的 应 用 场合 。 在 Bulk OnlyTransportation 的海量存储实现规范(见 4.3 节)中,使用了三个端点,他们分别是控制端点、数 据输出 端点和 数据输 入端 点。控 制端点 可以 用于控 制命令 的输 出,配 置信息 的输 入和输出,它通常表示为 0 端点,这个端点的流向是双向的,不会出现 STALL 的状态,它负责设备的配置交互,最大 信息包 64 字节。输入输出端点负责数据的输 入、输出,他们都是单向的只能负责输出或者输入,最大信息包 64 字节(USB 全速设备)。

表 4-1 B OT 端点 的属 性

端点 | 传输类型 | 端点类型 | 传输方向 | 最大传输包 |

0 | 控制输入 控制输出 | 默认 | 输入 输出 | 64Byte |

1 | 数据输出 | 普通 | 输出 | 64Byte |

2 | 数据输入 | 普通 | 输入 | 64Byte |

4.2 USB 的枚举过程

枚举过程定义为:当设备插入系统时,主机对设备进行配置,获取 USB 设备的各种描述(包括设备描述、配置描述、Bulk Only 数据接口描述、Bulk-In 端点描述、Bulk-Out 端点描述和字符描述),这也就是 USB 设备为什么可以热插拨的原因。USB 设备可分为以下几类:显示器、通讯设备、 音频设备、人机输入、海量存储„„特定类的 设备又可划分成子类。枚举使得主机可以精确定位 USB 设备类型,搜 索相应的驱动程序。

通用海量存储设备(General Mass Storage Device)的设备描述中,不同的 U 盘在某些具体的字段会具备不同的值。对于不同的字段值,在程序中采取了相应的措施以提高 U 盘的兼容性。USB-IF 推荐 使用批量传输(Bulk-Only Transportation)模式,所以 我们的系统也将采用批量传输模式。

4.3 批量传输协议(Bulk-Only Transportation Protocol)

在完成 U 盘的枚举过程之后,识别出为 Bulk-Only 的 Mass Storage 设备,然后即进入Bulk-Only 传输方式。 在此方式下,PC 与 U 盘之间所有数据均通过 Bulk- In 和 Bulk-Out 来进行传输,不再通过控制端点传输任何数据。

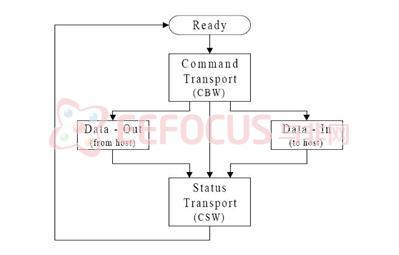

图 4-1命令 、数 据 、状 态流程 图

在这种 传输方式下,有三种类型 的数据在USB 和 设备之间传送,CBW、CSW 和普通数据。CBW(Command Block Wrapper)是从 USB Host 发送到设备的命令,命令格式遵从接口中的 bInterfaceSubClass 所指定的命令块,这里为 SCSI 传输命令集。USB 设备需要将 SCSI命令从 CBW 中提取出来,执行相应的命令,完成以后,向 Host 发出反映当前命令执行状态的 CSW(Command Status Wrapper),Host 根据 CSW 来决定是否继续发送下一个 CBW 或是数据。Host 要求 USB 设备执行的命令可能为发送数据,则此时需要将特定数据传送出去,完毕后发出 CSW,以使 Host 进行下一步的操作。USB 设备所执行的操作可用图 4-1 描述。

在流程图中包括了三种形式的数据包,USB 的设备层统一将他们看成数据,不加区分的进行传输,而在功能层上才开始区分这三种不同形式、不同功能的数据包。

4.4 SCSI 指令(Small Computer Systems Interface Block Commands)

在 4.3 节中介绍的 BOT(Bulk-Only Transportation)协议的 CBW 数据包中有一个长度为 6到 12 不等的字段 CBWCB,其传输的就是 SCSI 命令。

表 4-2 MSC 基 本 S CSI 命 令集

INQUIRY

命令描述查询设备的详细信息,如生产厂家、序列号等

READ CAPACITY(10)

READ(10)

REQUEST SENSE

TEST UNIT READY

WRITE(10)

读取 Flash 容量,扇区大小以及总扇区数

输入要读取的数据,从 Flash 读出

请求判断,用于发生错误时系统自我纠正

测试单元准备,电脑通过此命令保持 U 盘一直处于激活状态

提供 Flash 地址,向 Flash 写数据

SCSI命令集是 一套能够完成 对一般外接存 储系统设备 的存取、配置 、检查等任务 的完备指令 集。SCSI拥 有的这套指令 集有很多指 令,不同的 版本分别用 在光驱、硬盘、 软驱等设备的控制中,表 4-2 列出的 6 条指令已经可以完全实现 USB 存储设备的操作了,这一特性大大减小了设备设计的难度与复杂度。Bulk-Only 的 CBW 中的 CBWCB 字段就是对以上这些命令的描述。

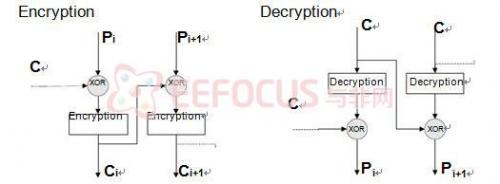

4.5 基于 CBC-ESSIV 模式的磁盘加密机制

在过去的很多年里用户 数据的保护大多停留在文件级别的加密技术上,而磁 盘加密技术一直由于软硬件上的瓶 颈而止步不前。随着计算机理论以及硬件的飞速发展 ,现在的计算机使用者,不管是专业人 员还是普通用户,在选择自己的加密手段 时则更加倾向于磁盘加密。

一是因为磁盘加密可以 通过高速的硬件实现透明访问;二是可以在磁 盘加密的基础上再使用文件加密,从而达到双重加密的高强度加密效果。

在加密方式上,毋庸置疑 AES 一直被用在了磁盘加密上,不只是因为它的安全性能,更因为 AES 是一种很好的分析加密算法。但是在加密模式上一直存在一定的问题。普通的 ECB模式因为它的一一对应容易受到水印攻击(watermarking attack),而 CBC(Cipher Block Chain)式一直以来是众 多模式中使用最为广泛的加密模式,即便是在某些方面存 在一些不足。综合考虑各种因素,CBC 仍然具有多方面的优越性。

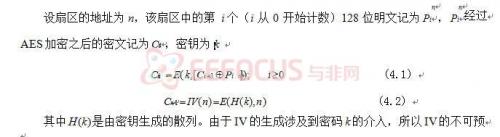

在一块可以扇区寻址的 Flash 或者硬盘上,通常一个扇区的大小为 512Byte,那么一个扇区 所需 要 的 AES 加 密 次 数 为 32 次 。 这 32 次 加 密 我 们 就 使 用 CBC 模 式 完 成 , 由ESSIV(Encrypted Salt-Sector IV)算法生成 IV(In itiation Vector)初始化向量。

经过其中 H (k ) 是由密钥生成的散列。由于 IV 的生成涉及到密码 k 的介入,所以 IV 的不可预测性很大程度增加了破解的难度。

4.6 FAT 文件系统

FAT 文件系统包括 FAT16 和 FAT32 两种,他们分别应用在不同大小的 U 盘中,有的 U盘两者都可以使用,但 是根据簇的大小以及寻址的位数,在不同容量的系统 中,他们会体现出不同的磁盘效率。

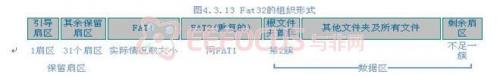

图 4-3FAT 文件 系统

如图 4-3 所示,FAT 主要有四部分组成:DBR (DOS Boot Record) 即操作系统引导记录区、FAT (File Allocation Table) 即文件分配表、 根目录、数据区。这四个部分随着 FAT 的位数的不同有略微的变化,但是磁盘的实现原理是一样的。

DBR 主要存储了跳转指 令、BPB 等一些分区信息,用于操作系统对 分区的识别以及进一步的操作。FAT 用于存储磁盘中大于一簇的文件的跨簇存储的信息,采用链表的方式实现了文件的连续和不连续的存储,同时 FAT 会存有相同的两份,以供其中一个出现错误时恢复用。根目录记录了 根目录下的文件、文件夹信息和他们所在的实际首地址、 长度等信息。最后便是所有文件数据存储的区块。

在 USB 的读写过程中,USB 控制器无需对文件系统有任何了解,在对文件的处理过程中所需要的操作全部由 PC 机上的操作系统完成,将需要读写的数据读出或写到 Flash 中。而USB 所要做的就是不断的响应 PC 的请求,这些请求就是 4.4 节所述的 SCSI 的读写命令,完全不需要管上层的文件 系统究竟在做什么工作。这一层与层之间 的独立的特性也为系统的实现以及对磁盘的加密提供了理论前提。

4.7 指纹特征提取与密钥生成

4.7.1 指纹特征提取

指纹模块完成指纹采集、指纹登记、指纹 1:N 和 1:1 比对等与指纹有关的操作。它由高速信号处理器 DSP 芯片 TMS320VC5416、指纹传感器(滑动式)、高性能指纹比对算法等软硬件组成。采用 SPI 总线接口和控制器通信。模块上的指纹传感器芯片为 AuthenTec 公司的EntréPad 2510 芯片,该芯片体积功耗都很小,对各种指纹适应能力非常强,并且从原理上讲只对人的真皮皮肤有反应,从根本上杜绝了人造指纹的问题。

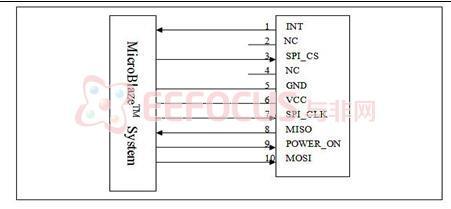

下面是指纹模块硬件内部原理框图:

图 4-4指纹 模块 内部 硬件 框图

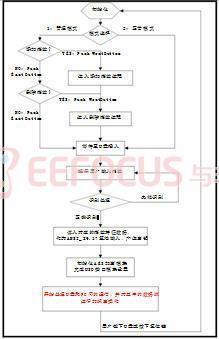

下面是指纹模块识别算法流程图:

图 4-5指 纹识 别算 法流 程图

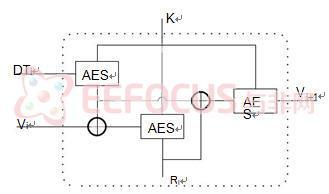

4.7.2密钥生成

这部分 工作是由MicroBlaze完成的。MicroBlaze从指纹模块读取到某个 指纹特征数据后,通过 ANSI X9.17 算法产生密钥。ANSI X9.17 是最强的伪随机数发生器之一,有一些应用使用了这种方法,如金融安全应用和 PGP 等。

图 4-6ANSI X9.17 伪 随机 数发 生器

上图中 K 为密钥,按照 ANSI X9.17 这个密钥是保密的。指纹特征数据分为 128bit 每组,最后一组若不足 128bit 则以 0 补足,作为 DTi 输入。Vi 为第 i 轮的初始种子值。Ri 为第 i轮产生的伪随机数。作品中取最后一轮产生的伪随机数作为密钥。

5 硬件框图

系统硬件实现框图如图 5-1 系 统 硬 件 实 现 框 图 所 示 。 虚 线 框 内 均 在starter kit 开发板上实现,虚线框外在自行设计的电路板上实现。

图 5-1系统硬 件实 现框 图

5.1 微处理器模块(MicroBlaze 系统)

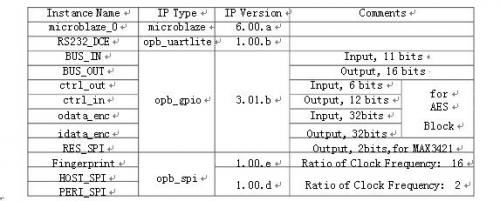

本系统中使用了 Xilinx 公司 IP Version 为 6.00a 的 Microblaze 软核作 为 CPU。其主要工作是过滤 PC 与 U 盘之间的数据传输,解析协议,提取需要加/解密部分交给 AES 模块,与指纹模块通信并生成密钥。系统部分 IP 核定义总结如表 5-1 所示:

表 5-1 MicroBlaze 系统部分 IP 核定义

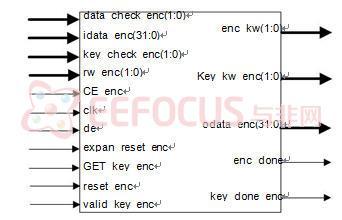

5.2 AES 加密模块

AES 模块是用 VHDL 语言设计的加密电路,采用 128 位密钥,工作在 CBC 模式。用户通过指纹验证后,MicroBlaze 获得 128 位密钥,然后将其写入 AES 模块。AES 模块内部存储并扩展密钥,用其加密 MicroBlaze 发来的数据。图 5-2 是本模块引脚图。

图 5-2AES 模块引脚图

Microblaze 首先 将 密 钥发 给 AES 模 块 , AES 模 块完 成 密 钥扩 展 后发 出 信 号通 知Microblaze。 这 时 ,Microblaze 便可 以 将 数据 写 入 AES 模 块, 运 算完 成 后 读出 数 据 。当Microblaze 发到“de”端口的信号为“0”时,AES 模块工作在加密模式,为“1”时工作在解密模式。

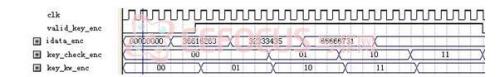

Microblaze 是 32 位的处理器,密钥和数据需要分 4 次写入或读出。我们定义了一组握手协议来完成密钥及数据的交互。写入密钥时,首先 Microblaze 将最低的 1 个字写进 idata_enc, 再将 key_check_enc 设为“00”。AES 模块判断出 key_check_enc 等于 key_kw_enc,在下一个时钟周期将 idata_enc 的数据读入,并将 key_kw_enc 信号加 1。Microblaze 发现 key_check_enc 与 key_kw_enc 不等,证实上一次写入的数据已经被 AES 模块接收,于是将下一个字的密钥加到 idata_enc,再将key_check_enc 加 1。这样,新的一个字的密钥就被写入 AES 模块。当 key_kw_enc 为“11”时,加 1 后又重新回到“00”,4 个字的密钥就成功写入。写入密钥的波形图如下:

图 5-3

写入数据的过程相似,不再赘述。

密钥 写入 波形 图读出数据时,以 data_check_enc 信号为地址, odata_enc 输出运算结果中相应的字。 AES 算法需要进行 10 轮运算。本模块中每轮运算仅需 8 个时钟周期 ,80 个时钟周期即可 完 成 一 次 加 密 或 解 密 运 算 。 按 照 系 统 50MHz 的 时 钟 频 率 计 算 , 本 模 块 最 高 可 达 到10Mbyte/s 的加解密速度。当然,每次加密前需要将数据写入 AES 模块,加密后再将数据读出。这部分占用的时间取决于 Microblaze 处理器的指令周期,所以实际应用中的运算速度要比 10Mbyte/s 小。5.3 USB 接口电路模块

USB 接口电路以两块美国 MAXIM 公司的 MAX3421E 芯片为核心。MAX3421E 是一款USB 控制器,既可作 USB 外设又可作 USB 主机。在这里,与 PC 相连的 MAX3421E 芯片使用 USB 外设工作模式 ,与 U 盘相连的 MAX3421E 芯片使用 USB 主机工作模式。

图 5-4

芯片具有通信速 率可高达USB 接 S 口电 路信 号图 26MHz 的 SPI 接口,在Micro Blaze系统中使用的是v1.00.d 版本的 opb_spi IP 核实现 SPI 接口,其允许的最小分频数为 2,而 opb bus 的时钟频率为 50MHz, 所以 此 处 spi bus 时 钟 频率 为 25MHz。两 块 芯片 均 工作 在 SPI 从机 模 式,MicroBlaze 系 统的 SPI 口为 主 机模 式。 主 从机 的 SPI 工 作方 式均 保 持默 认: CPHA=0,CPOL=0。 MAX3421 芯片提供了 D+、D-引脚,在串联 33Ω电阻后可直接连至 USB 总线。而且芯片内部集成了 ESD 保护和 VBCOMP,使外围电路进一步简化。为进一步保护插入的设备,我们在主机工作模式的 MAX3421 芯片外部又添加了限流芯片 MIC2545A,限流电阻选取 470Ω,最大允许电流为 490mA。

MAX3421 芯片内部集成了±15KV ESD 保护功能,故外围电路中没有再增加静电防护电路。

5.4 指纹模块

指纹模块采用深圳艾菲尔公司设计生产的 EFM-200 通用型指纹识别模块。它由高速信号处理器 DSP、指纹传感器芯片 AES2510、高性能指纹比对算法等软硬件组成。

图 5-5指 纹模 块接 口定 义

指纹模块通过 SPI 接口与 MicroBlaze 系统通信,指纹模块为从机,MicroBlaze 系统为主机。工作模式为:CPHA=0,CPOL=1。Pin3 为 SPI 从机选择引脚(低电平使能),Pin7 为SPI CLOCK 引脚,Pin8 为 MISO 引脚,Pin10 为 MOSI 引脚。MicroBlaze 系统中使用 v1.00.e版本的 opb_spi IP 核实现 SPI 接口,opb 总线频率为 50MHz,分频系数采用 16。

Pin1 为指纹模块中断脚,本系统中采用查询该引脚的方式来获得指纹模块状态信息,当该引脚为低电平时,说明指纹模块准备好数据待主机读取。Pin9 为电源使能引脚,当其置低时,指纹模块上电。在 MicroBlaze 系统中通过 opb_gpio IP 核对其进行控制。Pin6、Pin5 为电源和地,均与开发板相连。Pin2、Pin4 为保留引脚。图 4.7 是其示意图。

5.5 配置电路

作为一个完整的 FPGA 设计,配置方案是最后一步也是不可缺少的一步。本设计中采用是 Xilinx Platform Flash 作为我们设计的配置方案。在 Spartan3E starter kit 开发板上有一块 4Mbit Xilinx XCF04S serial Platform Flash PROM,通过 iMPACT 工具可以方便地生成FlashPROM 文件,然后采用主串行模式将 Platform Flash PROM 上的存储信息配置到 FPGA,实现FPGA 的上电自动加载功能。这是最简单也是最适合本开发环境的解决方案。

参考应用文档 XAPP482,还可应用该 Flash 实现更多功能,限于本设计的应用,不再做进一步探索,提出这一点只是为了说明,这个配置方案也支持对设计的进一步开发和改进。

6 软件流程

图 6-1软件 工作 流程 图

首先,当 USB 接口模块全部完成初始化之后就开始最初的 USB 枚举(enumeration)过程,涉及到各种描述的 获取,包括设备描述、地址设置、配置描述、字符串 描述、端点描述等等,而且随着描述请求的进行,部分描述还会不断的重复,直到计算机完全明白这个 USB设备究竟 具有什么功能 、该调用什么驱 动程序来对这个 设备操作。对于 市场上众多的 Flash闪盘,我们保证让每一条 PC 请求都能够到达 U 盘,U 盘的每一个回应都转发给 PC。这样保证了直接插到PC 端能够识别的 U 盘,使用本作品也能够被识别。

枚举完成之后 USB 进入数据传输阶段,当然这些数据都是对底层 USB 控制器而言的数据,对于要对 USB 数据进行解析的 FPGA 中的 MicroBlaze 程序而言,则仍然需要将其中的数 据 分 为 三 个 类 型 : CBW 、 数 据 、 CSW 。 这 三 种 类 型 数 据 的 详 情 请 参 考 4.3 节 。 当MicroBlaze 收到 CBW 之后就将它转发出去,在转发的同时判断该 CBW 是不是一个读写操作的命令,如果是则代表跟在 CBW 之后的数据是直接来自 Flash 或将要写到 Flash 中去的,那么在数据段的转发操作之前还需要将他们送到 AES 模块进行 CBC 模式的加解密。在数据传输完成之后,必须等待 USB 设备回应 CSW 表示整个会话过程完整无误之后才能进入到下一个请求回应的处理循环中去。

7 测试与总结

7.1 总述

系统测试采用先局部后整体的方案,首先将各个模块(USB 数据透传模块、指纹模块、AES 加密模块)在分离的情况下单独测试,通过对它的各种操作来尽可能多的暴露问题,并一一解决。最后再将三者组合起来进行总体测试。

对 于硬 件测 试, 依靠 SPATARN 开发 板上 的按 钮、 LCD、 LED 灯 来帮 助调 试。 同时RS232 串口能更加方便的将程序中产生的数据、变量实时的发送到计算机供,借助 PC 端的串口程序(Terminal v1.9b、AccessPort),硬件程序中的数据得以在 PC 上保存、分析。测试中用到的主要工具有:

1) Bus Hound 5.0。一款用于分析 PC 上 IO 数据软件,能够对多种协议的数据包进行截取、解析并保存。这些数据代表了在 PC 上看到的 USB 数据,与串 口发回的 USB 数据对比可以找到程序的漏洞,并作出相应的改进。

2) USB- IF Test Suite。USB 开发者论坛提供的用于 USB 标准测试的软件,能够查看当前设备是否符合国际标准。

3) HD Tach v3.0.4.0。用来对 USB 的传输速 率测试,它会对 U 盘提供大小不同的数据包,分别计算他们的传输速率。

4) ATTO Disk Benchmark v2.34。同样是 USB 测速软件,使用不同的两款软件可以提高测试数据的可信度。

WinHex 15.0 SR-2。用于观察 Flash 上每一个扇区的数据变化,有效地判断加密的正确性并评估效果。

7.2 指纹模块的测试

指纹模块由深圳艾菲尔公司设计生产,相关测试指标及结果均由艾菲尔公司提供。

表 7-1 指 纹模 块 各项 指标 性能( 深圳 艾菲 尔 公司 提供)

技术指标名称 | 数值 |

探测皮层 | 真皮层 |

认假率 FAR(实际测试值) | 0.00008% |

拒真率 FRR(实际测试值) | 0.005% |

指纹容量 | 15 枚 |

图像分辨率 | 500dpi |

平均匹配速度 | 1 秒 |

抗静电能力 | IEC61000-4-2 标准 15KV |

抗磨损强度高 | 1 百万次 |

峰值耗电 | 150mA |

工作环境温度 | -10°C 至 70°C |

最大工作湿度 | 98% |

工作电压 | 3.3V |

尺寸 | 4.4 x 6.6 cm |

7.3 VHDL 实现的 AES 加密模块的测试

测试方案

National Institute of Standards and Technology (NIST) 发布 AES 标准的文档Announcing the ADVANCED ENCRYPTION STANDARD (AES) 中,以附录的形式给出了一组 128 位密钥的加解密数据。我 们选择 ISE Simulator 为仿 真器,将这组数据的明文与密钥作为 输入,看加密后的结果是否正确。再将加密结果作为输入,看解密后是否为原文。

测试数据

数据来自于 NIST 发布的联邦信息处理标准(FIPS PUBS) 197 。

明文:00112233445566778899aabbccddeeff

密钥:000102030405060708090a0b0c0d0e0f

密文:69c4e0d86a7b0430d8cdb78070b4c55a

结果分析

在 ISE Simulator 提供的可视化波形输入编辑平台 TBW(Test Bench Waveform)下,编辑仿真波形。其中密钥部分:

明文部分:

加密结果:

密文为

69c4e0d86a7b0430d8cdb78070b4c55a,与文档中给出的完全一样,说明加密电路正确。将密文 69c4e0d86a7b0430d8cdb78070b4c55a 作为输入,进行解密仿真,仿真结果为:

与输入的明文一样,说明 AES 模块能够进行正确的加解密操作。

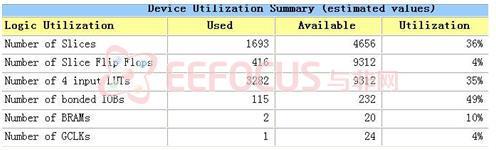

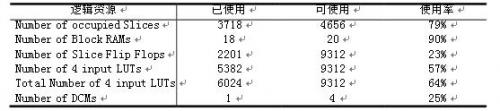

下面是 ISE 中 AES 模块编译后的资源消耗情况如表 7-2。

表 7-2 AES资源消耗表

其中逻辑资源使用了 1688 Slices,占整个可用资源的 36%,存储资源用了 2 块 RAM,占全部可用量的 10%。关于 AES 的 VHDL 实现已经有了不少研究成果,在此做一个比较。电子科技大学的刘珍桢在其硕士论文《AES 加、解密算法的 FPGA 优化设计》一文中介绍了他的设计。他的设计是基于 ATERA 公司的 Stratix 系列 FPGA 芯片,在 QUARTUSII 环境下实现的。资源消耗情况如下:

Total logic elements: 30626

Total memor y bits: 231544.

将本模块同样放到 QUARTUSII 环境下进行编译,资源消耗情况如下:

通过比较发现,本模块 在资源消耗方面有明显的优势,这是以牺牲加解密速 度获得的。

刘珍桢的设计中,每 5 个时钟周期即可完成一次加密或解密运算,而本模块则需要 80 个时钟周期。本模块在 50MHz 的系统时钟下,最高可达 10MByte/s 的加解密速度,完全能够满足需求。由 此可 见 ,AES 模 块 的设 计 在速 度与 资 源消 耗 上取 得了 很 好的 平 衡。 既适 当利 用 了FPGA 片上资源,也很好满足了应用需求。

7.4 作品整合测试

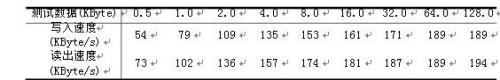

将作品插到电脑 USB 端口,再将 U 盘连接到本作品。在正确输入指纹之前,电脑不显示 U 盘盘符。正确输入指纹后,开始显示盘符,电脑与 U 盘可以正常通信。传输速率测试结果如下表:

再将加密后的文件重新 拷贝到电脑上,打开后与原文件一样,作 品加解密运算正确。将加密后的 U 盘直接连到电脑上,电脑无法读写 U 盘中的数据。

通过以上测试,作品完全能够正确完成加解密运算,有效识别指纹,为 U 盘提供可靠的保护,完全实现了预期目标。

7.5 开发板资源资源利用情况

本 作 品 充 分 利 用 了 开 发 板 上 的 资 源 。 FPGA芯 片 、 Platform Flash 、 LCD显 示 屏、push-button switchesHirose FX2 、expansion connector 等资源得到了合理利用,并且开发了外扩电路板。其中,FPGA 芯片内部自用利用率见下表:

8 作品功能特色与应用前景

8.1 功能特色与创新

8.2 技术难点

在作品的完成过程中,我们遇到并解决了以下难点:

1 USB 协议解析

2 AES 的 VHDL 实现,权衡资源利用率和加解密速度

3 磁盘分区加密技术在本作品中的应用

4 设备对各种 U 盘的通用性

8.3 应用前景

作品拥有广阔的应用前景,能为私人、企业、政府等机构提供便捷、可靠的 U 盘安全解决方案。加密器与 U 盘相分离,减小指纹信息泄露的威胁,在需要保密的部门更便于安全上的管理,因此将大受欢迎。

评论