基于FPGA的速度和位置测量板卡的设计与实现

摘要:针对增量式光电编码器经典速度测量算法M/T法低速采样时间过长和位置测量算法精度不高的问题,本文基于定采样周期M/T法设计实现了速度和位置测量板卡。采用Xilinx公司的XC3S400 FPGA为核心控制芯片进行设计,并设计PC104总线接口实现板卡与控制器的数据通信。该板卡接收处理光电编码器的反馈脉冲得到速度和位置参数,将数据通过PC104总线接口传递给控制器。实验表明,板卡的最小采样时间达到1ms,并且位置测量精度可达5×10-3。

本文引用地址:https://www.eepw.com.cn/article/201610/308996.htm增量式光电编码器作为速度和位置传感器被广泛应用于伺服系统。理论上,光电编码器反馈脉冲的频率对应被测轴转速,反馈脉冲个数的累加值对应位置信息。经典的速度测量方法有M法、T法和M/T法3种:其中M法通过计取固定时间间隔内光电编码器的反馈脉冲数计算当前转速,适用于高速场合;T法利用高频脉冲测量相邻反馈脉冲的时间间隔计算当前转速,适用于低速场合;M/T法不仅测量固定时间间隔内反馈脉冲的增量值,而且计数该时间内的高频脉冲数。虽然M/T法克服了M法和T法测速范围有限的缺点,在高速和低速段都具有较高的分辨率及较低的测速误差,但是存在低速采样时间过长等问题。经典的位置测量方法按转向的正负对反馈脉冲进行增减计数,然后将计数值乘以脉冲当量K得到当前位置信息,可见其测量精度取决于脉冲当量。

本文以定采样周期M/T法为基础,它解决了经典M/T法低速检测时间过长的问题,保证每一固定周期都能采样到数据。此外,该算法充分利用反馈脉冲的位置信息和时间信息,得到了比一个脉冲当量K更为精确的位置信息。本文利用FPGA设计实现定采样周期M/T法,并设计PC104总线接口满足板卡与控制器数据通信的要求。

1 总体方案

速度和位置测量板卡接收光电编码器的反馈脉冲信号,通过差分电路将其转换为单端信号消除共模干扰,然后在FPGA中对脉冲处理得到速度和位置参数,最后将参数通过PC104数据接口传递给控制器。速度和位置测量板卡除差分电路以外的功能均通过FPGA设计实现(如图1所示),因此FPGA是本板卡的核心芯片。速度和位置测量板卡主要包括倍频辨向模块、定采样周期M/T法模块和PC104数据接口模块。

1. 1 倍频辨向模块

光电编码器的输出反馈脉冲包括相位差90°的A、B信号以及零位脉冲Z。A、B之间的相位关系标志被测轴的转向,即A相超前B相90°表示正转,滞后90°表示反转;Z脉冲起到参考零点的作用。一个周期内A、B两路信号的相对位置变换了4次,即正转A、B按00-10-11-01循环输出,反转遵循00-01-11-10的规律。倍频辨向模块通过检测A、B信号的状态变化输出四倍频及方向信号,不仅提高了速度和位置测量的精度,还起到抗干扰的作用。

1.2 定采样周期M/T法模块

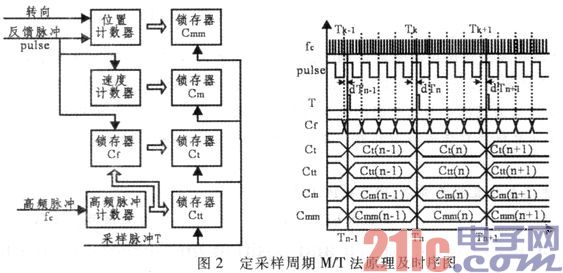

定采样周期M/T法模块分为速度测量电路和位置测量电路两部分,图2给出了该算法的硬件原理及时序图。定采样周期M/T法对高频脉冲fc两级锁存的设计确保实际检测起始点Tk超前于采样周期Tn,这解决了M/T法在低速时检测时间过长的问题,保证每个采样周期内都能成功采集到数据。

速度测量硬件电路由速度计数器及其数据锁存器Cm,以及高频脉冲计数器及其两级数据锁存器Cf和Ct构成;其中速度锁存器Cm和高频脉冲锁存器Ct由采样脉冲触发,辅助高频脉冲锁存器Cf由反馈脉冲触发。通过差分处理得到当前周期Tn内的转速增量Cm和高频脉冲增量Ct,并设高频脉冲的频率为fc,脉冲当量为K,那么计算可得转速为:

Vn=KxfcxCm/Ct

位置测量硬件电路同样采用高频脉冲的两级锁存设计,除此之外还包括位置计数器及其数据锁存器Cmm,以及辅助位置锁存器Ctt。由图2可知,dTn-1和dTn这两个时间差所对应的位置变化小于一个脉冲当量K,位置测量算法将上述时间差内的位置变化加入到位置信息中,提高了位置测量的分辨率和精度。dTn通过差分当前周期辅助位置锁存器Ctt和脉冲锁存器Ct得到,接着将dTn乘以速度值Vn可得位置变化。位置锁存器Cmm计取了反馈脉冲的变化值,再加上dTn-1和dTn内位置变化,便能计算出精确的位置信息。

dTn=(Ctt(n)-Ct(n))/fc

S=KxCmm+VnxdTn-Vn-1xdTn-1

2 各个模块Verllog实现

根据速度和位置测量板卡的总体设计方案,利用Verilog设计实现各模块。

2.1 倍频辨向模块

本模块在FPGA系统时钟clk上升沿检测A、B的电平,并与上一clk记录的状态进比较:当状态变化符合00-10、10-11、11-01、01-00时,表明A超前B相90°,并且A或B产生一个边沿跳变,此时光电编码器正转那么置1方向信号,同时输出一个计数脉冲,这样一个周期内将产生4个计数脉冲实现了四倍频;当变化对应00-01、01-11、11-10、10-00时,标志A滞后B相90°,光电编码器反转则清零方向信号,并输出一个计数脉冲;当变化符合00-00、01-01、10-10、11-11时,说明光电编码器处于换向阶段,或者对应正反转的中间状态,此时保持方向信号并且不输出计数脉冲;当变化为00-11、01-10、10-01、11-00时,说明A、B信号受到干扰而产生了错误的状态翻转,此时保持方向信号并且不输出计数脉冲,达到了抗干扰的目的。

2.2 定采样周期M/T法模块

分析定采样周期M/T法模块可知,它主要由计数器和锁存器组成,其中计数器对脉冲个数进行计数,得到的计数值存于锁存器中等待数据接口模块读取。

按计数方式的不同,计数器又可细分为增计数器和可逆计数器。其中高频脉冲计数器和速度计数器都采用增计数,在检测到计数脉冲有效时加1计数值。位置计数器采用可逆计数的方式,在计数脉冲有效时通过方向脉冲决定采取增或减计数。由于对增量式光电编码器的反馈脉冲计数只能获得转台的相对位置,因此在计数器断电或控制系统上电之前,都要对计数器所存数值进行校正,即归零。为了实现归零操作,计数器除可逆计数外还需具备清零以及置数等功能。

锁存器在采样脉冲T有效时,锁存当前数据供接口电路读取,其中采样周期大小取决于控制器对速度和位置的读取频率。考虑到数据读取的安全性,控制器读操作前必须首先完成各锁存器的数据锁存工作,即通过控制器对板卡的写信号产生采样脉冲T触发锁存器的锁存工作。

本模块设计了4个双字锁存器暂存速度和位置参数,因此开辟4个双字的I/O地址空间。控制器对I/O地址的读操作实现锁存器数据的读取,写操作为板卡提供清零、置数及采样脉冲等信号。

2.3 PC104数据接口模块

PC104总线是一种专为嵌入式控制而定义的工业控制总线,它具有小尺寸结构、抗震性极佳的堆栈式连接、低功耗总线驱动等优点,广泛应用于机载设备的开发中。此外,它是一个8位和16位兼容的总线,本模块采用8位总线方式,采用以下总线信号完成通信设计:SD7~SD0:数据信号;SA9~SA0:地址信号;AEN:地址使能信号;IOR:I/O读信号;IOW:I/O写信号;电源信号。

在PC104系统中,为防止I/O地址冲突,每个模块都必须有一个单独的基地址。速度和位置测量板卡采用10位地址译码,基地址通过板卡上的基地址跳线器进行设置。PC104数据接口采用I/O读写方式进行通信,利用状态机设计实现本模块如图3所示。S0为空闲状态,此状态为初始状态,一旦控制器对板卡进行操作,则进入S1状态。S1状态记录控制器的地址、数据以及控制信号,并判断控制器的操作类型。如果是读操作进入S2状态,若是写操作则进入S3状态。在S2状态中,将对应地址的数据给到数据线,完成读操作。在S3状态,将数据写入对应地址中,完成写操作。读操作或者写操作完成之后,状态又重新回到S0,等待控制器下次读写。

下面结合PC104的信号说明各状态的作用。S0状态检测地址使能信号AEN,当AEN有效并且地址信号SA的高位与基地址一致,说明控制器对本板卡操作,则激活S1状态。S1状态记录地址信号SA的低4位和数据信号SD,并判断读信号IOR或写信号IOW是否有效。当IOR有效说明目前进行读操作进入S2状态,而IOW有效表明当前为写操作进入S3状态。S2状态对地址进行分支选择确定欲读取数据的地址,输出对应地址的数据完成读操作。S3状态将数据写入到对应地址完成写操作。

3 测试平台与仿真测试

用ISE软件编程实现各模块的功能,用ModelSim对其进行仿真测试,图4为仿真结果。由图可知,输入的A、B信号模拟正转、反转及干扰三种状态,正转和反转下每周期都将输出四个脉冲,并且正转方向信号置1,反转清零,而在干扰信号下不输出计数脉冲,并且方向信号保持不变。速度计数器在计数脉冲有效时计数,位置计数器根据方向信号对计数脉冲做增减计数,速度锁存器Cm、位置锁存器Cmm在采样周期有效时锁存速度和位置值。辅助高频脉冲锁存器Cf及高频脉冲锁存器Ct对高频脉冲进行两级锁存,保证实际采样点超前于采样周期,保证每个周期下都能采样到数据。

设计完成的速度和位置测量板卡如图5所示,FPGA采用Xilinx公司的XC3S400,控制器部分选用盛博公司的SAT-1040板卡。使用36000刻线的增量式光电编码器,高频脉冲由40 MHz晶振提供,最小采样周期可达1ms,在测量范围内速度、位置测量精度分别达到3x10-5、5x10-5。

4 结束语

文中以FPGA为核心控制芯片设计实现了速度和位置测量板卡,它以定采样周期M/T法为基础对光电编码器的反馈脉冲处理得到表征速度和位置的参数,通过PC104总线接口将数据传递给控制器计算得到精确的速度和位置信息。整个设计在FPGA内完成,故硬件结构简介,可靠性强,抗干扰能力强;板卡的最小采样时间达到1 ms,确保每一周期下都能采样到可靠数据,并将位置测量精度提高至5x10-5。

评论