基于FPGA的GPS数据采集器的设计与实现

全球定位系统(Clobal Position System,GPS)能够提供实时、全天候、全球性和高精度的服务,其广泛应用于各行各业中。GPS接收机通过天线单元接收卫星信号,将信号进行带通滤波、下变频混频、AGC放大、A/D转换等一系列处理,得到数字中频信号,进而对中频信号进行捕获、跟踪,解调出用户的纬度、经度、高度、速度、时间等导航信息,将这些信息按NMEA-0183协议封装,通过串口输出数据。用户设备中的GPS接收器在收到GPS信息后,需要对相关信息予以解码处理,从而得到用户的位置、时间等信息,进而实现用GPS导航和定位的目的。近几年来,现场可编程门阵列(FPGA)凭借其开发过程投资少、设计周期短、灵活方便以及可反复编程等特点,在现代电子设计中得到了广泛应用。本设计选择现场可编程门阵列(FPGA)来实现GPS信号的解析处理。

本文引用地址:https://www.eepw.com.cn/article/201610/308358.htm1 NMEA-0183协议的数据格式

NMEA-0183是美国国家海洋电子协会(NMEA,The National Marine Electronics Association)为海用电子设备制定的标准格式,它现在已被广泛地应用于多个领域的设备之间的数据传输。NMEA标准格式输出采用ASCII码,每个ASCII数据码长8位,串行通信的波特率为9600位/秒,数据位8位,开始位1位,停止位1位,无奇偶校验位。

NMEA-0183协议由语句组成,每条语句以字符“$”作为语句起始标志,数据之间以逗号相隔,字符“*”作为校验和前缀,最后以校验和数值和回车/换行字符结束。最常用的有6种语句格式:$GPGGA,$GPGLL,$GPGSA,$GPGSV,$GPRMC,$GPVTG。下面以推荐定位信息GPRMC语句为例介绍数据格式。语句的格式如下:

$GPRMC,1>,2>,3>,4>,5>,6>,7>,8>,9>,10>,11>,12>*13>

1>UTC时间,格式hhmmss.sss(时分秒);

2>定位状态,A=有效定位,V=无效定位;

3>纬度,ddmm.mmmm(度分)格式(前导位不足则补0);

4>纬度半球N(北半球)或S(南半球);

5>经度,dddmm.mmmm(度分)格式(前导位不足则补0);

6>经度半球E(东经)或W(西经);

7>地面速率(000.0~999.9节,前导位不足则补0);

8>地面航向(000.0~359.9度,以真北为参考基准,前导位不足则补0);

9>UTC日期,ddmmyy(日月年)格式;

10>磁偏角(000.0~180.0度,前导位不足则补0);

11>磁偏角方向,E(东)或W(西);

12>模式指示(仅NMEA-0183 3.00版本输出,A=自主定位,D=差分,E=估算,N=数据无效);

13>校验和;

2 NMEA-0183协议解析器设计

2.1 系统的总体设计

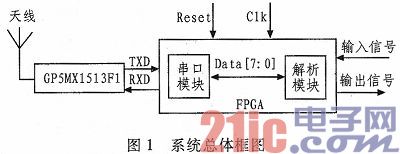

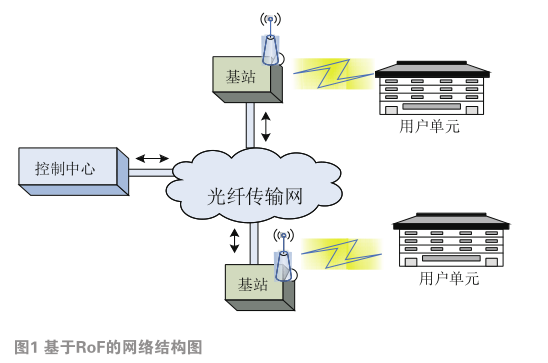

以深圳星际通公司生产的GP5MX1513F1导航芯片为例进行说明。该芯片为一个64并行通道单频接收机,只接受L1波段的卫星信号,定位精度2 m(2D RMS)。该芯片依次输出6种NMEA信息,分别是:$GPGGA,$GPGLL,$GPGSA,$GPGSV,$GPRMC,$GPVTG,串口默认设置:波特率9 600bps,起始位1位,数据位8位,无奇偶校验位,停止位1位。NMEA-0183协议解析系统的总体设计框图如图1所示,GP5MX1513F1导航芯片通过天线单元接收卫星信号,将信号滤波、下变频、放大和模数转换等一系列处理,得到数字中频信号,进而对中频信号进行捕获、跟踪、位同步及帧同步,解调出导航数据,最后计算出用户的纬度、经度、高度、速度、时间等信息,以NMEA-0183协议格式打包成数据帧,再通过标准的串口输出数据。NMEA-0183协议解析模块生成的硬件电路内嵌在FPGA中,一方面通过串口模块接收GP5MX1513F1芯片发出的串行数据,将接收的信号给解析模块进行处理,另一方面解析模块根据NMEA-0183协议的数据格式提取出所需要的信息。

2.2 串口模块

串口模块主要负责接收由GP5MX1513芯片输出的导航定位信息,串口模块通过波特率发生器将系统时钟进行分频,产生16倍数据波特率的时钟。系统复位后,接收端以16倍波特率的速率读取线路状态,检测信号GPS_TX出现下降沿,在GPS_TX信号下降沿后第8个采样点确认是否为低电平,如果检测得到的是高电平,则认为起始位无效,返回到空闲状态,重新等待起始信号的到来。起始位找到后,开始接收数据,当数据计数器data_bit_cnt计到7时,8位数据都已经输入完成。最后,检测停止位,如果正确检测到高电平,则

说明本帧的各位数据正确接收,将数据存入到8位数据寄存器中,否则出错。

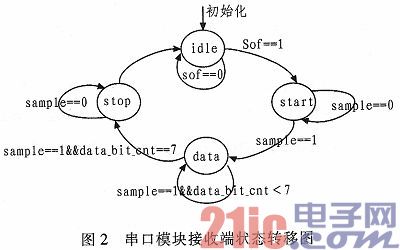

串口模块接收端的状态转移图如图2所示,接收机由4个工作状态组成,分别是空闲状态、起始位、数据位和停止位。当系统复位后,电路处于空闲状态,等待信号的触发,连续8个时钟检测出数据发生负跳变,sof信号为高,进入起始状态,当sample为1时,进入数据位,接着的数据位将每隔16个采样周期被采样一次。即取每一位的第8次的波特率时钟采样值来确保采样正确。连续采样8次后,采样计数器data_bit_cnt==7,进入停止位,当sample为1时,进入空闲状态,开始接收下一个数据。

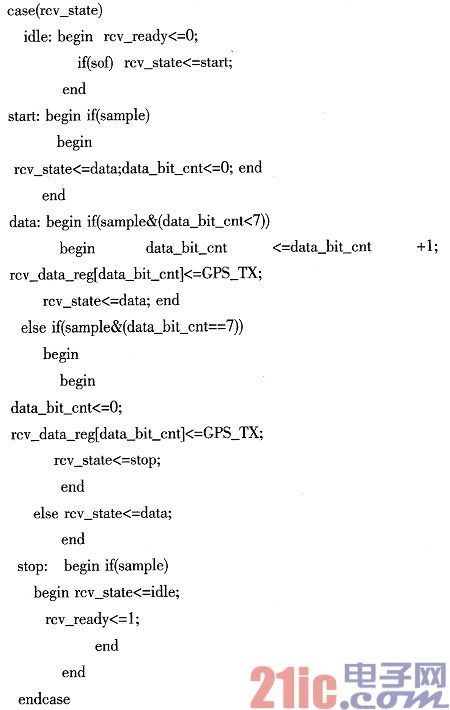

在状态机模型的基础上,使用verilog HDL语言来描述其功能,其主要代码如下:

2.3 解析模块

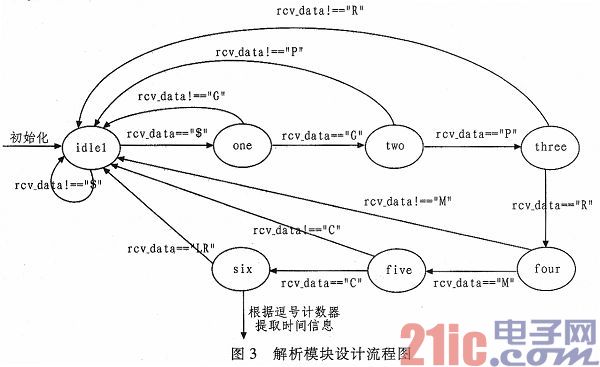

串口模块输出的8位数据送到解析模块,解析模块采用6MUX1选择器来选择提取哪种语句,通过外部输入信号对寄存器config_Reg进行配置来实现,当config_Reg=000时,提取GGA语句,当config_Reg=001时,提取GLL语句,当config_Reg=010时,提取GSA语句,当config_Reg=001时,提取GSV语句,当config_Reg=011时,提取RMC语句,当config_Reg =100时,提取VTG语句。下面以RMC语句为例,来说明解析过程,解析模块将串口模块接收端接收的数据进行循环检测,判断报文头、定位状态、校验位、结束位信息,提取时间信息。首先,对config_Reg进行配置,设置config_Reg=011;其次,检测报文头$GPRMC,如果是,则进行下一步,否则,继续检测;最后,用逗号计数器的值来决定提取$GPBMC语句的哪段信息,当逗号计数器为1时,提取时分秒信息,存储在data_hh_mm_ss寄存器中;当逗号计数器为2时,提取定位状态信息,当VALID信号为高,则有效定位;当VALID信号为低,则无效定位;当逗号计数器为3时,提取纬度信息,存储在lat_data寄存器中;当逗号计数器为5时,提取经度信息,存储在lon_data寄存器中;当逗号计数器为9时,提取日月年信息,存储在data_dd_mm_yy寄存器中。程序设计的流程图如图3所示。

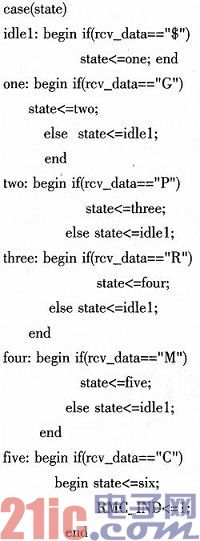

其主要代码如下:

3 仿真测试及硬件实现

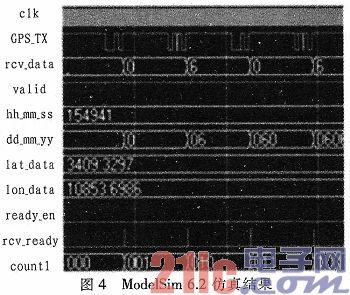

根据编写的测试模块在ModelSim 6.2软件下进行了功能仿真,其仿真结果如图4所示,GPS_TX为输入的串行数据,rcv_data为接收的8位数据,hh_mm_ss为提取出时分秒信息:15:49:41,dd_mm_yy为提取出日月年信息:13.06.09,lat_data为提取的纬度信息:3409.3297,lon_data为提取的经度信息:10853.6986,从仿真波形上看,仿真的结果与测试激、励中的数据一致。

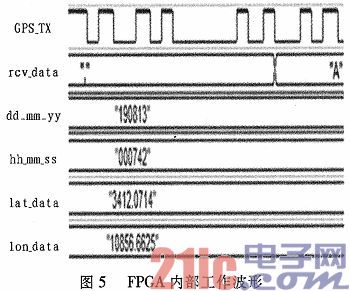

完成了仿真后,在Quartus II 9.0下进行了逻辑综合,将程序下载到Altera公司生产的CycloneII系列EP2C5T144C8型号的FPGA中,用Quartus II 9.0软件自带的嵌入式逻辑分析仪SignalTapII,对FPGA内部的信号进行观测,FPGA内部实际工作波形如图5所示,从硬件调试结果观测,实际测出的结果:年月日2013.08.19,时分秒00:07:42,纬度为3412.0714,经度为10856.6625。由于所测得时间信息为世界协调时间,北京时间与世界协调时相差8个时差,北京时间应修正为:08:40:09,所测得结果与本地的时间一致。

结果分析:从图4和图5波形上可以看到我们测试的结果,实际测试中,我们让整个解析过程连续工作12 h,没有发现解析错误、丢包等不正常现象。因此,大量测试结果表明,该模块能够正确的接收和处理导航信息。

4 结论

根据NMEA—0183协议格式,提出使用FPGA实现NMEA-0183信息解析的一种方法,仿真及实际测试结果表明,该电路能够正确地提取出所需要的信息,如时间、位置等信息,最终实现了GPS数据采集及处理等工作,为搜查救援、事故定位等工作提供了技术依据。

评论