基于DSP Builder的CIC梳状滤波器的设计

摘要:CIC梳状滤波器具有结构简单、规整,占用存储量小,不需要乘法器,实现简单且速度高等特点,在高速抽取或插值系统应用广泛。采用DSP Builder软件工具,在Simulink平台上构建了一级4阶CIC梳状滤波器仿真模型,通过多种EDA工具仿真与分析,最终在EP2C35F484C8型FPGA得到了最高响应速度为138.89 MHz的高速CIC梳状滤波器,其性能远优于DSP通用处理器的实现方式。

本文引用地址:https://www.eepw.com.cn/article/201610/308186.htm0 引言

CIC(Cascade Integrator Comb)滤波器最早由Hogenauer提出,后来出现了很多改进的结构形式。随着芯片技术的快速发展、多相滤波技术的广泛应用以及无线通信市场的迅速成长,CIC低通滤波器得到了广泛的应用。长期以来,CIC梳状滤波器一般是在通用DSP处理器上实现的,由于DSP处理器的顺序执行特性的限制,其速度很难满足一些高速抽取与插值系统的需要。FPGA具有优良的全硬件并行执行的特性,研究CIC梳状滤波器的设计及其FPGA实现具有重要的现实意义。

本文采用DSP Builder建模的方法,研究一级4阶CIC梳状滤波器及其FPGA实现方法,为CIC梳状滤波器设计及其FPGA实现的研究提供了一种新的思路。

1 CIC梳状滤波器原理

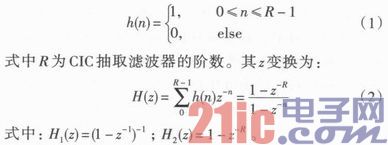

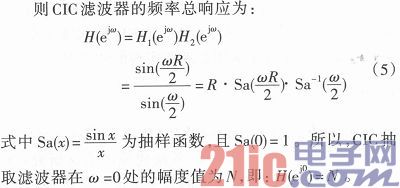

CIC滤波器冲激响应如式(1)所示:

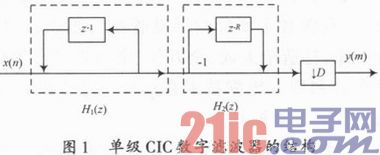

单级CIC数字滤波器的结构如图1所示。

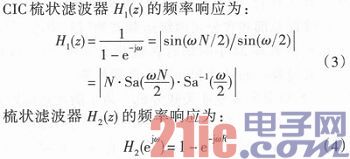

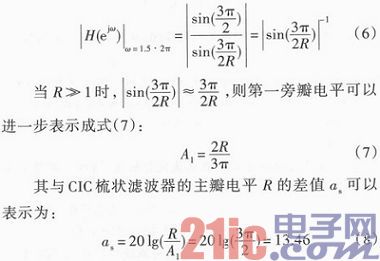

频率区间(0~2π/R)为CIC数字滤波器的主瓣,其他区间称为其旁瓣。不难看出,随着信号频率的增大,CIC数字滤波器的旁瓣电平不断减小。其中,第一旁瓣电平表达式如式(6)所示:

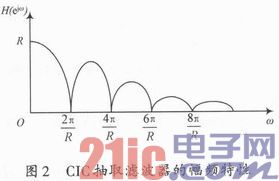

图2是CIC抽取滤波器的幅频特性,可见,单级CIC滤波器的旁瓣电平比较大。

2 基于DSP Builder的FPGA开发方法

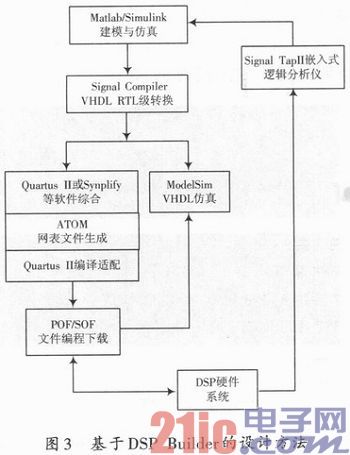

图3是利用DSP Builder软件工具来开发FPGA的基本流程。设计第一步是建模,主要是调用DSPBuilder软件中的元件构建数字系统模型。之后对建立的模型进行仿真测试。

仿真通过之后再运行Signal Compiler信号编译器将模型转化成寄存器传输级硬件描述语言。然后利用QuartusⅡ软件进行编译、逻辑综合、适配(结构综合)及时序网表提取等操作,最后生成编程文件和时序网表文件。最终再下载到FPGA/CPLD芯片上进行硬件测试。

3 CIC梳状滤波器建模

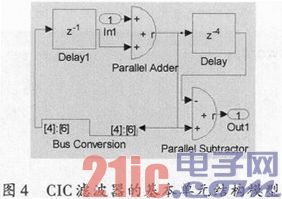

调用DSP Builder工具包中的模块,构建了CIC滤波器单元结构模型,如图4所示。CIC梳状滤波器主要由加减法器和延迟单元组成。

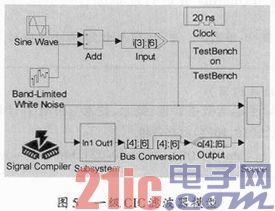

将基本单元模型封装成一个子系统,构建一级CIC树状滤波器仿真模型如图5所示。滤波器输入信号由典型的正弦信号叠加白噪声组成,经一级CIC梳状滤波器后送示波器输出结果。

4 仿真与结果分析

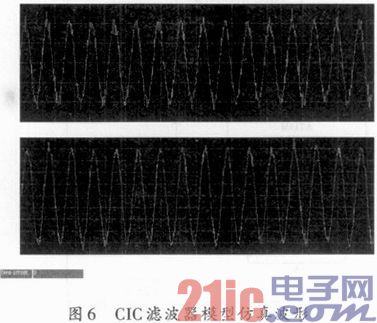

图6是CIC梳状滤波器模型仿真结果,其中图6(上)为梳状滤波器输入信号波形,图6(下)为输出信号波形。可以看出,经过一级CIC梳状滤波器后,输入信号中的高频噪声得到了较好的抑制。

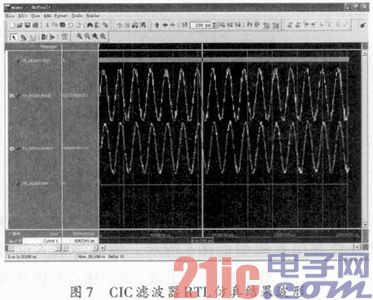

模型仿真通过以后,运行Signal Compiler信号编译器,将模型转换成VHDL语言程序,产生测试向量文件,然后用ModelSim进行寄存器传输级仿真,仿真结果如图7所示,可以看出,RTL寄存器传输级仿真结果与Matlab中模型仿真结果基本一致,进一步验证了模型的正确性。

再调用QuartusⅡ进行逻辑综合与适配,最终在Altera公司CycloneⅡ系列EP2C35F484C8型FPGA上得到了最高响应频率为138.89 MHz的CIC梳状滤波器,其性能远高于采用DSP通用处理器实现的滤波器。

5 结语

CIC梳状滤波器的设计及其FPGA实现具有重要的意义。本文采用DSP Builder系统建模的方法研究CIC梳状滤波器的设计具有重要的参考价值。当然,本文只研究了一级四阶CIC梳状滤波器的性能,在实际应用中,可以根据需要进行二级或者多级级联,以提高CIC梳状滤波器的整体性能。

评论