基于FPGA的TS流的UDP封装实现

摘要:为实现数字广播接收机输出的传输(TS)流方便地接入嵌入式平台,实现综合业务接收,本文基于现场可编程门阵列(FPGA),实现了将集成DVB-T(Digital Video Broadcasting-Terrestrial)高频头输出的TS流转化为UDP协议的IP流,进一步通过以太网接口进入嵌入式平台,支持综合业务接收。该接口转化模块借助FPGA,将缓存的TS流进行有效封装,设置以太网接口,输出UDP格式的IP流。实测表明,该接口转换模块可实现TS流到IP流的转换,支持嵌入式平台视频播放与综合业务接收。

本文引用地址:https://www.eepw.com.cn/article/201607/294698.htm引言

在互联网高速发展以及三网融合的趋势逐步推进的背景下,地面数字电视广播与互联网的融合得到了研究人员越来越多的重视。地面数字电视广播[1]音视频数据的传输流是编码格式为MPEG-2(Moving Picture Experts Group-2)的TS(Transport Stream)流。因此,传统广播接收机多输出TS流。

为支持嵌入式平台实现TS流传输的综合业务接收,本文在前期实现的数字广播接收机的基础上[2],采用FPGA作为转接,实现了TS流到IP流的封装,从而可以方便地将TS流接入嵌入式平台,实现利用嵌入式平台的基于TS流的综合业务接收。

1 硬件系统结构

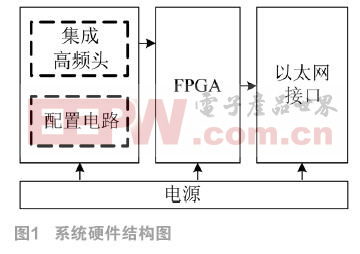

硬件系统主要包括电源部分、集成高频头[3]及其配置电路部分、FPGA部分和以太网接口输出部分。其工作原理如下:系统启动之后,由配置电路中单片机首先对集成高频头进行配置,然后FPGA等待接收由集成高频头输出的数据,接收的数据经过格式封装后,经以太网接口模块以UDP格式[4]的IP流输出。输出的负载数据为MPEG-2标准的TS包,可以在任何支持该标准解码的终端进行实时播放。

系统的硬件结构如图1所示,系统实现的是以FPGA为控制核心的接收、处理和转发系统,下面介绍每个部分的具体实现。

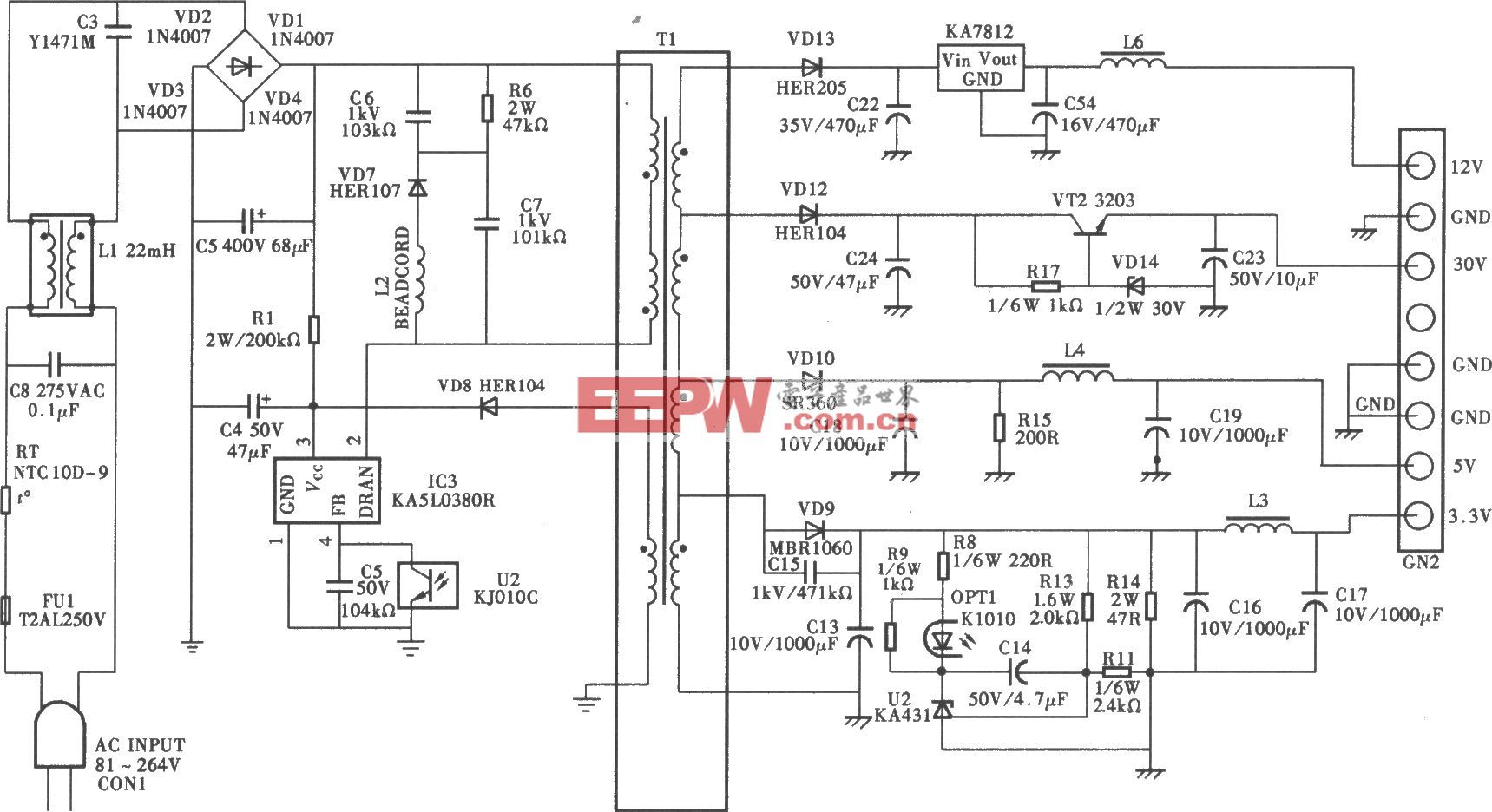

(1)电源部分

电源部分采用TI公司的LP3906电源管理芯片,该电源芯片被广泛应用于低功耗FPGA、嵌入式微处理器、DSP等系统的电源管理。其性能优秀,最高输出效率为96%,最大输出电流为1.5A。该芯片的输入电压为5V直流,由外部电源适配器提供。

(2)集成高频头及其配置电路部分

本部分电路由集成高频头以及其配置电路组成。集成高频头采用夏普公司的VA4M1EE6159。该器件功能是将天线接收到的DVB-T标准信号变频为中频信号[5],通过解调、基带处理和打包,最终输出TS(Transport Stream)流[6]。TS流输出有两种常用接口,分别是异步串行接口(ASI,Asynchronous Serial Interface)和同步并行接口(SPI,Synchronous Parallel Interface),VA4M1EE6159采用同步并行接口,该接口共有11位信号线,包括3位控制信号线和8位数据信号线。3位控制信号分别为时钟信号MCL、同步信号SYN和数据有效信号VALID。其中,集成高频头的时钟信号MCL输出为9MHz。SPI接口使用同步控制信号,所以传输速率由实际情况决定。

配置电路采用Silicon Lab公司的C8051F120单片机作为集成高频头的配置电路控制器。该款单片机兼容8051单片机的指令集,速度是普通8051单片机的数十倍,外部无源晶振为25MHz,最高速度可达100MIPS(百万指令集每秒),支持JTAG(Joint Test Action Group)调试接口。该单片机具有较高处理速度,对于实现严格时序有很大的优势。

(3)FPGA部分

FPGA部分由FPGA电路及其配置电路组成。FPGA采用的是Xilinx公司的Spartan-3系列XC3S700A芯片。该芯片最大用户I/O数量为372,具有分布式RAM为92kb、块RAM为360kb,拥有8个数字时钟管理单元(DCM,Digital Clock Manager),slice数量为5888。配置模式为JTAG模式和主串(Active Serial)模式。采用的存储芯片是XCF04S,存储空间为4M,外部为50MHz无源晶振。

FPGA是系统的控制和计算核心[7],负责接收集成高频头的TS流数据,将接收的数据缓存、计算、打包,并驱动DM9000AEP芯片,将处理完成的数据以IP数据报的形式输出。FPGA芯片使用11个通用I/O与集成高频头相连,模拟SPI接口时序接收数据。作为DM9000AEP的驱动源,FPGA的物理管脚与DM9000AEP连接,用于按其控制时序驱动芯片工作。

(4)以太网输出部分

以太网输出部分使用的是10M/100M自适应的MAC层接口芯片DM9000AEP。该芯片是支持物理层自协商,支持IEEE802.3u全双工流量控制的快速以太网接口控制器。输出物理接口与RJ45相连。该以太网控制器使用的是25MHz的无源晶振,外部电路简洁。

DM9000AEP拥有4K双字大小的SRAM块,可以作为以太网帧结构的缓存。由于以太网帧结构最大为1500字节,所以可以缓存多个相同的帧结构。DM9000AEP有两个方面的功能。首先是完成与后级网络设备的物理层协商,建立链路;其次是接收FPGA的指令,执行指令、发送已经存在于缓存中的以太网帧以及完成相关链路层功能。

系统硬件电路由LP3906模块提供统一的电源管理。集成高频头在配置电路完成配置之后,与天线相连,从天线接收DVB-T信号并将信号解调处理,以SPI接口输出TS流,是整个系统的数据源。FPGA是系统中枢,它模拟SPI时序接收TS流数据并打包为UDP格式,控制DM9000AEP以IP流输出。DM9000AEP完成与接收者的物理链路建立及辅助的链路层功能。

2 基于FPGA的封装转发实现

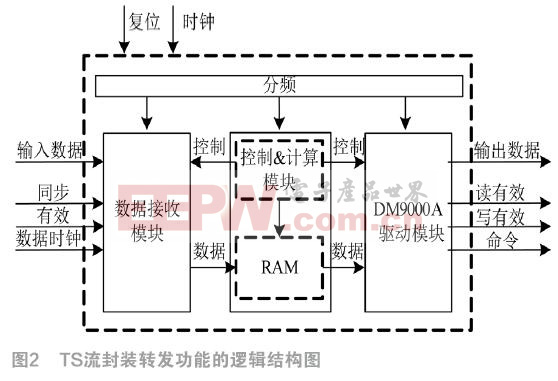

在系统实现过程中,TS流的接收、处理和转发部分都在FPGA内部实现。图2为FPGA实现的封装转发功能的逻辑结构图。主体由数据接收模块、控制计算模块和DM9000AEP驱动模块三个模块组成。数据接收模块模拟SPI接口时序接收集成高频头的输出数据;控制计算模块负责将接收的数据有序地存入RAM,并将RAM中的数据打包为IP格式;DM9000AEP驱动模块将IP格式的数据通过网口输出。

2.1 数据接收模块

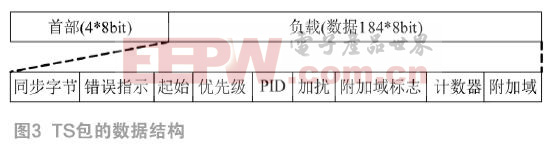

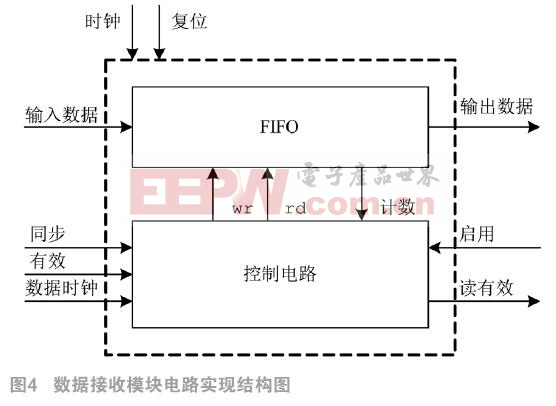

数据接收模块的功能是模拟SPI接口时序接收由集成高频头输出的TS流格式的数据。集成高频头数据输出宽度为8bit,接口时钟频率为9MHz。当有数据输出时,有效信号变为高电平。输出的TS流数据包含有4字节的首部和184字节的数据,总计大小为188字节,数据格式如图3所示。

TS流数据输出为突发模式,即在一个周期内只有小部分时间有数据输出,大部分时间没有数据输出。突发瞬时速率最高可达到72Mbps,这里的72Mbps为裸数据,增加数据头部等,最高瞬时速率将会增加到80~85Mbps之间。DM9000AEP的理论最高速率为100Mbps。由于在DM9000AEP的驱动中有额外开销,数据很难做到最大带宽。所以使用FIFO作为缓冲来匹配前后两者的速率差,既可以防止数据丢失,也方便进行数据处理。当FIFO中的TS流数据包的数量超过阈值时,则读有效信号为高电平,数据线输出数据。本部分电路实现的结构图如图4所示。

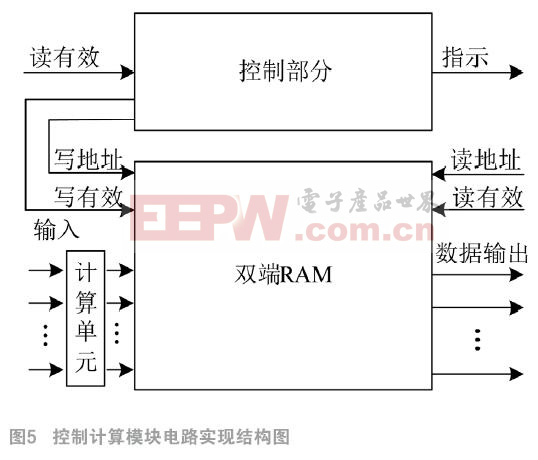

2.2 控制计算模块

控制计算模块由控制部分、计算部分和双端RAM部分组成。本部分电路实现的结构图如图5所示。

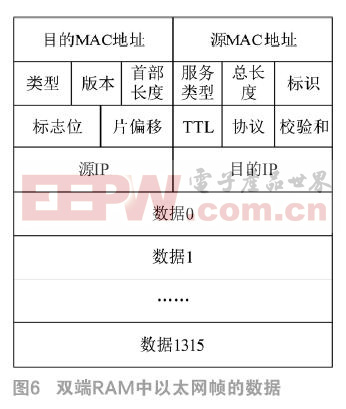

其中,双端RAM内存储一个完整的以太网帧,RAM中不同部分的功能如图6。源MAC地址设置为本机地址,目的MAC地址为广播地址,类型为IP数据报。IP数据报中版本、首部长度、服务类型、标志位、片偏移、TTL、协议、源IP以及目的IP为常量。其中,源IP设置为本机IP,目的IP为广播地址,TTL为64。以太网帧的数据大小范围是46~1500字节。为了最大限度地提高传输效率,取7个TS包作为一个以太网帧的数据部分,即1316字节。

以太网帧中数据段、标识字段和校验字段为变量。数据段由传输的TS流数据决定;标识字段为依次递增;校验字段则是将字段本身置为零之后,对IP数据报中每16比特进行二进制反码求和,将结果存入校验字段。这部分运算在计算部分实现。

控制部分时刻监视读有效信号的状态变化。当发现信号状态变化为有效,则接收前级模块的输出数据,并且按地址存入RAM。与此同时,在数据输入路径上的计算模块对数据进行反码求和运算,得到校验字段,并且进行递增运算,得到标识字段。计算完成后,两个字段分别按地址存入RAM中。此时,RAM中是一个完整的以太网帧结构。控制部分将会给出指示信号,通知DM9000AEP驱动模块可以读取UDP帧数据。

2.3 DM9000AEP驱动模块

DM9000AEP驱动模块通过状态机实现,负责对DM9000AEP芯片进行初始化及功能驱动。

DM9000AEP的初始化过程首先进行物理层(PHY)上电。物理层上电第一步是对DM9000AEP芯片内部的GPR寄存器清零,然后最低位赋值为1。在对物理层上电之后,延时应该超过2ms,最佳为5ms。第二步是将NCR寄存器进行两次软件复位,两次软件复位的目的是确保软件复位成功。每次软件复位延时30μs,正常的时间间隔是20μs左右。然后依次按着时序对NSR、ISR、TCR、BPTR、FCTR、SMCR的寄存器和物理地址进行设置。为了确保数据的通用性,物理地址设为广播地址。寄存器设置成功表示DM9000AEP初始化完成。

初始化完成后的DM9000AEP在检测到控制计算模块的指示信号变化后,在双端RAM的右端进行读取,将RAM中的一个以太网帧数据写入DM9000AEP的buffer中,并查询标志位,直到标志位变化表示发送完成。由于DM9000AEP的发送速度大于集成高频头的数据平均输出速率,所以不会出现双端RAM中数据被重复写的情况。

FPGA部分的三个模块采用的是流式的处理过程。数据接收模块模拟接口时序接收集成高频头的输出数据,是整个FPGA逻辑的数据源。控制计算部分负责对IP数据报进行计算打包,并且将完整的以太网帧存入双端RAM,完成之后通知驱动部分。DM9000AEP的驱动部分负责按时序初始化DM9000AEP,并在得到控制计算模块的通知后,发送双端RAM中的以太网帧。

3 系统测试

为验证系统接收数据的正确性及系统运行的实际效果,对系统进行实测。

发送端采用PC机控制调制卡DTA-115产生符合DVB-T标准[8-9]的调制信号。其中,DTA-115为DekTec公司生产的多制式数字电视调制卡。发射端采用QPSK调制,中心频率为226.5MHz,带宽为7MHz,2K模式,7/8码率,发射功率-3dBm。

数字广播接收系统的数据输出连接至具有MPEG-2解码播放功能的嵌入式平台。单片机设置高频头的对应接收参数,FPGA实现数据处理转发,嵌入式平台实现TS流的解码播放。最后嵌入式平台上测试结果如图7所示。视频流数据可以进行流畅播放。

4 结论

本文利用FPGA实现了集成高频头输出的TS流转换为嵌入式平台可以读取的IP流。系统通过集成高频头接收DVB-T标准[10]广播信号,由高频头完成广播信号的接收,得到TS流数据。利用FPGA实现了高频头输出的突发数据的平滑封装至基于UDP协议的IP数据流。经过测试[11],基于FPGA的封装模块输出的IP流可以在嵌入式平台播放。

参考文献:

[1]杨知行,王军,王昭诚,等.数字电视传输技术[M].北京:电子工业出版社. 2011.

[2]戴军忠,陈为刚,赵玉冰,等. DTMB数字电视接收机电路设计与实现[J].中国科技论文在线,2014-12-12.

[3]Nguyen TT, Dang KL, Nguyen HV, Nguyen PH. A Real-Time FPGA Implementation of Spectrum Sensing Applying for DVB-T Primary Signal [J]. Proceedings International Conference on Advanced Technologies for Communications, 2013:164-169.

[4]史蒂文斯(W.Richard Stevens).TCP/IP详解卷1:协议 [M].北京:机械工业出版社.2000.4.

[5]Gholami M, Rahimpour H, Ardeshir G, MiarNaimi H. A new fastlock, lowjitter, and alldigital frequency synthesizer for DVBT receivers [J]. International Journal of Circuit Theory and Applications, 2015, 43: 566-578.

[6]丁法珂,基于FPGA的PCM-FM遥测中频接收机设计与实现[J].电子产品世界,2015,6:54-59.

[7]张黎明, 高性能数字接收机FPGA设计[J].电子产品世界,2013,5:40-42.

[8]Torio P, Sanchez MG. Reconciling the ETSI coverage requirements for DVBT with the ITUR recommendations[J].Telecommunication Systems, 2014,57:217-222.

[9]DVB Document A122. Digital Video Broadcasting (DVB). Frame structure channel coding and modulation for a second generation digital terrestrial television broadcasting system. v1.3.1 [S]. 2011.

[10]ETSI EN 300 744 V1.6.1 Digital Video Broadcasting (DVB). Framing structure, channel coding and modulation for digital terrestrial television [S]. 2009.

[11]陈为刚,赵干,李思,等. 基于USRP的DVB-T接收机实现 [J]. 电视技术,2014,38(9):155-159.

本文来源于中国科技期刊《电子产品世界》2016年第7期第51页,欢迎您写论文时引用,并注明出处。

评论