基于SATA2.0的高速存储系统设计实现

摘要:本文介绍了一种高速数据存储系统,该系统采用SATA2.0协议,存储介质选择的是Intel公司新型固态硬盘,控制器选择的是Xilinx公司的Viretx-5系列FPGA,以及所提供的软件开发平台ISE和EDK联合开发工具,最后使用ChipScope对系统进行测试。多次测试结果显示,本系统能稳定有效地完成高速数据传输,且存储速度达到800MB/s。

本文引用地址:https://www.eepw.com.cn/article/201606/293258.htm引言

科学技术的快速发展使得人类快速地从网络时代迈入大数据时代,于是人们在社会生活中产生的数据量呈现爆炸式增长,这给数据的存储带来了很大的压力。正是基于这种现状,借助于计算机与电子技术的快速发展,本文提出一种SATA2.0协议的高速大容量数据存储系统,相比于更早的PATA协议具有无可比拟的优势。SATA协议的数据传输模式传输速度比PATA协议更快,将40根数据线简化到7根,并且采取差分传输形式,能有效解决信号间的串扰问题,最长1m的数据线长度扩展使用范围并能支持热插拔[1]。为实现更快的传输速度,本系统还采取磁盘阵列方式进行存储,采用四块固态硬盘组成RAID0模式磁盘阵列。FPGA作为本系统的控制器是实现整个系统的关键,采用EDK的IP核生成工具定制实现SATA协议的IP核,因此数据可以直接从FPGA写入磁盘阵列。

1 SATA协议介绍

SATA概念[2]由Intel公司在2000年提出,随后诞生的SATA1.0协议规定采用串行数据传输模式,速率为1.5Gbps。之后SATA2.0将速率提升到3.0Gbps,并加入NCQ(本地指令列队)、EM(机架管理)等新技术,同时支持热插拔。最新版本SATA3.0传输速率高达6.0Gbps。

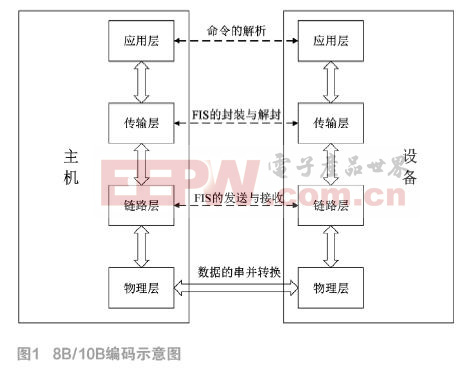

SATA协议从上到下有四层,即物理层、链路层、传输层和应用层[1],其架构如图1所示。

SATA协议中,应用层主要负责的是对所有命令的解析和执行,会根据处理器的要求实现一系列操作,像PIO传输、DMA传输、软件复位以及中断等;传输层主要负责帧的封装和解析,在发送端将要发送的数据按照要求封装成各种类型的FIS,在接收端把接收到的FIS解析成数据;链路层主要负责的是帧的校验和抗干扰处理,将根据上两层传输命令生成原语发送出去,并且接收来自于下一层的原语,将其转换成命令发送给上两层;物理层主要实现与对方物理层建立通信连接,负责差分数据的传输[2]。在发送端从链路层接收数据[1],加入同步字符后对数据做串行化处理,再采用低压差分方式传输。在接收端对低压差分数据进行解串处理以分离时钟与数据,通过同步字符实现数据对齐,最终恢复出发送时的数据。

2 总体方案的设计

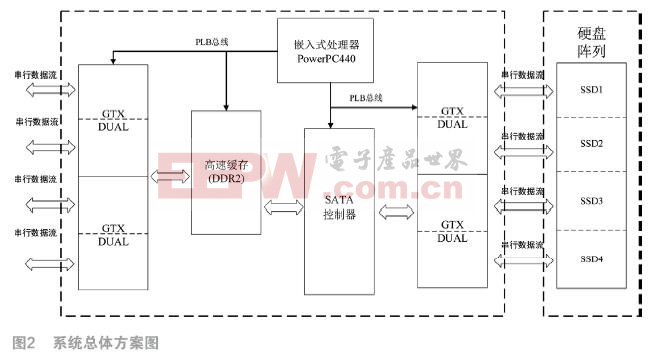

存储系统的整体方案如图2所示,FPGA内部集成两个主频550MHz的PowerPC440处理器,通过PLB总线[4]控制整个系统,数据输入端是四路GTX,参考时钟设置为150MHz,传输数据位为16位,高速缓存是容量1GB的DDR2,SATA控制器实现协议规定的所有功能,包括启动DMA传输模式,把数据封装成帧,进行CRC校验、加扰和解扰处理,最后进行8B/10B编码,数据被串行化后通过四路GTX写入固态硬盘组成的磁盘阵列。

3 存储系统的实现

3.1 通信链路初始化

通信链路建立前需要进行上电复位和电源管理,并对通信模式和传输速率进行配置[1]。因此,双方要建立通信先要进行握手,握手成功后才能建立可靠的连接。SATA协议规定使用OOB信号进行上电复位和电源管理。SATA2.0标准定义了三种OOB信号,即COMRESET、COMINIT和COMWAKE来实现链路初始化。

上电硬件复位后,双方须先初始化,使通信链路都置于空闲状态。对于物理层的初始化,通信双方是利用OOB信号的硬件复位信号使设备端完成复位操作,设备端完成复位后准备建立通信链接(速度协商、时钟恢复等),其上电过程如图3所示。

● 主机/设备端处于断电状态;

● 电源上电,主机端将TX和RX拉到共模电压;

● 主机端就连续发送多个COMRESET信号,然后把总线设置成等待状态;

● 设备端发送COMINIT信号,一旦检测到COMRESET信号,设备端发送COMINIT信号作为响应,无论何时设备端上电完成,都可以发送该序列请求建立连接;

● 主机端校准,主机端接收到COMINIT信号后进行校准,校准完成之后发送COMWAKE信号给设备端作为响应;

● 设备端响应,设备端在其接收端上检测COMWAKE信号并校准发射器;

● 速率协商,双方要进行速率协商,此时主机端以最低速率连续发出D10.2字符,如果设备端能够锁定该速率则速率协商成功,否则重新进行;

● 设备端锁存,假如此时设备端可以建立连接,回复SYNC原语表明设备端允许建立连接。

如果主机端接收到的是三个连续的非ALIGN原语后,这就表明双方连接成功,即可传输数据。

3.2 数据传输过程

数据在SATA协议中传输是以帧(Frame)形式传递[3]。帧由一组Dwords构成,以SOF原语开始,内部含有多个数据,最后一位是CRC校验值,并以EOF原语结束。有时为调节速率,帧中间也会插入一些原语(CONT、HOLD、HOLDA)用来控制流量。帧的典型内部结构图如图4所示。

原语是由双字组成的最简单信息单元,主要用于建立通信链接、传递最新状态和传输控制命令等。原语双字之一是控制字符另外三个字节的存放数据。

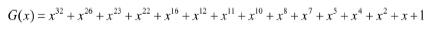

在数据通信过程中,信号会受到各种各样的干扰,因此,在数据发送之前要对数据作校验处理,SATA协议采用的是CRC校验,这要对数据帧中SOF与EOF之间包含的所有数据作循环冗余运算,其计算单位是双字(32bits),如需要计算的数据量不是双字的整数倍,处理方法是在数据的后面添加“0”补成32位。CRC的运算公式如公式(1)所示:

(1)

(1)

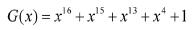

为使数据在传输过程中能更加稳定,要对方法的数据进行加扰,加扰处理的原理就是利用扰码的正交性,一般都采用伪随机序列码。加扰后的信号可以降低噪声对信号的影响,解扰码的原理跟加扰一样。加扰的特征方程如公式(2)所示:

(2)

(2)

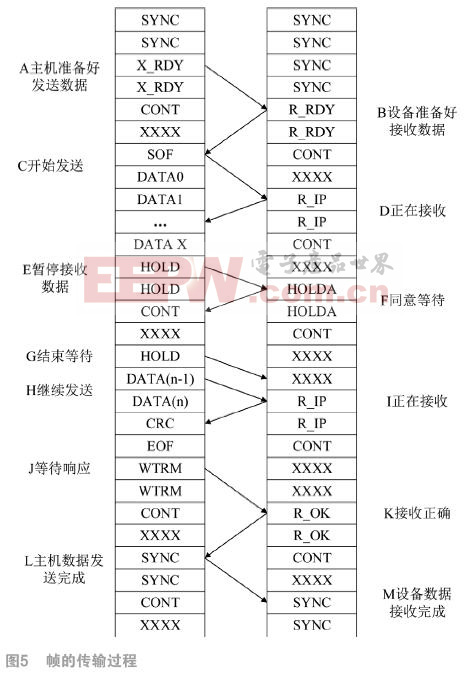

现以一个数据帧的传输过程为例来说明原语在传输过程中的作用以及其间应答关系,传输过程如图5所示。

A.若发送端有数据要发送,发送X_RDY,通知接收端准备接收;

B.若接收端可以接收数据,发送R_RDY;

C.发送端开始发送数据;

D.接收端在接收到数据时,发送R_IP;

E.发送端数据未准备好,发送HOLD原语告诉接收端等待;

F.接收端接收到HOLD原语后,发送HOLDA原语应答;

G.发送端可以继续发送数据,发送HOLD原语结束等待;

H.继续发送数据;

I.接收端接收到数据时,发送R_IP原语;

J.发送端发送完数据以后,发送WTRM原语给接收端,发送端等待接收结果;

K.接收端接收完成并校验正确后,发送R_OK原语给发送端,数据接收正确;

L.发送端发送SYNC原语进入空闲状态;

M.接收端发送SYNC原语进入空闲状态。

4 数据的测试与验证

数据测试是整个系统开发期间最为耗时的部分,为方便测试而选用Xilinx公司提供的一款在线逻辑分析软件Chipscope Pro。在ISE中直接调用数据采集的核(包括ICON、ILA和VIO)就能使用Chipscope来观测FPGA芯片内部的信号。模拟产生一串从0开始递增的数据发送给GTX,然后通过Chipscope检测接收到的数据值,其采样图如图6所示。

从图7可看出数据呈现非常规律的分布,从数据放大后的图中可看出是非常规律的递增码。本系统自设计完成以来已经做过多次测试,为配合数据测试的需要还为本系统开发一套上位机数据误码检测软件。由于每次测试使用的数据格式都不同,每次存储的数据量不少于2TB,数据存入固态硬盘后用数据误码检测软件对数据进行检测,经反复测试后的结果证明,所设计的高速存储系统存储速度不低于800MB/S并且性能稳定、数据准确率高。

5 结束语

本文给出了一个基于SATA协议的高速存储系统的设计,由于SATA协议传输速率较高、通信过程较为复杂,以往只能在专用芯片上实现。随着越来越多高端FPGA集成了串行通信模块,在FPGA内部可以实现整个SATA协议,系统设计完成后,测试结果显示其体积小、抗干扰能力强、传输速度快且稳定性好,因而有很广阔的应用前景。

参考文献:

[1]Serial ATA International Organization.Serial ATA Revision2.0[S].USA,2005.08.

[2]张天文.基于SATA2.0接口的固态硬盘控制器的设计与实现[D]. 中北大学, 2015.

[3]寇科男. SATA接口技术研究及设计[D]. 哈尔滨工业大学, 2010.

[4]Xilinx.Process Local Bus(PLB)v4.6(v1.03a)[S].USA:Xilinx,2008.

[5]赵峰. FPGA上的嵌入式系统设计实例[M].西安:西安电子科技大学出版社, 2008.

[6]赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,1999.

[7]Xilinx.FIFO Generator v4.4 User Guide[S].USA:Xilinx,2008.

本文来源于中国科技期刊《电子产品世界》2016年第6期第39页,欢迎您写论文时引用,并注明出处。

评论