基于FPGA的VGA显示系统的设计与实现

摘要:针对VGA(视频图形阵列)接口显示器的检测需求,设计了一种基于Altera FPGA的VGA显示系统。详细介绍了VGA显示的原理,采用硬件描述语言Verilog完成了VGA显示所需的驱动时序和图像存储相关模块的设计,并对整个系统进行了综合仿真,验证了设计的正确性。仿真与测试结果表明,该设计可以在简单的情况下实现图像或字符显示,节约了硬件成本,还可以满足不同显示标准的需要。

本文引用地址:https://www.eepw.com.cn/article/201603/287500.htm引言

VGA (Video Graphics Array)是IBM公司在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在显示器领域得到了广泛的应用。随着电子设计自动化(EDA)技术的发展,近年来FPGA(现场可编程逻辑门阵列)在大规模嵌入式系统设计中得到了广泛应用。本文对基于FPGA的VGA显示系统进行了研究,利用了Altera Cyclone IV系列的FPGA高达上百兆的工作频率特性为数字图像处理提供了良好的实时性,其内部集成的数字锁相环为系统的工作时钟提供的良好的稳定性,其内部嵌入的存储器可以存储一定容量的图像信息,其丰富的I/O口资源可以扩展外接大容量的显示接口。此外,FPGA电路的可重构性,为系统功能的优化和升级以及功能拓展提供了很大的设计空间。因此,由FPGA完成VGA图像的显示和控制,较好的实现了图像数据处理的实时性和可靠性,具有成本低、结构简单、应用灵活的优点,可以广泛应用于视频和计算机的显示技术领域。

1 VGA显示原理

计算机显示器的显示有许多标准,如VGA、SVGA等。VGA 作为一种标准的显示接口得到广泛的应用。常见的彩色显示器,一般由CRT(阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成。显示器中的阴极射线枪通过发出电子束打在涂有荧光粉的荧光屏上,产生RGB三基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,进行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

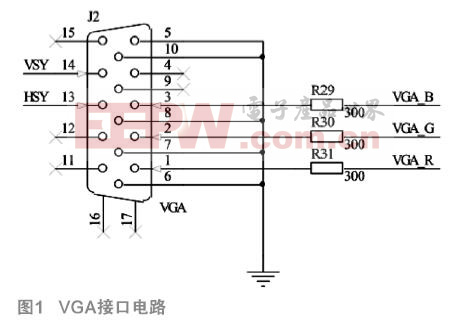

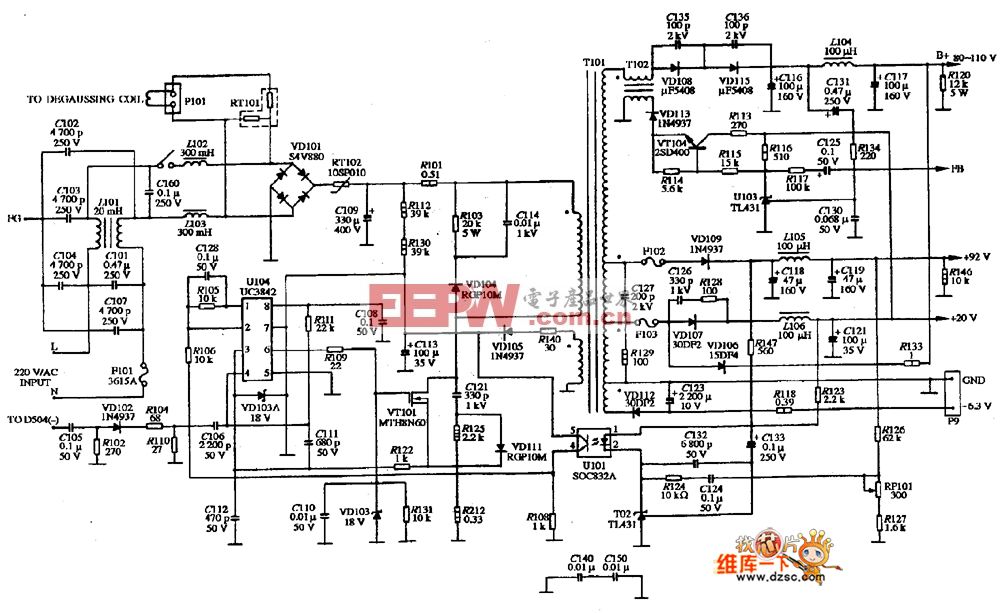

VGA接口电路如图1所示,VGA采用15 pin的接口,用于显示的接口信号主要有5个:1个行同步信号(HSY);1个场同步信号(VSY)、以及3个颜色信号(VGA_G、VGA_R、VGA_B)。

VGA 的接口时序如图2所示,场同步信号VSYNC在每帧开始的时候产生一个固定宽度的低脉冲,行同步信号HSYNC在每行开始的时候产生一个固定宽度的低脉冲,数据DATA在某些固定的行和列的交汇处有效。

对于VGA接口信号的时序驱动,要严格遵循VGA显示工业标准。在不同分辨率下,VGA驱动时序中的行、列同步信号的格式是完全一致的,都由同步段、后廊段、激活段和前廊段组成,只是对应每段的高低电平的保持时间不同。本文采用刷新频率为60Hz,分辨率为800x600的VGA显示标准,其驱动时序表如表1所示。按照800x600x60Hz 的显示标准时序,一个列像素扫描需要25ns,要完成一行的扫描,需要1056个列像素,也就是说需要1056x25ns 的时间。如果要完成所有行的扫描的话,需要628x1056x25ns的时间。但不是所有时间都用来VGA图像显示,有一部分的时间用来时序同步操作。

2 FPGA的设计与实现

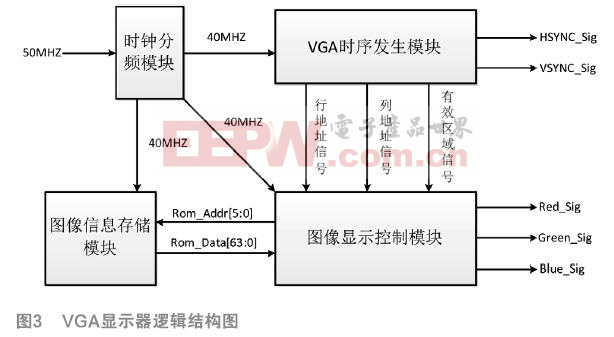

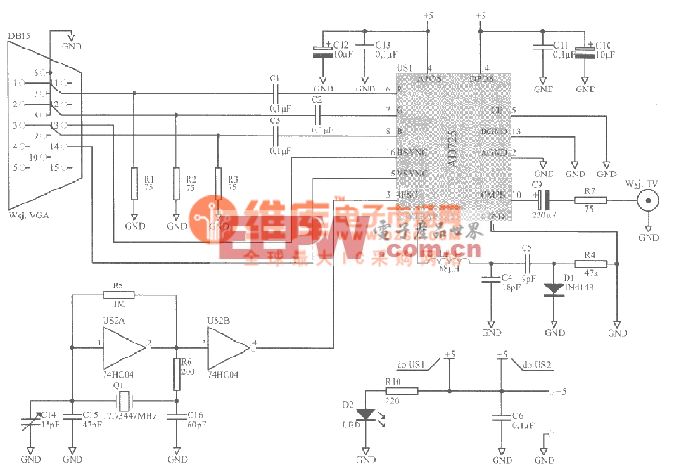

设计采用Altera公司的Cyclone IV系列FPGA(EP4CE6F17C8)作为主控制器,该芯片具有多达16272个LE、179个用户I/O口。器件中M9K存储块提供240 KB存储容量,能够被配置来支持多种操作模式,包括ROM、RAM、FIFO以及单口和双口模式。器件具有3个可编程锁相环(PLL) 和9 个全局时钟线,能提供时钟管理和频率合成,实现最大的系统功能。VGA图像显示器是一个较大的数字系统。本设计采用模块化的设计方法,遵循自顶向下的程序设计思想,进行功能划分并按层次设计。采用硬件描述语言Verilog设计了各个功能模块并进行仿真,使顶层VGA显示模块实体仿真综合得以顺利通过。VGA图像显示器的逻辑结构框图如图3所示。根据VGA显示的原理,VGA图像显示器的工作原理是:时钟分频模块负责为系统提供驱动的基准时钟,VGA时序发生模块负责产生时序驱动信号、行列地址信号和有效区域信号,同时在正确的时序控制下,由图像显示控制模块读取图像信息存储模块中的像素数据并产生R、G、B三基色信号至显示器的VGA接口,进行图像显示。

2.1 时钟分频模块设计

设计驱动VGA采用800x600x60Hz显示标准,该显示标准需要的最小单位也就是列像素所占用的时间周期为25ns。也就是说,至少需要频率为 40MHz 的时钟为VGA驱动提供基准时钟,利用FPGA器件的嵌人式锁相环(PLL)对FPGA源时钟(频率为50MHz)进行倍频(四倍频后五分频得到 40MHz)。PLL是FPGA的重要硬件资源,其主要的功能是对源时钟编程、倍频、分频等。

2.2 VGA时序发生模块设计

VGA时序发生模块接口信号包括:行同步信号HSYNC Signal、场同步信号VSYNC Signal、有效区域信号Ready_Sig、行地址信号Column_Addr_Sig、列地址信号Row_Addr_Sig。行同步信号是根据行像素计数寄存器Count_H的计数值来产生,场同步信号产生是根据列像素计数寄存器Count_V的计数值来产生,而有效区域信号Ready_Sig用来确定串行输出的显示器的红、绿、蓝信号线上电平的高低。

经过PLL分频后的时钟每过25ns,Count_H就会累加计数,当其计到1056个列像素时,Count_V加1,Count_V最大计到628。VSYNC Signal 在同步段保持低电平,之后就会拉高输出,同步段保持低电平的时间是扫描4个列像素的时间。而HSYNC Signal在同步段即刚开始的128个行像素保持低电平,之后输出高电平。有效区域信号Ready_Sig发生在HSYNC Signal和VSYNC Signal的激活段交集处,输出为高电平有效。为了精确地控制图像显示在屏幕的位置,VGA时序发生模块有义务输出当前的行地址信号(Column_Addr_Sig)和列地址信号(Row_Addr_Sig)。行地址的计数是发生在128个Count_H之后,而列地址计数是27个Count_V之后开始计数。

VGA时序发生模块sync_module.v的部分代码如下:

module sync_module

(

input CLK, RSTn;

output VSYNC_Sig, HSYNC_Sig, Ready_Sig;

output [10:0] Column_Addr_Sig, Row_Addr_Sig;

);

………………………

…………

assign VSYNC_Sig = ( Count_V <= 11'd4 ) ? 1'b0 : 1'b1;

assign HSYNC_Sig = ( Count_H <= 11'd128 ) ? 1'b0 : 1'b1;

assign Ready_Sig = isReady;

assign Column_Addr_Sig = isReady ? Count_H - 11'd216 : 11'd0;

assign Row_Addr_Sig = isReady ? Count_V - 11'd27 : 11'd0;

endmodule

本文来源于中国科技期刊《电子产品世界》2016年第2期第48页,欢迎您写论文时引用,并注明出处。

评论