基于单片机的低频数字相位测量仪的设计

关键词:单片机;低频;集成电路;可编程逻辑器件;绝对误差

频率是信号的重要参数之一,如何获得这一准确数据已经在信息领域显得越来越重要了[1,2]。相位测量在信号提取、检测、处理等方面有着重要的应用[3]。本设计采用89C52单片机和可编程逻辑器件(CPLD)为核心,利用单片机进行数据处理并显示结果,软件采用汇编语言实现,构成低频信号频率相位测量仪。?

1系统工作原理

本设计以89C52单片机和可编程逻辑器件(CPLD)为核心,构成低频信号频率相位测量仪。该仪器具有移相、频率和相位测量2大功能。移相电路由移相网络和信号放大电路组成,对固定频率信号(100 Hz,1 kHz,10 kHz)可满足-45~+45的相移要求;频率、相位测量电路由阻抗变换电路、整形电路、分频电路、计数器电路、锁存器、数据处理和显示电路等组成,可对10 Hz~20 kHz信号进行频率和相位测量。单片机系统是整个硬件系统的核心,他既是协调整机工作的控制器,又是数据处理器,并完成对最终显示的控制。

(1) 单片机89C52(内部带8 kB FLASH ROM)、地址锁存器74LS573和数据存储器6264(内部 RAM为8 kB)构成的[4]。

(2) 数据处理主要是正确判断对所输入的信号是测频还是测相,并完成测频、测相的功能。

(3) 由控制面板、显示接口芯片8279构成显示电路。?

2精度分析

本设计要求相位测量精度绝对误差≤1,因此,在所测信号一个周期中,只有计数数值超过360次时才能达到要求。对于被测信号频率为20 kHz时,其周期为50 μs,在50 μs内计数值为360次,由此可计算出时间基准信号的频率为20 kHz360=7.2 MHz,所以采用8 MH z晶振作为时基信号源,完全可以满足精度要求[5]。?

3系统设计总框图

系统设计总框图如图1所示。

?

?

4测频、测相的实现

测频、测相电路是本次设计的主要内容,此部分采用可编程逻辑器件(CPLD)完成,由单片 机控制。单片机的汇编程序就是按照CPLD的设计原理而编写的[6,7]。

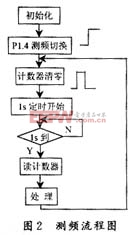

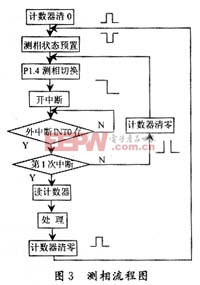

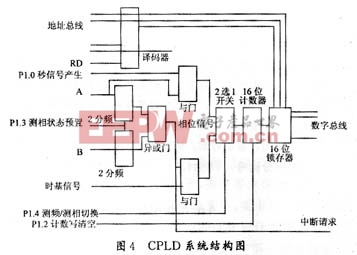

图2,图3分别为测频、测相的流程图。为了便于说明,画出此系统结构图,如图4所示。

CPLD电路描述:首先经过扫描P1?1控制74257(2选1)电路,选择测频还是测相,如果为高 电平则测频,利用单片机产生10次中断产生的秒信号,即在1 s中信号的脉冲数,其中计数器是由6个74193搭成的24位计数器,经锁存器锁存,等待单片机读出;如果为低电平则测相。测相时先调用了测频的程序但并不显示,而是存起来待用,然后给D触发器清零,否则得到的异或值不同,如图3所示。a′,b′经过异或生成相位信号并发出中断请求,与8 MHz的时基信号相与所产生的脉冲由计数器计数,然后把所计的数送入锁存器锁存,等待单片机读数。?

5结语

本文采用单片机和可编程逻辑器件(CPLD)作为低频数字相位测量仪的核心部分。用89C52进行数据控制、处理,送到显示器显示,硬件结构简单,软件采用汇编语言实现,程序简单可读写性强,效率高。与传统的电路相比,具有处理速度快、稳定性高、性价比高的优点。

参考文献

[1]Joseph J CARR.射频电路设计理论与应用[M].北京:电子工业出版社,2002.

[2]Ken C Phkmann.数字音频原理与应用[M]. 北京:电子工业出版社,20 02.

[3]张厥胜,张会宁,邢静.锁相环频率和成器[M].北京:电子工业出版社,1997.

[4]余永权.ATMLE89系列单片机应用技术[M]. 北京:北京航空航天大学出版社,2002.

[5]周明德.微型计算机原理及应用[M].北京:清华大学出版社,1998.

[6]张迎新.单片微型计算机原理、应用及接口技术[M].北京:国防工业出版社,2003.

[7]冯涛,王程.可编程逻辑器件开发技术[M].北京:电子工业出版社,2002.

评论