存储器接口设计-认识信号完整性的价值

存储器和其它组件之间的问题通常存在于这些器件之间的接口上,这些系统级的问题有时候是难以觉察的。本文详述了一种能够很容易地识别和解决这些出现在存储器接口上问题的测试工具,从而使你的设计更为鲁棒。

本文引用地址:https://www.eepw.com.cn/article/193860.htm过去,设计工程师已在新系统的设计中采用信号完整性(SI)测试并用于稳定产品质量。尽管SI在工程阶段非常有价值,但它并非万能药,随着产品设计不断深化,其价值实际上会变得越来越小,并且要用温度及电压边际测试(margin testing)来补充或替代SI测试以稳定产品质量。

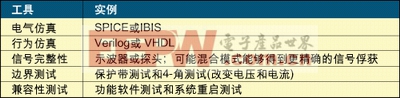

表1: 存储器设计、测试及验证工具。

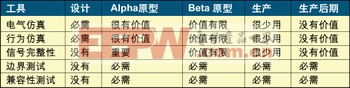

正确选择存储器设计、测量和验证的工具将减少工程时间并增加检测潜在问题的可能性。表1是5个用于存储器设计的重要工具的简 短描述,由于本文将重点放在用于确认设计的功能性及鲁棒性的工具上,这一列表并未完全列出所有的存储器设计工具,表2说明了在什么时候采用这些工具最为有 效。

产品开发的5个阶段

调试实验室没有逻辑分析仪对设计和调试是不可思议的,然而,鉴于对成本和时间的考虑,逻辑分析仪很少成为检测系统内故障或问题的首选工具,它们却常用来调试由兼容性或4-角测试(4-corner)所检测到的问题。产品开发包括5个阶段:

阶段1-设计

要在硬件设计中实现一个概念或思想,由于没有现成的原型,只可采用仿真工具,因此,设计工程师只能依靠电及行为仿真工具来进行设计。

阶段2-阿尔法原型

阿尔法原型是最初或较早的原型,它可能会在生产(BIOS、功能性等)前就经过多次改变。

设计工程师必须在阿尔法原型上进行足够的测试以确保下一个原型,至少从硬件角度讲,将接近生产就绪状态。就这一点而言,可靠的工具将至关重要。

首先要采用的工具是启动和软件检验,由此可得出有价值的信息,这些信息与基本软件检验相结合,从而指出需要加以改变的数据,由于基本硬件改变尚有可能,彻底的软件检验或许尚不可行。

表2:验证与设计阶段相对的存储器功能性的工具。

在这个阶段SI测试起着重要作用,它捕获线路板上线迹的模拟信号,这些捕获可与仿真或器件规格进行比较来确定这一器件是否符合规格及有充足的时序裕量,否则,就必须对器件加以改进。

然而,有一种在这个阶段不应使用的工具是边际测试,该测试只能在硬件完成后采用。在运行相应的测试后,设计工程师要进行一系列设计变更,包括可能要通过电或行为的仿真来确保设计达到所需的效果。

阶段3-贝塔原型

在最后阶段(贝塔原型),硬件接近成品状态, 仅有一些很小的问题出现,组合测试可以确保系统处于生产就绪状态,软件或兼容性的测试必须彻底,这一测试可单独执行或与边际测试结合在一起执行,边际测试 的涵盖范围应当是广泛的。不同的温度与其极限电压电平对识别这些问题及边际时有价值,这一组合应捕获可能出现的存储器故障。

在这一阶段SI测试的作用有限,但它可用于调试功能性的故障或确认在阿尔法原型阶段所进行的改变。SI测试不应用于验证来自未被改变的阿尔法原型的信号或网络。假如在贝塔原型阶段有任何补充性的修改,则有必要通过电和/或行为仿真或SI对这些修改进行确认。

阶段4-生产

在生产阶段很少对系统进行改变,这一阶段的重点在于稳定产品质量,系统的生产或许需要几个月甚至几年,这一生产或许要用到数百或数千个元件,公司有一套稳定产品质量的程序显得尤为重要。

在系统进入生产阶段后对元件上进行一系列的质量测试,可以确保足够的元件供应以使生产不致中断。在生产阶段,极少对母板的线 迹和布局加以改变,由于SI测试已用于确认那些改变,在这一阶段,SI测试不再必要。此外,SI测试不能捕获以往由系统/存储器相关的问题所造成的故障, 首选的工具及稳定产品质量的关键是兼容性及边际测试。

阶段5-后期制作

像MP3播放器或DVD录音机这样的系统在生产后段没有稳定产品质量的要求,然而,其它的系统可能有存储器升级或支持的要求,这一点在笔记本电脑、移动PC及其它器件中尤为常见,而且在生产后段的数年都很重要,边际测试及兼容性测试成为稳定产品质量的关键。

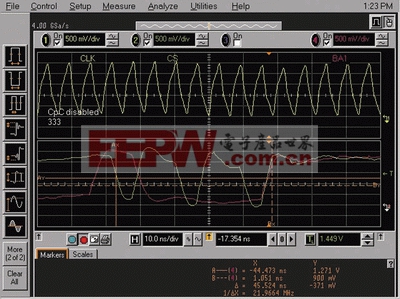

图1:从示波器所获得的典型的信号完整性问题。

信号完整性测试

电子设计工程师喜欢使用示波器观察电路设计并评估信号。图1显示了一个典型的SI捕获,在这一实例中,目标照片表明信号来自单个DDR同步动态随机存取存储器(SDRAM)组件:地址组1、片选择信号及不同的系统时钟。

SI测试过程用系统信号的示波器光图来评估电压随时间的变化,这些光图或“捕获”通过视觉来评价违规状态,这种方法因对工程专家的水平提出高的要求,因而是一个耗时的过程。

如图1所示的SI测试图能够反映出振铃、上冲/下冲和时钟冲突(斜率、建立/保持时间、总线争用等),假如上述状况中有任何一种出现,通过兼容性及边际测试都能轻易发现系统故障,在这些问题被发现后,其它的工具(逻辑分析仪、SI测试等)能够确定故障的原因。

SI分析的局限性

SI分析正变得越来越困难并且消耗时间,在像FBGA封装这样的情况下,几乎不可能进行SI分析,原因何在?除非探测点被增加到设计当中,在FBGA封装中是不可能探测到信号的。

在多芯片模组(MCM)封装中,将各种不同的芯片组合在一个封装内,这些封装既可用铸模化合物也可用密闭的方法加以保护,并且封装内的信号无法被探测到。

评论