FPGA+POWER PC架构的实时飞行试验振动数据分析系统

引言

本文引用地址:https://www.eepw.com.cn/article/193107.htm在飞行试验过程中,飞行试验安全监控对飞行试验的安全起着至关重要的作用。飞行试验本身具有相当的风险性,危及飞机和试飞员安全的因素错综复杂、涉及面广,不但包含飞机本身的因素,还包括许多外界条件。由于不安全事件的突发性,往往使得试飞员、地面指挥员、机务人员、安全救护员等不能做出及时响应。

特别是近几年随着航空技术的飞速发展,飞机的结构日趋复杂,其结构强度、可靠性问题也日益突出,带来的问题是飞机故障率增高、维护难度加大。而结构强度问题90%是由振动导致或与振动有关。振动出现异常,其结果轻则引起飞行员情绪紧张影响操作;重则损伤机器部件,减少使用寿命,甚至危及飞行安全。

由于振动信号具有采样率高、数据量大、处理复杂的特点,通过遥测数据处理系统很难传输大量的振动参数。近几年对振动信号实时监控技术进行了一定的探索和研究,通过遥测链路将机载振动数据传到地面,在地面遥测数据处理站对数据进行分析和实时监控。由于前期所作的研究受到各种条件的限制,效果不太理想,因此结合某型号试飞测试的需要,在关键技术攻关项目中通过对振动信号进行机上的实时数据分析,将分析结果实时发送至地面监控系统,以减小遥测传输带宽,真正实现振动信号的遥测实时监控。

1 国内外所采用的方法分析

纵观国外飞机试飞情况,无论是空客的A380,A330,A400M还是波音787,在试飞过程中都非常重视振动参数的测量,为了使得飞机的各部位振动指标满足设计要求,在飞机设计的时候就已经在地面建设了“地面振动测试系统”。而对于试飞验证阶段的振动监控更加重视,通过专用的振动、应变实时处理系统对所关心的振动点进行实时监测。我院在研制某型直升机传动系统振动试飞实时数据处理系统时,采用软件技术对振动信号进行了分析处理,可以实时处理2路振动参数,基本解决了该飞机试飞振动数据实时处理需求,但是由于遥测带宽的限制,导致还有一部分振动参数被取消或降低需求,另外通过遥测传输和软件处理也存在跳点多、时间延迟大的问题。

据估计,在某型运输机试飞中,振动、应变参数将多达数百个,需要实时监控的参数有数十路。按照传统的技术和方法,无法满足该型号飞机试飞对振动信号实时处理的要求。针对该型号的试飞需求,在该型号关键技术攻关项目中提出了采用嵌入式处理器+FPGA架构来设计振动信号机载实时处理单元,在机上实现实时数据的工程量转换、信号实时分析处理及高速存储,将处理结果重新编码后送机载测试系统遥测发送,最终实现振动信号的地面遥测实时监控。

2.1 硬件系统设计

2.1.1 硬件工作原理

硬件部分包括机载高采样实时处理单元硬件和地面遥测分析单元硬件,前者主要由嵌入式计算机、FPGA分析单元和系统配置装置构成,后者是一台数据分析工作站。嵌入式计算机选用400 MHz处理器芯片,10/100 MBase-T以太网口,配以200万FPGA逻辑门阵列用于实现对振动信号采集、处理、分析等工作,系统配置装置采用笔记本电脑通过网络接口完成对机载高采样实时处理单元的系统配置。

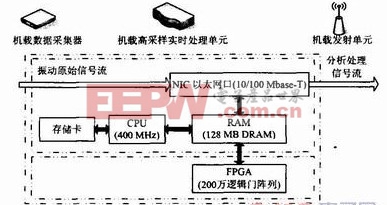

振动原始信号流由以太网口输入,嵌入式系统完成振动数据流的解包后将数据通过DMA方式直接传输至FPGA实时处理芯片,由FPGA模块完成实时在线的振动数据分析处理工作:工程量转换、频谱分析、时域统计量计算等,分析处理完后通过DMA方式传送至嵌入式计算机的DRAM中,嵌入式计算机完成数据存储和数据发送工作。硬件原理示意图如图1所示。

图1 机载高采样实时处理单元硬件原理

2.1.2 接口设计

振动信号的信号电缆、供电电源电缆接口设计按符合MIL-C-38999 I系列航空电连接器设计。提供信号电缆的接口、电源接口以及网络接口。所有接口以航空电连接器的形式提供。

2.1.3 核心硬件设计

(1)硬件核心逻辑原理结构

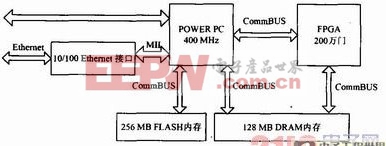

系统硬件核心部分由400 MHz处理器芯片,200万门FPGA芯片及以太网接口芯片及串行通信芯片组成。系统硬件逻辑结构、输出硬件数据流逻辑原理设计及元件组成如图2所示。

图2 系统硬件逻辑原理设计及元件组成示意图

(2)功能

POWER PC核心CPU,内置VxWorks实时操作系统,负责系统网络接口、串行通信接口。Xilinx FPGA芯片,完成自定义FFT频谱分析及实时信号分析算法。

2.2 实时处理系统软件设计

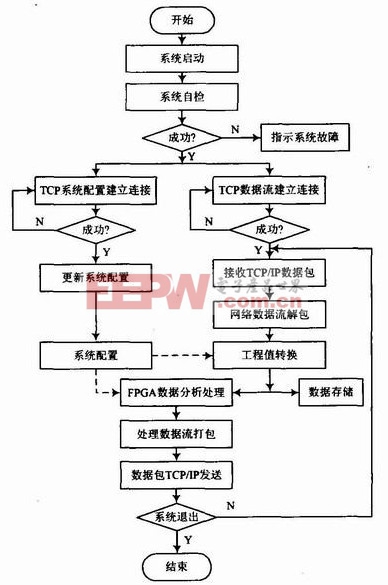

机载振动数据实时处理单元开机后,软件自动运行,首先完成系统的自检,判断系统的工作状态,如果正常则进行下一步工作,同时将设备面板的“工作正常”指示灯闪烁,反之不闪烁。系统正常后,软件进入循环连续的数据接收、分析处理与存储程序,同时处理后的信号发送至机载数据网络。

高采样实时处理单元软件在实时操作系统下运行,使用NI公司的图形化编程语言LabVIEW RT、高级信号处理包、噪声振动信号处理包和基于赛灵思公司Xilinx ISE FPGA开发模块编制完成。机载高采样实时处理单元配置软件全部操作采用图形化的人机界面,能方便、直接、快速完成机载系统的配置。

机载高采样实时处理单元软件流程如图3所示。

图3机载高采样实时处理单元软件流程图

软件采用模块化设计的思想,以功能来划分各个不同的子模块。

2.2.1 实时网络数据传输模块设计

评论