容性设备绝缘监测数据采集系统硬件电路设计

摘要:介绍了容性设备在线绝缘性能检测系统中,数据采集硬件电路的设计思路。采用DSP技术实现数字滤波和相位换算。提高了系统的抗干扰能力。16位双极性A/D转换器,大大提高了信号的精度。采用程控增益的办法,提高了系统增益的稳定性。现场采集的实时数据来看,交流信号电流幅值偏差在±5%之内,相位的误差为0~3%,并且硬件系统稳定可靠。

关键词:DSP2812容性设备;介质损耗;数据采集;ADS8365

0 引言

容性设备是指绝缘结构采用电容屏的电气设备,主要包括耦合电容器(OY)、套管、电流互感器(CT)以及电容式电压互感器(CVT)等。在变电站中,高压容性设备是其重要的组成部分。这些高压容性设备绝缘性能的好坏,对于整个变电站的运行安全至关重要。现有的技术手段是通过测量介质损耗tan δ及电容量Cx,可较为灵敏地发现电容型设备的绝缘缺陷。目前所有的在线监测系统均把介损作为重点测量的对象。

为了提高系统监测的精度,本系统采用基于相对本地测量单元的数字介损测量技术。放弃传统的过零比较技术,利用TMS320F2812具有较强的数字运算能力,通过DFT算法,精确的提高系统介损测量的准确度。

1 数据采集系统设计方案

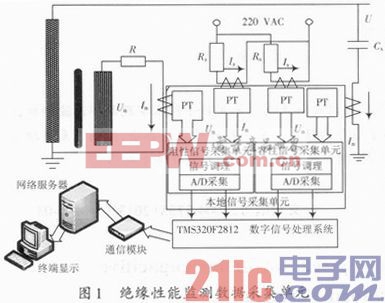

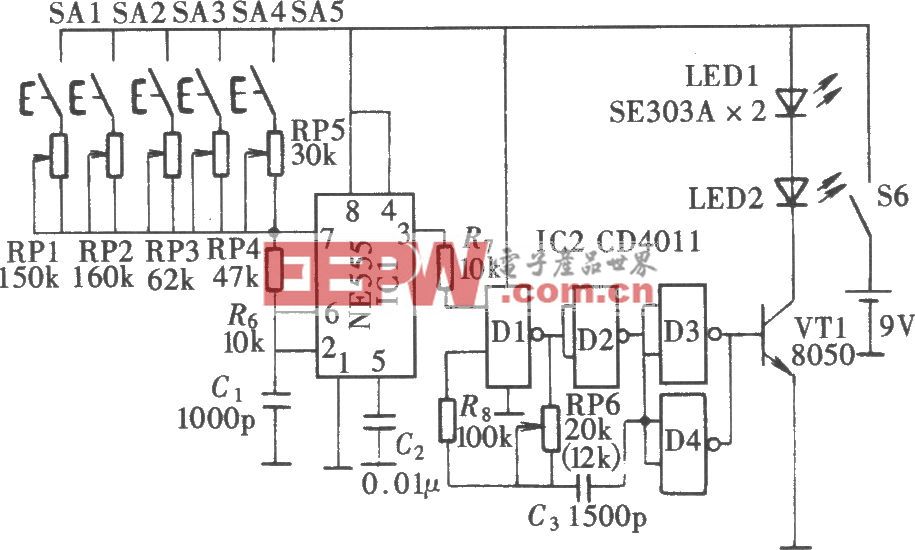

在以往的系统设计中,通常采用母线的电压作为基准进行测试,但是这种测试方式经常会受到现场环境和传输过程的干扰影响。为了减小干扰,可以采用系统的供电电源为基准源。这样不但可以减小干扰提高精度,操作起来也十分的方便。系统测量的方案如图1所示,在该系统中,假设流过系统的阻性电流为Ix,而系统的容性电流为In。同时,设基准源流过参考电阻Rs的电流为Is。利用高精度电流传感器把被测电流信号Ix,In变换为电压信号Ux,Un。电流传感器在±12 V直流电源的供电下可以将100μA~700 mA的电流信号转换成电信号输出。电压信号的峰值为0~10 V。然后由数字化测量系统对信号进行同步采样及傅里叶变换处理,获得这两个信号的基波向量及其相位夹角phUx-phUn。如果不考虑电压互感器(PT)的相位失真问题,则可方便地计算出电容型设备Cx的介质损耗tan δ值。

电容型设备的介损测量通常需要选用母线电压作为相位测量的基准。传统的处理方式是把母线PT的二次侧电压信号直接提供给检测系统,其主要缺点是现场布线复杂,模拟信号在长距离的传送过程中易受电磁场干扰的影响,有可能导致介损测量结果失真。本方案所设计的绝缘监测系统采用信号处理单元的220 VAC电源作为参考基准,不用将PT二次信号进行远距离传输。该方法较好地解决了基准电压信号的取样问题,也是目前比较通用的解决方式。

由图1可知,该系统主要由两个数据采集单元组成。每个采集单元都包含了信号调理和A/D采样两个部分。

2 硬件电路设计

对于设备阻性电流和容性电流的获得是通过有源零磁通传感器来实现的。该电流传感器相对于传统的无源电流传感器来讲能够大大提高对微电流信号测量的准确度。其电流精度可以达到微安数量级。如此高的精度对于复杂环境中的容性设备来讲,信号调理电路的设计和软件滤波器的设计尤为重要。

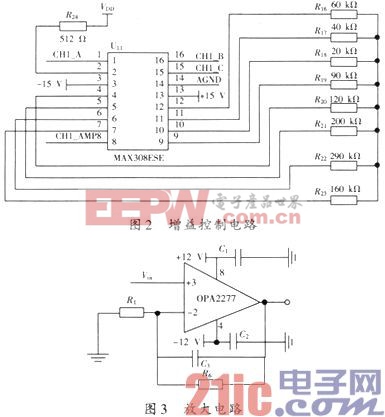

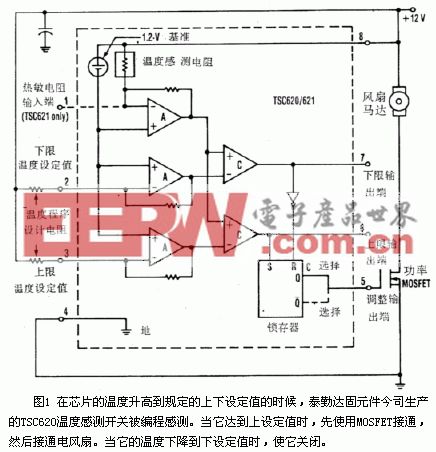

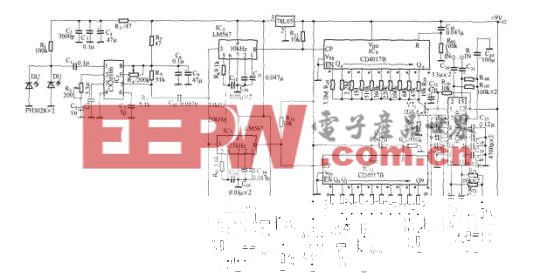

2.1 放大电路

本系统放大电路采用动态增益的办法实现。其具体电路如图2所示,CH1 A,CH1 B,CH1 C接CPLD,由CPLD进行控制。即如图3中的风通过数字控制的方式来实现。主控芯片CPLD选用EPM3128ATC100-10,该芯片是一款高性能、低功耗、基于E2PROM的可编程逻辑器件,片内集成了2 500个可用门,8个逻辑阵列模块(LAB),每个LAB由16个宏单元组成,最多为用户提供80个I/O口,通过JTAG接口进行在线编程,可以进行100次的程序烧写。选用该芯片主要基于以下几点考虑:Altera器件采用铜铝布线的先进CMOS技术,功耗低、速度快,采用互连结构,提供快速、连续的信号延时和具有相同延时的时钟总线结构。逻辑集成度高,开发周期短,使用专用软件设计输入、处理、校验及器件编程一共仅需几个小时。FPGA/CPLD中寄存器资源或组合逻辑资源比较丰富,更适合于时序电路和组合逻辑电路的设计。

为了防止信号的振荡,电路中增加电容C3,对其进行消除振荡影响。

cvt相关文章:cvt原理

评论