基于EDA技术的单片机IP核设计

摘 要:本文介绍了利用EDA技术设计出与MCS-51系列微处理器指令集完全兼容的8位嵌入式微处理器芯片的IP核,并经过验证获得了满意的效果。

关键词: 电子设计自动化;知识产权核;设计

1. 引言

EDA(Electronic Design Automatic),简单的说就是通过有关的开发软件,自动完成用软件的方式设计的电子系统到最终形成集成电子系统或专用集成芯片的一门新技术。其中, EDA关键技术之一就是可以用硬件描述语言(HDL)来描述具有广泛应用前景、且具备自主知识产权的IP核(Intellectual Property)。这种IP核具有很高的通用性和灵活性,可以通过软件编程完成不同特定的功能,可以任意使用在各种嵌入式微控制系统中。嵌入式IP核的应用,由于重用设计思想、设计知识,极大地降低了设计成本,缩短了设计周期,成为当今片上系统(SoC)的重要设计手段。【1】

MCS-51系列单片机是目前国内应用时间最长、最普及、可获得应用资料最多的功能强大的8位MCU,建立兼容MCS-51单片机IP核对于各种嵌入式系统和SoC的应用具有重要意义。针对MCS-51单片机的应用前景,笔者成功设计了与MCS-51系列微处理器指令集完全兼容且功能更强的8位嵌入式微处理器芯片,通过IP核重用技术,可广泛应用在各种SoC中。

2.系统简介

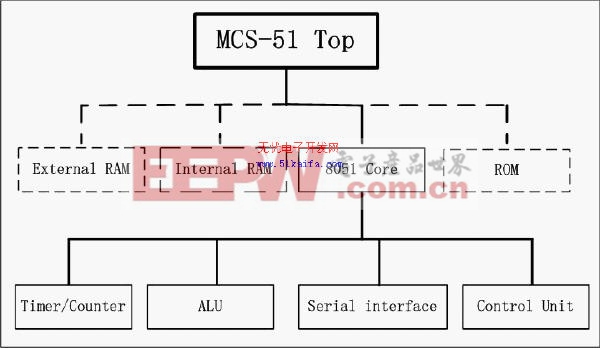

本课题采用Altera公司的MAX+plusⅡ10.0设计平台,以超高速集成电路硬件描述语言VHDL为系统逻辑描述的唯一表达方式,采用自顶向下的设计原则,对MCS-51单片机进行反相设计。同时选用 Altera 公司的 ACEX系列器件来实现最终的IP核。由于篇幅的关系,笔者不打算对开发平台、开发工具以及最终实现硬件电路的FPGA芯片进行介绍,而是着重介绍整体的设计思想。图1是本课题进行设计的顶层设计层次图。实线部分是MCS-51单片机的内核部分,虚线部分是外围存储电路部分。下面介绍各部分的实现方法。

图1 MCS-51单片机顶层设计层次图

3.系统现实

3.1 算术逻辑单元(ALU)的实现

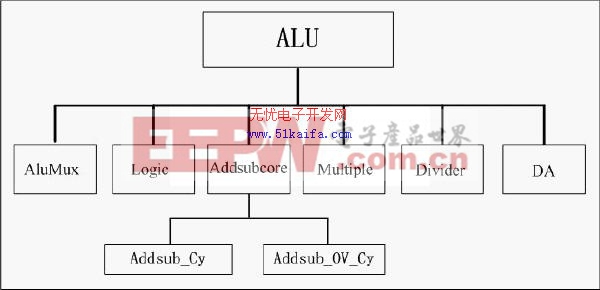

算术、逻辑运算模块的功能是按照控制单元给出的指令,对来自数据存储器、程序存储器、累加器A以及程序状态字的相关位的数据,进行相关的算术和逻辑运算。图2是用VHDL语言对ALU模块进行描述的设计层次图。由图中可以看出整个ALU由6个模块组成:加/减法器,乘法器、除法器、十进制调整器、逻辑运算器以及一个多路选择器。其中加/减法器又可以分成两个子模块。本模块将用较为简单的纯组合逻辑电路来实现。限于篇幅,具体的实现不再赘述,请读者参阅参考文献【2】。

图 2 ALU设计层次图

3.2定时器/计数器(Timer/Counter)模块的实现

分析MCS-51单片机的定时器/计数器的功能和原理可知,本单元将必须以时序逻辑电路的方式来实现。图3中的左图就是本模块设计完成后形成的符号文件。图中的输入除时钟CLK、复位RESET、外部中断0 INT0_I和外部中断1 INT1_I直接来自芯片的外部输入之外,其余的输入信号全部来自控制器。其中的RELOAD_I[7 to 0]、WT_EN以及WT_I[7 to 0]用于重写定时器/计数器内部寄存器。所有的输出信号全部送往控制器,用于及时更新特殊功能寄存器的内容。

定时器/计数器的两种工作方式决定了要设计好定时器/计数器首先必须设计一个分频器和两个(因为有两个定时器/计数器)负跳变的检测器。负跳变的检测器,可以用一个双稳态的触发器来实现;分频器的实质是计数器。触发器和计数器都是时序逻辑电路中的基本单元,VHDL语言的实现方法请读者参考相关书籍【1】。因此本设计实体的结构体将由3个进程来实现。除了分频器和两个负跳变的检测器各占用一个进程外,第三个进程用于实现时器/计数器的四种工作模式。对定时器/计数器的各种工作于模式的原理分析可知,要实现这样一个电路,其VHDL语言的结构体应该包括两个大的部分:一是置中断标志位,二是改变计数寄存器的值。同时,改变计数寄存器的值又可以细分为两块――写高8位寄存器和写低8位寄存器。各个进程之间相互关联,内部信号将作为进程之间传输信息的纽带。

评论