基于EDA技术的单片机IP核设计

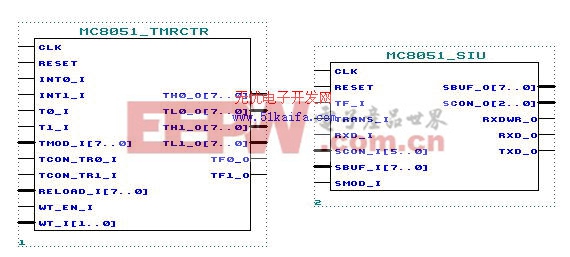

图 3 8051_tmrctr和8051_siu的符号文件图

3.3串行接口模块

MC5―51单片机的串行接口既可以作通用异步接收和发送器(UART)用,又可以作同步移位寄存器用。图3中的右图就是本模块设计完成后形成的符号文件。由于本设计不支持I/O口的复用,所以为串行口工作于模式0下增加了RXD_O和RXDWR两个输出引脚,前者用于输出,后者为输出有效控制位。串行口控制寄存器SCON在设计中也被分成两部分,一部分接收来自控制器的输入(一共6位,SM0、SM1、SM2、REN、TB8和RI),一部分作为输出送往控制器(一共3位,RB8以及分别指示发送和接收完毕的两位,控制器会根据这两位来对中断标志置位)。至于发送中断标志位TI,由于其不会影响串行口的工作过程所以在此并未列出,它将在控制器中得到体现。

串行口有四种工作方式,方式0和方式2是对时钟频率分频的结果;方式1和方式3的波特率是对定时器/计数器1的溢出率进行分频。由此可见,首先必须要解决的问题就是设计分频器。由于在方式0下,串行口是作半双工的同步移位寄存器使用,其发送和接收的波特率是一样的,因此对于方式0,串行口内部的分频信号只需要一路即可。但是对于其他方式,串行口均是工作在全双工的状态下,因此,每种方式下均需要两路分频信号。分频器的设计在上已经述及,在此不加赘述。对于方式1和方式3,其分频的对象都是定时器/计数器1的溢出率,且分频的系数是一样的。由于串行口只有一个,它不可能同时工作在方式1和3,因此方式1和方式3可以共用分频信号。要对定时器/计数器1的溢出率进行分频,首先必须测出其频率,为此需要一个上升沿的检测器来监测外部输入的定时器/计数器1的溢出信号(图3中的右图中的TF_I引脚),这样的检测器同样可以用双稳态触发器来实现。检测器在监测到TF_I引脚的上升沿时就使其输出信号保持一个时钟周期的高电平,再来另外设计计数器对此高电平进行计数,以达到对其分频的效果。

除了作为同步移位寄存器的方式0外,其他的三种方式在接收外部输入的时候均需要对外部的输入信号采样监测以确定信号的值。因此一个位检测器是必需的。同时,串行口工作在方式1、方式2和方式3时,每一个接收的数据帧都有一个起始位,这个起始位被固定为0,也就是说在输入端RXD_I监测到1到0的负跳变就会启动接收过程(注:负跳变检测器对外部输入引脚的采样频率为波特率的16倍)。位检测器的设计原理是把一个接收位的时间分为16等分(以内部计数器的16个状态来表示),在计数器的7、8、9状态时,位检测器对外部输入端的值进行采样。采用3取2的表决方法来抑制噪声。如果位检测器检测到接收的第一位不是0,那么就说明它不是一帧数据的起始位,应该摈弃,接收电路复位。

至于接收和发送,这里采用有限状态机的方式来实现。由于要工作在全双工模式下,所以接收和发送要采用两个有限状态机,有限状态机的每一个状态用来发送/接收移位数据,发送和接收的具体实现方式是移位【3】。移位的时钟来自上面所述的分频器,也就是根据各自的波特率进行。限于篇幅,在此不再详述。

3.4控制器模块

控制器的设计是MCS-51单片机IP核设计中最复杂的部分,也是设计中最重要的组成模块。控制器的将分为两个模块来实现。一个模块(在此命名为control_mem)主要用于与存储器(包括内部RAM,特殊功能寄存器SFR,外部RAM以及程序存储器)的控制。另一个模块(在此命名为control_fsm)主要用来实现指令系统。control_mem以时序电路的方式来实现,它的作用是根据状态机传来的各种控制指令来对相应的存储器进行操作。本状态机的主控时序进程是control_mem模块中的一个以时序逻辑电路现实的进程。它的启动由control_mem模块的相应输出信号来实现,启动后每经过已过状态,其输出的信号就会部分改变,这些改变就会指示control_mem下一步的动作,如此周而复始。下面简要介绍一下二者的实现原理。

control_mem模块的主要任务是根据状态机的相应指令,实现对存储器的相应操作。其总共要完成7个任务(7个任务分别以7个进程来实现,除前3个以时序逻辑电路的方式来实现外,后面的4个进程全部是以组合逻辑电路的方式来实现的。),分别是:

1.监测各个中断源的变化。使指示中断源有变化的相应信号位置位。监测外部引脚的变化的方法,一个简单的双稳态触发器就可以实现。

2.根据状态机的指令写一些用户没有直接地址的芯片内部辅助寄存器。它主要的作用是作为状态机的主控进程,同时它也会根据状态机的状态置位相应的内部辅助寄存器(例如:指示高、低优先级的中断是否正在运行的寄存器等)。同时,取指令也是在本进程中实现的。

3.写内部RAM和SFR,包括写“字节”和写“位”。它由时序逻辑电路来实现,写“位”和写“字节”的控制信号由状态机给出,每次写操作均由时钟上升沿触发。

4.根据检测中断源的变化的结果,在必要时向状态机发送中断请求类别指示信号。它是一个纯组合逻辑电路,进程1中一旦监测到中断源有变化,它的输出信号(与状态机相连接)就会改变,从而指示状态机进入中断。

评论