基于SOPC的频谱分析仪设计与研制

基于NIOS核处理器(包括I2C总线模块)和Altera公司FPGA设计制作的频谱分析仪,可用于工程指标的监测和诊断。设计的关键模块有:I2C总线控制的数据采集模块、FFT模块、FFT控制模块、Avalon总线接口及Atlantic总线接口模块以及VGA、LCD显示部分。

频谱分析仪的核心是DFT及快速算法FFT。FFT主要分为基2、基4等固定几何结构,设计采用基2几何结构、512点的FFT算法。设计平台为Altera公司推出的Cvclone II,其为高性能结构体系的PLD器件,其中包括FFT IP Core(知识产权核)。同时,Quartus II(Altera公司开发的IDE)软件具有很强的硬件仿真和逻辑分析功能,可将Verilog HDL描述的硬件综合到FPGA的整体设计中。

2 结构设计

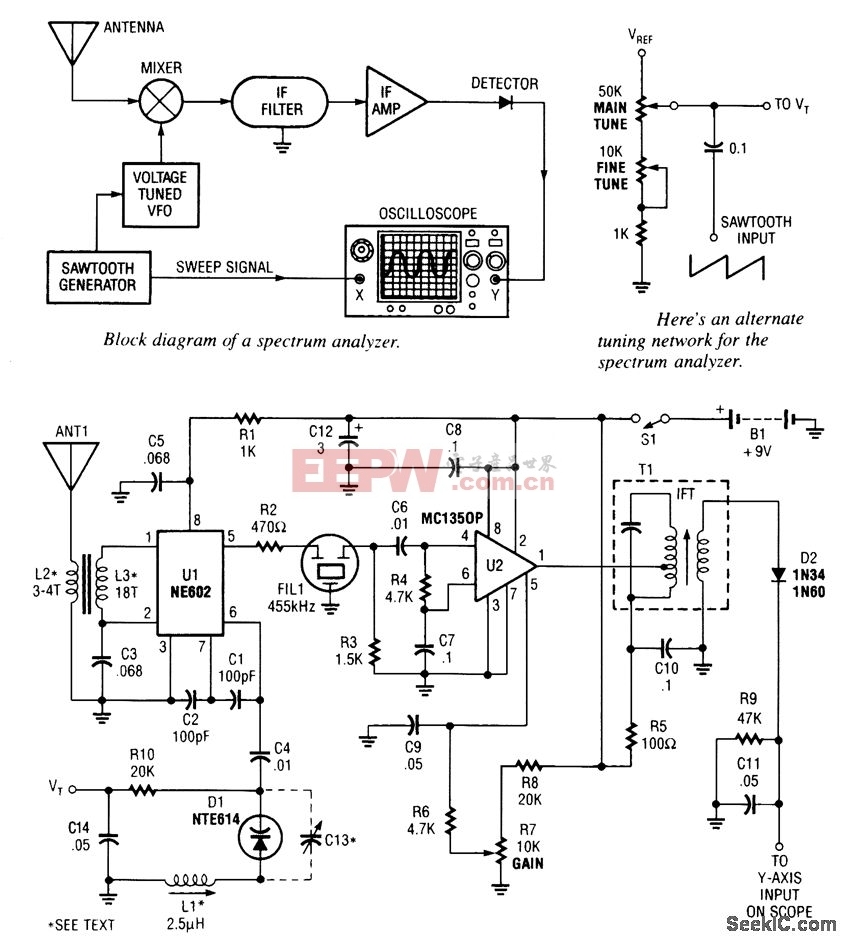

频谱分析仪的系统框图如图1所示,其主要模块包括:I2C总线模块、FIFO模块、平方求和模块、FFT模块、VGA模块、显示器等组成闭。

频谱分析仪的硬件原理框图如图2所示,图2包含FPGA的内部硬件电路及外围接口模块。

软件设计的实现是建立在NIOS II IDE的基础之上,整个软件设计总体分为4大任务:设计主任务、A/D采集控制、Flash存储任务和VGA控制显示器显示任务。

3 系统设计

设计中,充分利用了SOPC技术的优势实现软、硬件协同设计,在尽可能短的时间内实现仪器功能,分别从硬件设计和软件设计两方面详细说明设计过程。

3.1 仪器硬件设计

3.1.1 核设计简介

利用SOPC Builder在NIOS指令系统中集成了A/D转换控制、I2C总线控制、VGA控制、FFT控制等控制模块,图3为SOPC Builder集成IP。

评论