以有源电感为负载的CMOS宽带LNA设计

关键词:有源电感,CMOS,宽带低噪声放大器

一、前言:

随着RF通信系统市场的增长,越来越多的RF器件用MOS工艺实现,包括电感和电容。就电感而言,目前的多数研究集中于片上无源电感的实现和建模。 无源电感大多用来获得较好的匹配和功率增益[1],尽管通过使用立体电感或是微机电工艺可以克服片上无源电感的低Q等缺点,却无法解决其占用面积过大的缺点。在低噪声放大器中,一个1~2nH的电感所占用的面积可能超过其余全部有源器件所占面积之和。而且,一个良好片上无源电感的实现常常要求一些特殊工艺,难以与主流的数字MOS工艺兼容。因此,在噪声要求并非十分严格而对面积和价格更为关注的情况下,采用有源电感是一种不错的选择。

在片上实现有源电感的研究已经进行多年,有源电感主要用于带通滤波器和低噪声放大器部分。但因为噪声、电感Q值低以及功耗等问题,有源电感在低噪声放大器中的应用亦不多见,主要还处于研究阶段。Jhy-Neng Yang等在2001年提出了一种改进的高Q值有源电感[2],解决了Q值及功耗问题。然而却有S11与S21峰值重叠的问题。在Jhy-Neng Yang等人于2003年提出的高Q值有源电感为负载的宽带LNA中[3],尽管解决了S11与S21峰值重叠的问题,却大大增加了噪声(达到8dB)。本文基于以上两文的研究,对有源电感作了改进,设计了一个基于CMOS工艺的以有源电感为负载的宽带低噪声放大器,在满足功耗及增益指标的情况下解决了S11与S21峰值重叠的问题并得到较好的噪声指标(不超过5dB)。

文章第二部分介绍有源电感的设计原理,第三部分介绍以有源电感为负载的宽带低噪声放大器的设计,最后给出所设计电路与已有的电路的性能参数比较。

二、有源电感原理

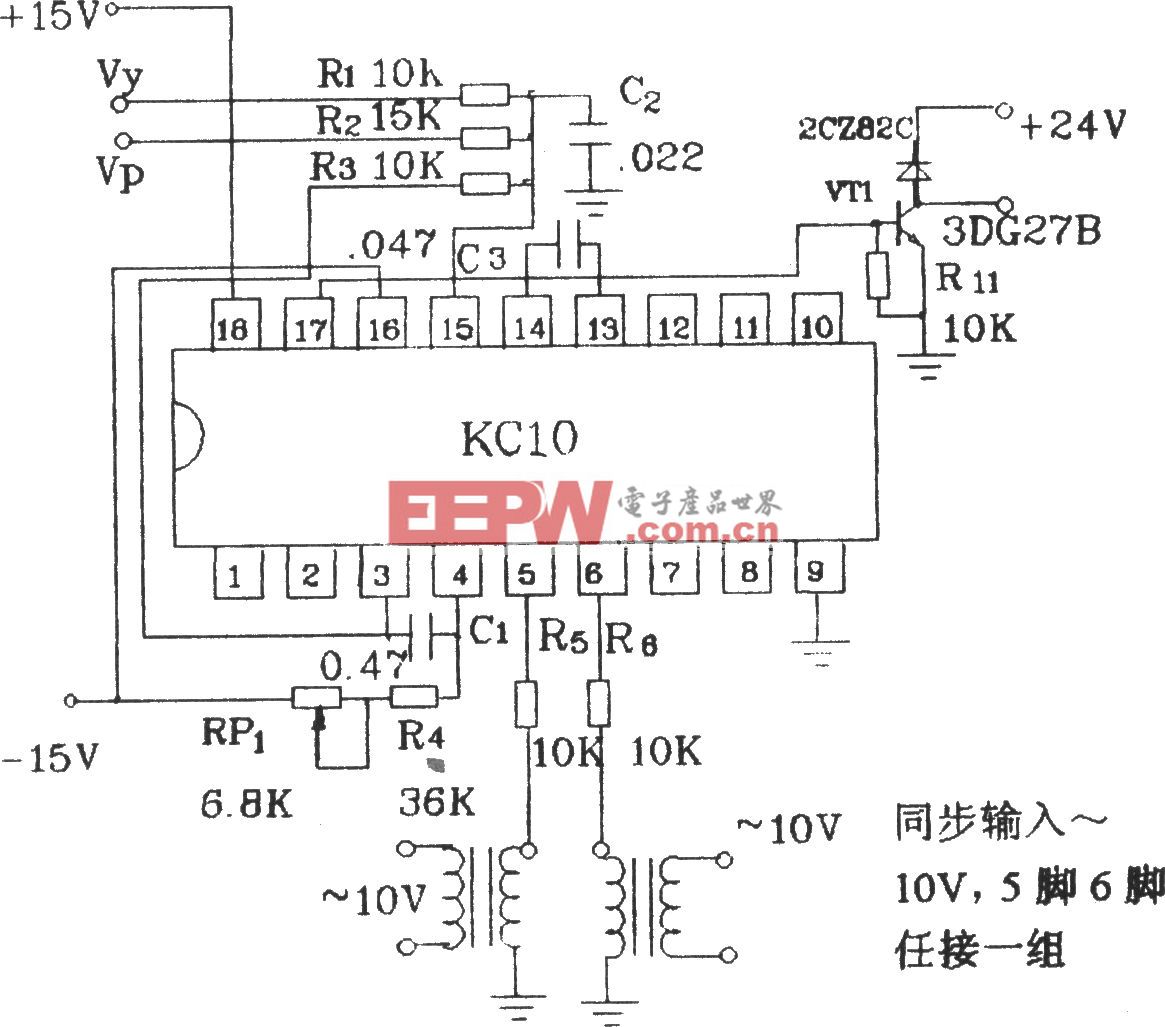

图1:有源电感原理图 图2:改善增益的有源电感

目前对CMOS有源电感的等效模型的研究已较多。典型的简单的级联CMOS有源电感如图1所示。此电路利用了器件的寄生参数。分析电路的等效小信号模型,可得[4]:

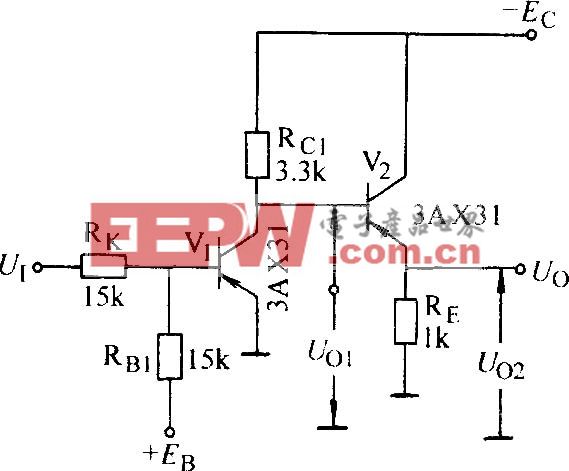

为了提高电路的增益并增加带宽,考虑在M1上级联一个MOS管。得到图2。此外亦有另外增加一个M4以增加Q值的调节度的方法,如图3。但是,不论使用何种结构,其电感等效电路都等效于图4。

其中:

寄生电阻主要由M2决定。

三、以有源电感为负载的低噪声放大器的设计

为了得到性能指标较好的以有源电感为负载的LNA,本文对Jhy-Neng Yang等人提出的有源电感形式进行了改进。文献[2]以差分形式的电感取得更好的增益,而文献[3]是以单端电感形式实现了LNA的设计。为在较好的噪声系数下分离S11与S21的峰值,本文提出了不对称的双端有源电感形式。

LNA的可选构架包括共栅结构和共源结构。由于这里要设计的是宽带LNA,并使其面积尽可能小,因此我们依然选择了共栅结构。

一般LNA的输入源(如微带天线,传输线)的输出阻抗为50欧。为获得最大功率且不在电路中产生反射,即得到最小S11及VSWR,LNA的输入阻抗应为50欧。对于共栅放大器:源端输入阻抗为1/gm。那么只要选择适当的器件尺寸和偏置电流,共栅放大器就可获得50欧源端输入阻抗。

图5:设计的有源电感为负载的宽带LNA

以有源电感为负载的LNA如图5所示。对于图5电路,MINPUT完成输入功能。M1~M5、MININ和MTL实现有源电感。M3和M4主要影响增益,而其中M5反馈系统的增加可以降低电感的寄生电阻值,有益于输入输出的50欧姆匹配,而M1~M4则有利于对电感各项参数,如Q值和带宽等进行调节,但同时更对输入输出的匹配产生影响,适当调节其栅宽,可以改善S参数并分离S21和S11的峰值。MS2和MSF作为输出缓冲,完成输出阻抗变换。RL为50欧负载。而MS1与MS2都与输入端相连,对输入阻抗产生影响。其中MS1作为输入管MINPUT的偏置,对功耗影响很大。设计时必须在功耗及S参数值间取得折中。

四、仿真结果

采用0.35um工艺对电路进行仿真。得出仿真结果如图6所示。可以看出,本文提出的设计成功的分离了S11与S21的峰值点。S11的峰值基本被抑制,波形与一般的共源结构LNA的S11的波形相似,且在整个通带内都满足S11-10dB的要求。而S22尽管在2GHz处出现峰值,却在依然整个通带内保持在-13dB以下。与此同时,LNA的噪声系数在3dB带宽内保持在3.6至4.9dB,大大优于文献[3]中的8dB值,基本满足宽带LNA的要求。而电路的功耗亦保持在20mW,与文献[3]中的功耗相当。将仿真结果与国际上一些已完成项目做比较,如表1。

图6:宽带LNA仿真结果

表1:LNA性能参数比较

NF/dB | S11/dB | S21/dB | 有源电感 | 3dB带宽/GHz | 工艺/um | 功耗/mW | |

本文 | 3.6~4.9 | -12~-17 | 10 | 是 | 1.1 | 0.35 | 20 |

文献[5] | 2.1 | -4~-5 | 15~12 | 否 | 1 | 0.18 | 23.2 |

文献[6] | 4.8 | -16 | 8 | 否 | 0.8 | 0.24 | 10 |

文献[7] | 3 | -6~-12 | 8-4 | 否 | 1 | 0.35 | 20 |

文献[8] | 3.9~4.3 | -15.11~-18 | 16.4~16.98 | 否 | 1.7 | 0.18 | 21 |

文献[9] | 3.9 | -7~-16 | 28 | 否 | 1.4 | 0.13 | 3.9 |

文献[10] | 2 | 19.2 | 是 | 窄带 | 0.3 | 40.8 | |

文献[3] | 8 | -17 | 20 | 是 | 1 | 0.25 | 18 |

五、结论:

本文设计了一种以有源电感为负载的宽带低噪声放大器,采用有源电感代替片上螺旋电感,大大缩小了芯片面积。在权衡各项指标的情况下得到较为理想的性能参数,并得到HSPICE仿真结果论证。S21达到10dB,电压增益为17dB。在3dB带宽内,S11在-12~-17之间,NF在3.6至4.9之间。通带的反向隔离大于40dB,S21亦在-14dB以下。

【参考文献】

[1] 陈伟,刘和光.基于Matlab的RF系统阻抗匹配设计[J].微计算机信息,2006,4-2:116-117。

[2] J.N. Yang, Y. Ch. Cheng, T. Y. Hsu et. Al, “A 1.75GHz Inductor-less CMOS Low Noise Amplifier With High-Q Active Inductor Load”, Circuits and Systems,2001. Vol. 2, Page(s):816-819.

[3] J.N. Yang, Y.Ch Cheng; Chen-Yi Lee; “A design of CMOS broadBand amplifier with high-Q active inductor”, System-on-Chip for Real-Time Applications, 2003. Proceedings. The 3rd IEEE International Workshop on 30 June-2 July 2003 Page(s):86 - 89

[4] A. Thanachayanont and A. Payne, “VHF CMOS integrated active inductor,” IEEE Electron. Lett., 1996.vol. 32, (11),pp. 999-1000.

[5] M. Madihian, H. Fujii. H. Yoshida, H. Suzuki, and T. Yamazaki, “A 1~10GHz 0.18 um CMOS Chipset for Multi-Mode Wireless Applications,” IEEE Microwave Symposium Digest, 2001.vol. 3, pp. 1865-1868.

[6] D. Mukhejee, J. Bhattacharjee, S. Chakrahony, and J.Laskar, “A 5-6GHz Fully-Integrated CMOS LNA for a Dual-Band WLAN Receiver,” IEEE Radio and Wireless Conference,2002. pp. 213-215.

[7] T. P. Liu, “5GHz CMOS Radio Transceiver Front-End Chipset,” IEEE Journal of Solid-State Circuits, 2000.vol. 35, (12),pp.1927-1933.

[8] Vishwakarma, S.; Sungyong Jung; Youngjoong Joo; “Ultra wideband CMOS low noise amplifier with active input matching”, Ultra Wideband Systems, 2004. Joint with Conference on Ultrawideband Systems and Technologies. Joint UWBST IWUWBS. 2004 International Workshop on 18-21 May 2004 Page(s):415 - 419

[9] Gaubert, J.; Egels, M.; Pannier, P.; Bourdel, S.; “Design method for broadBand CMOS RF LNA”, Electronics Letters, 2005.Vol.41,(7),Page(s):382 C 384.

[10] Pascht, A.; Fischer, J.; Berroth, M.; “A CMOS low noise amplifier at 2.4 GHz with active inductor load”, Silicon Monolithic Integrated Circuits in RF Systems, 2001. Digest of Papers. 2001 Topical Meeting on 12-14 Sept. 2001 Page(s):1 C 5.

评论