Sobel边缘检测的FPGA实现

随着设计复杂度的增加,使用IP核已经成为一种常用的设计方法。QuartusⅡ软件提供的Megafunt-tions是基于Altera底层硬件结构最合理的成熟应用模块,在代码中使用Megafunctions这类IP资源,不但能将设计者从繁琐的代码编写中解脱出来,更重要的是,在大多数情况下Megafunctions的综合和实现结果比用户编写的代码更优。而且只需要简单地设置选取宏功能模块的相关参数就可以在程序中调用它们,因此宏功能模块的使用也十分方便。QuartusⅡ的Mega-functins中包含有算术运算(Arithmetic)、逻辑门(Gates)、I/O、存贮器(Storage)等四个系列,可以根据系统设计需求灵活选用。

在实时图像处理中,用Sobel算子进行物体的边缘检测是经常用到的算法,由于对处理速度要求较高,因此用纯软件的方法很难达到要求。而FPGA对同时可完成的处理任务几乎没有限制,适合高速、并行信号处理,并且FPGA密度高、容量大,有内置存储器、容易实现,所以FPGA广泛用于实时图像处理系统中。

在此通过调用基于RAM的移位寄存器altshifttaps、可编程乘加器altmult add、可编程多路并行加法器parallel_add和参数化绝对值运算模块lpm_abs,实现了基于FPGA的Sobel边缘检测。最后给出设计系统的仿真结果,通过与Matlab仿真结果相比较,可以看出该设计获得了很好的边缘检测效果。

1 Sobel边缘检测算法

图1给出了Sobel边缘检测算法框图。从图中可以看出对一副图像进行Sobel边缘检测时首先要利用Sobel算子计算出水平梯度和垂直梯度,然后再把两个方向的梯度结合起来,最后应用门限处理模块判断图像边缘并输出边缘检测结果。

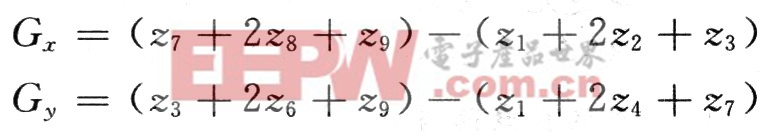

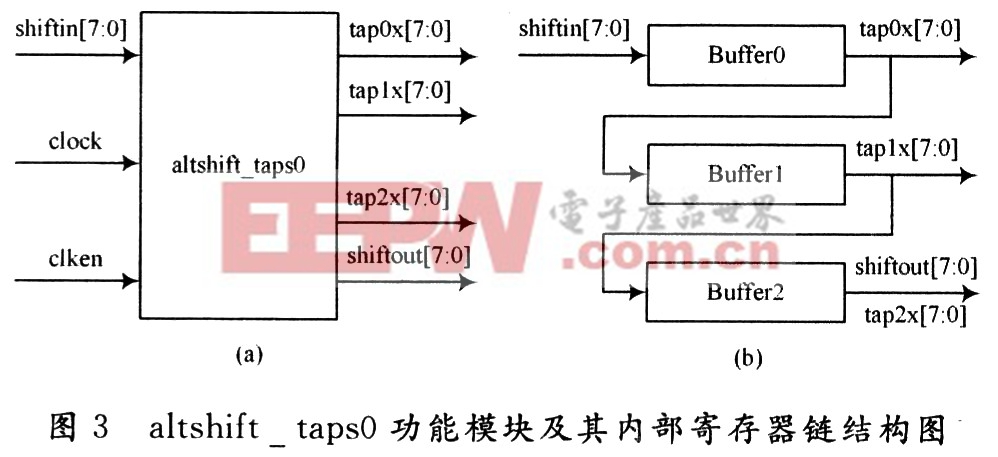

图2(a)为一副图像的3×3区域,图2(b)和图2(c)分别为Sobel算子的x方向(垂直方向)梯度算子和y方向(水平方向)梯度算子。当采用Sobel算子对图2(a)所示的3×3区域做梯度计算时,可得标记为z5的像素点x方向梯度和y方向的梯度分量分别为:

梯度的计算需要Gx,Gy这两个分量按公式![]() 联合使用。然而实际执行时,为了运算方便可以采用公式

联合使用。然而实际执行时,为了运算方便可以采用公式![]() f△|Gx|+|Gy|对梯度进行近似。

f△|Gx|+|Gy|对梯度进行近似。

该设计在门限处理时,采用基本全局门限:当某像素点(x,y)的梯度值XXXXf(x,y)大于或等于设定的门限T时,规定该点的灰度值为255,反之则为0。即:

2 Sobel边缘检测的硬件实现

根据图1所示的Sobel边缘检测算法框图,可得FPGA硬件实现Sobel边缘检测时应该包含梯度计算模块和门限处理模块。此外在硬件实现时还要采用图像数据缓冲模块对图像做缓冲处理,以便进一步对图像数据做模板处理。门限处理模块可以通过编写VerilogHDL代码实现。以下主要介绍图像数据缓冲模块和梯度计算模块。

2.1 图像数据缓冲模块器

在图像的空域滤波中,为了得到3×3的方形模板窗,常使用FIFO(First In First Out)模块作为图像数据的缓冲器。这里通过应用基于RAM的移位寄存器宏模块altshift taps实现了同样的功能,而且还省去了一些控制信号,使用十分方便。

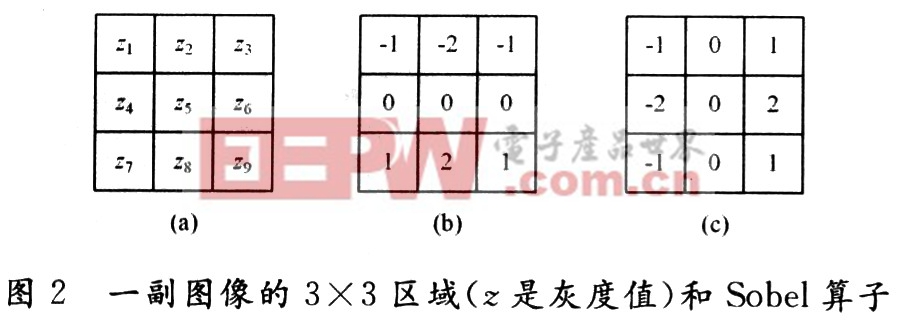

altshift_taps宏功能模块是一个可配置的、具有抽头(Taps)输出的移位寄存器,每个抽头在移位寄存器链的指定位置输出数据。图3(a)和图3(b)分别为定制的8位输入/8位输出、3抽头,且相邻两个抽头相距256个寄存器的altshift_taps0功能模块及其内部寄存器链结构图,图3(b)中的Buffer0,Buffer1,Buffer2分别为由256个8位移位寄存器构成的寄存器链。当图像的第N行数据在像素时钟同步下从shiftin[7:0]端输入到altshift_taps0的Buffer0后,随着第N+1行图像数据输入到Buffer0中,第N行的图像数据依次存入Buffer1中,而当第N十2行图像数据存入Buffer0后,Buffer1和Buffer2中分别存放的是第N+1行和第N行的图像数据,从而实现缓冲图像数据的功能。这样在像素时钟的同步下,第N+2,N+1,N行的同一列数据分别从tap0x[7:0],taplx[7:0],tap2x[7:0]端输出给梯度计算模块,进行梯度计算。

2.2 梯度计算模块

Sobel边缘检测中,图像像素点梯度的计算可由So-bel算子与图像像素卷积运算的输出经梯度计算公式计算获得。图5是图4所示的3×3空间滤波模板与图2(a)所示的3×3图像区域卷积运算的原理图。从中可以看出,为了实现卷积运算需要做乘法和加法运算,之前的文献中大都采用分立的D触发器和加法器以及乘法器来完成卷积运算,它的结构复杂。在此采用可编程乘加器altmult_add模块和可编程多路并行加法器par-allel_add模块实现卷积运算,大大简化了设计。

评论