亚微米CMOS电路中VDD-VSSESD保护结构设计(二)

3 仿真分析及具体设计结果

本文引用地址:https://www.eepw.com.cn/article/185950.htm3.1 仿真分析

在亚微米的ESD结构的设计中,一种常见的具体的ESD瞬态检测电压如图2 VDD-VSS间的电压钳位结构。其原理如下:

主要利用结构中的RC延迟作用,一般T=RC被设计为100ns-1000ns之间,而ESD脉冲通常为纳秒级,其上升时间为十几纳秒。初始状态,IC处于悬空状态下,当个正ESD电压出现在VDD电源线上,而VSS相对为0时,Vx通过RC开始充电,由于其充电常数T比VDD的上升时间大的多,致使Vx无法跟随VDD的变化,从而使P0管打开,N0管关闭,Vg电压迅速上升,N1大管开启,从而提供了一个从VDD到VSS的低阻抗大电流泄放通道并对内部的VDD与VSS有一个电压钳位作用,从而有效地保护了内部电路。 在正常上电时,因为正常的上电时间为毫秒级,所以Vx的充电可以跟随VDD变化,当上升到一定电压时,N0管开启,P0管一直关闭,Vg=0,N1管一直关断无效。

对上述例子中图2结构的具体仿真见图5、图6。

从上述仿真分析及实际的ESD结果来看,该结构本身首先必须要有一定的健壮性,其自身的健壮性则与以下两方面有关:

(1)该结构的逻辑设计,即各管子尺寸的设计,以保证该结构在正常上电时能完全关断,使电路正常工作,当ESD发生时能有效开启,从而保护内部结构。通常T=RC的值的设计要在100ns-1000ns之间,R可由倒比管或阱电阻实现,而C可直接由MOS电容构成,P0、N0管的宽长比W/L不用很大,其沟长比内部最小沟长稍大,该结构因为承受了ESD大电流泄放通道的任务,N1管的宽长比4W/L要比较大,在不影响面积的情况下尽可能大,管子沟长比内部最小沟长大。

(2)该结构的版图设计非常关键,其设计不当就可能导致自身的损坏。特别是N1管子版图设计,其漏区孔距栅要有一定距离,即有一定的压舱(Ballast)电阻时电流开启泄放更均匀。

3.2 具体设计及结果

上述例子中,主要是版图的设计不当造成在ESD发生时自身结构的损坏。经过分析,对该版图结构做了一些修改优化。

原因:针对上述理论分析及例子中实际的击穿点,该结构在1000V即被击穿的原因主要是N1管的漏区孔距栅的距离d太小所致,d=1.35μm;

目标:改动尽量少的版次达到全面提升该电路的ESD性能的目标;

方案:N1管的L修改为1.2μm,d修改为3μm,改动的版次为多晶版和孔版;

结果:I/O-VDD、I/O/-VSS、I/O-I/O模式下,最低的P95可达到2.50kV,P50、P51、P54、P57、P84可达2.8kV,其余的I/O在3.1kV时仍然通过;在VDD-VSS模式下,当ESD加+3.40kV时,VDD-VSS间短路,所以该模式下抗ESD电压为3.1kV。

可见,通过修改优化VDD-VSS钳位结构,其图2结构自身的抗ESD健壮性大大增强,VDD-VSS的抗ESD能力提高到3kV以上,其余I/O也得到了进一步的提升,使该电路总体ESD性能提高到2.20kV以上,满足了民品电路的ESD性能要求。要进一步提高该电路的ESD性能,需要对该结构继续优化,如再增大N1管的漏区孔距栅的距离d及W/L等,其他I/O口的GGNMOS管也需要相应的优化修改,但其总面积可能会相应增加。

4 VDD-VSS两种电压钳位结构的比较

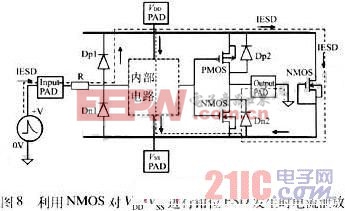

图8为一种常见的全芯片ESD保护结构的设计,左边为一个输入PAD,右边为一个输出PAD,最右边的NMOS管则是常规CMOS工艺电路中最常见的VDD-VSS电压钳位结构的设计。其设计要注意管子本身尺寸的逻辑设计,也要注意其版图的详细规则设计。它不属于电压检测电路。在电路正常工作时,相当于一个反向二极管;当有ESD发生时,则NMOS管漏区的PN结反向击穿,寄生的NPN导通从而泄放大电流并使VDD-VSS间的电压钳位。

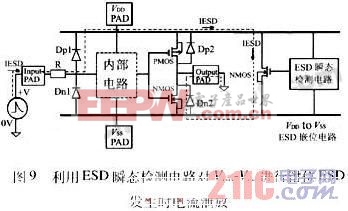

图9中最右边的VDD-VSS电压钳位结构的设计则为一种ESD瞬态检测电路,该电路一种详细的设计方案即为图2的结构设计。具体作用上面已经进行了详细的分析阐述。主要是比较一下图8、图9两种VDD-VSS电压钳位结构的优劣。

在ESD发生时,两个结构对VDD-VSS都有电压钳位作用,关键是各自电流的泄放能力的差异。一般管子的正向导通比反向击穿能力耐更高的ESD电压,承受更大、更低阻抗的ESD电流,且ESD电流泄放更均匀。在亚微米CMOS IC中,VDD-VSS直接的GGNMOS大管可能不足以耐较高的ESD电压,该结构更有利于ESD性能的提升,同时其版图设计面积也更大。只有在亚微米以下的CMOS电路的设计中,才需要考虑。

5 全芯片ESD保护结构的设计

如要进一步优化电路的抗ESD性能,需要从全芯片ESD保护结构的设计来进行考虑,在亚微米全芯片ESD保护结构的设计中,不仅要设计每个I/O对VDD、VSS直接的保护结构,以提供外围直接的ESD低阻抗大电流泄放通道及对内部电压钳位,更要重点设计全芯片外围VDD-VSS之间低阻抗大电流泄放通道及对内部VDD-VSS电压的钳位,如上述例子中若去掉图2的结构,则I/O-VDD(VSS)的ESD性能下降许多,特别是对于面积较大、特征尺寸较小的电路,电源线、地线走线较长,则电路的不同位置电源线、地线对VDD、VSS根部有较大的电阻压降,在VDDPAD上出现ESD脉冲时,距VDDPAD较远的电源线上就有了一定的RC延迟,所以即使完全相同的ESD保护结构,由于每个I/O PAD距VDD、VSSPAD位置的不同,其ESD性能也不完全相同,离VDD、VSS近的I/O口ESD性能更好,反之较差,上述例子中优化改版后,有几个管脚如P95、P51、P54等抗ESD变的更差就与其位置离VDD、VSS最远有关,若在芯片的左下角再加一个VDD-VSS如图2的保护结构,则全芯片的抗ESD性能会得到进一步的提高。

在全芯片的ESD结构设计时,注意以下关键几点:

(1)外围VDD、VSS走线尽可能宽,减小走线上的电阻;

(2)设计一种VDD-VSS之间的电压钳位结构,且在发生ESD时能提供VDD-VSS直接低阻抗电流泄放通道,如文章所述的结构。对于面积较大的电路,最好在芯片的四周各放置一个这样的结构,若有可能,在芯片外围放置多个VDD、VSSPAD,也可以增强整体电路的抗ESD能力;

(3)外围保护结构的电源地的走线尽量与内部走线分开,外围ESD保护结构尽量做到均匀设计,避免版图设计上出现ESD薄膜环节;

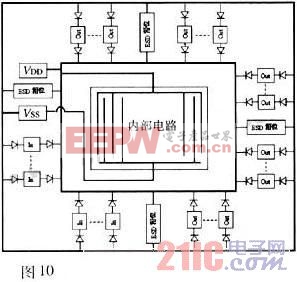

(4)ESD保护结构的设计要在电路的ESD性能、芯片面积、保护结构对电路特性的影响如输入信号完整性、电路速度、输出驱动能力等进行平衡考虑设计,还需要考虑工艺的容差,使电路设计达到最优化。一个全芯片的ESD保护结构的设计见图10。

在实际设计的一些电路中,如0.8μm以上的电路中,有时没有直接的VDD-VSS电压钳位保护结构,此时,VDD-VSS之间的电压钳位及ESD电流泄放主要利用全芯片整个电路的阱与衬底的接触空间。所以在外围电路要尽可能多地增加阱与衬底的接触,且N+P+的间距一致。若有空间,则最好在VDD、VSSPAD旁边及四周增加VDD-VSS电压钳位保护结构,不仅增强了VDD-VSS模式下的抗ESD能力,也增强了I/O-I/O模式下的抗EESD能力,且自身的抗ESD能力要具有很强的健壮性,避免自身可能首先被ESD击穿损坏从而成为全芯片的最薄弱环节。

6 总结

对于深亚微米超大规模CMOS IC的ESD结构设计,常规的ESD保护结构通常不再使用了,通常大多是深亚微米工艺的Foundry生产线都有自己的外围标准的ESD结构提供,有严格标准的ESD结构设计规则等,设计厂商只需调用其结构就可以了,这可使芯片设计师把更多精力放在电路本身的功能、性能方面的设计等。

更多资讯请关注:21ic模拟频道

DIY机械键盘相关社区:机械键盘DIY

评论