Altera的Stratix SoC为何不加ADC?

—— FPGA业过去二三十年都在考虑这个问题

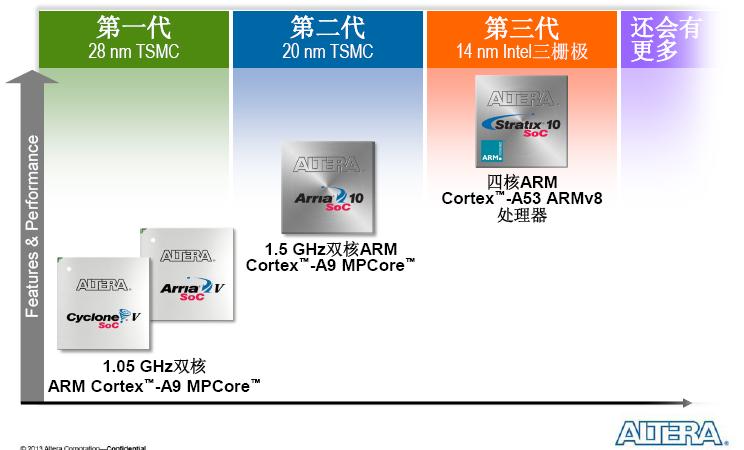

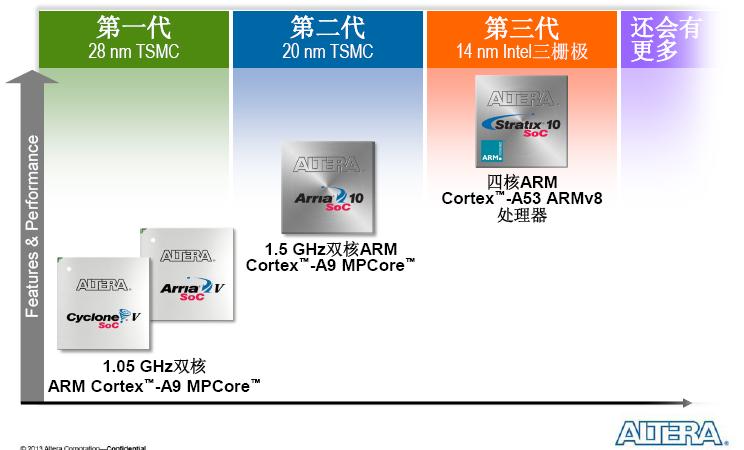

2013年10月30日,Altera公司在其SoC上进行了重大发布,宣布将推出第三代处理器系统,采用Intel 14nm三栅极工艺制造的Stratix 10 SoC器件将具有高性能四核64位ARM Cortex-A53处理器系统 [1]。不过,我们注意到,不像其同行竞争对手加入了高精度的Delta-Sigma ADC,Altera的SoC还是纯数字,仍然没有集成ADC。

Altera嵌入式处理营销资深总监Chris Balough告诉《电子产品世界》编辑,首先,增加什么功能,主要看客户的需求,不仅是芯片上要不要放ADC,所有的功能都要考察,例如是用于军用、通讯、消费者,还是计算、存储设备、工业或汽车?如果大部分的客户都说我们不需要这个功能,或者是70%的客户需要的功能,Altera才会考虑是否增加这样的功能。

实际上,FPGA业过去二三十年都在考虑这个问题:要不要加ADC?发现加ADC这个主意挺好的,但在实施过程中到底怎么构建这个ADC?有的需要8位的,有需要16位的,有的需要32位的,有的需要高速的,有的需要精密型的——客户的需求非常不同。

实际上,FPGA业过去二三十年都在考虑这个问题:要不要加ADC?发现加ADC这个主意挺好的,但在实施过程中到底怎么构建这个ADC?有的需要8位的,有需要16位的,有的需要32位的,有的需要高速的,有的需要精密型的——客户的需求非常不同。

另外,要考虑到在芯片上增加一个ADC,不仅仅是增加一个硬件成本的问题,还有测试、验证、方法、软件模块等等,还有后端测试的环境设施,这些都是花成本的。

Altera发现ADC不是大部分客户需要的,如果把它加进去,客户就会觉得我们不需要这个东西,还得为此付钱?所以,“我觉得加一个ADC不太划算。在中国也不是因为我们没有ADC我们失去了任何的机会。”Chris说。

参考文章:

[1] Altera发布Stratix 10 SoC中的四核64位ARM Cortex-A53.(2013-10-31).http://www.eepw.com.cn/article/184832.htm

评论