C6000与C2000系列DSP之间串行数据通讯的研究与实现

TI公司的TMS320LF2407为16位定点DSP微控制器,内嵌有看门狗定时器(WDT)、CAN总线控制器、模数转换器(ADC)、串行外设接口(SPI)、异步串行口(SCI)等多种外设模块,并有大量输入输出引脚(GPIO),可以满足控制系统多方面的控制需求。但由于TMS320LF2407的指令周期最短为25ns(40MHz主频),对于数据处理运算量特别大的系统,其运算速度略显不足。

多数数字图像处理应用系统既要求系统有强大的数据处理能力,以满足对图像处理的实时性要求,又要求系统有强大的控制能力,以便实现对外部众多设备的控制。在实际应用系统中,将TMS320C6711作为处理器完成数字图像的实时处理,TMS320LF2407作为控制器完成系统的控制功能,便可兼顾系统的数据处理能力与外部设备控制能力。这样的系统要求在TMS320C6711和TMS320LF2407之间建立有效的数据交换通道,本文所介绍的设计思想就是基于以上工程需要提出的。

1 系统结构

本系统为嵌入式数字图像处理系统,系统结构如图1所示。数字图像数据由下位机TMS320C6711处理,处理结果采用异步串口通讯的方式传送给上位机TMS320LF2407,TMS320LF2407将采集到的模拟量、开关量等参数,与通过异步串口接收到的图像处理结果一起通过CAN总线向远程监控终端发送。

TMS320C6711的多通道缓冲串行接口McBSP与TMS320LF2407的SCI模块,通过特定的软硬件设计可以支持使用标准格式的异步数字通讯。通讯数据的格式为:一个起始位、数据(长度可通过编程在16位~8位内可选)位、可供选择的奇/偶/非极性位、一个或两个停止位,如图2所示。

1.1 McBSP接口

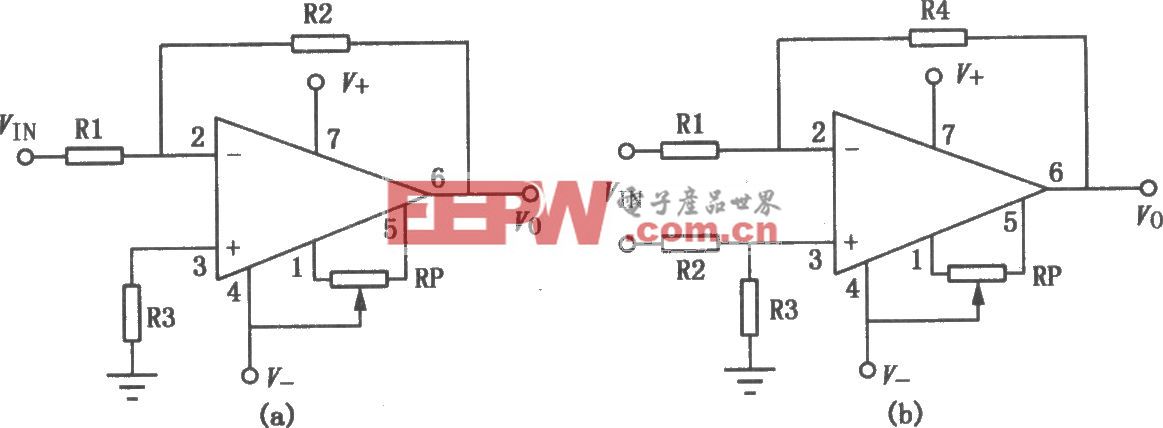

McBSP的结构框图如图3所示。McBSP可以分为数据通道和控制通道两部分。数据发送引脚(DX)和数据接收引脚(DR)分别负责数据的发送和接收,发送时钟引脚(CLKX)、接收时钟引脚(CLKR)、发送帧同步引脚(FSX)和接收帧同步引脚(FSR)提供串行时钟和控制信号。CPU和DMA控制器通过外设总线与McBSP进行通讯。当发送数据时,CPU和DMA将数据写入数据发送寄存器(DXR1,DXR2),接着复制到发送移位寄存器(XSR1,XSR2),通过发送移位寄存器输出至DX引脚。同样,当接收数据时,DR引脚上接收到的数据先移位到接收移位寄存器(RSR1,RSR2),接着复制到接收缓冲寄存器(RBR1,RBR2),RBR再将数据复制到数据接收寄存器(DRR1,DRR2)中,并通过串口事件通知CPU或DMA读取数据。这种多极缓冲方式使得片内数据通讯和串行数据通讯能够同时进行。

1.2 SCI接口

SCI模块支持CPU和其他使用标准格式的异步设备间的通讯。它具有SCIRXD(串行数据接收端)和SCITXD(串行数据发送端)两个I/O引脚。在全双工模式下具有一个发送器(包括SCITX2BUF及其主寄存器TXSHF)、一个接收器(包括SCIRXBUF及其RXSHF)。发送器在SCITXBUF存放要发送的数据,并每次一位地将数据移位至SCITXD引脚;接收时则每次一位地将SCIRXD引脚上的数据移入,载入SCIRXBUF和SCIRXEMU给CPU读取。具有一个可编程的波特率发生器,可得到超过65 000种不同的可编程速率。SCI为接收器和发送器提供独立的中断请求和中断向量:如果RX/BKINT ENA位(SCICTL2.1)被置位,当SCI接收到一个完整的帧,并把RXSHF中的数据传送到SCIRXBUF时,这个动作置位RXRDY标志(SCIRXST.6)并启动一个中断。如果TX INT ENA位(SCICTL2.0)被置位,则在任何时候,只要SCITXBUF中的数据送到TXSHF,发送器中断就会被认定,表示CPU可以向SCITXBUF写。这个动作置位TXRDY标志位,并启动一个中断。

2 硬件实现

当TMS320C6711D与TMS320LF2407A进行标准异步串行通讯时,TMS320LF2407A的SCI接口可直接支持该通讯,只需将SCI接口通过内部特殊功能寄存器配置为串行接口模式即可。而TMS320C6711D的McBSP除通过内部特殊功能寄存器配置成串行接口外,在硬件设计上还应将DR和FSR短接,并与SCI的串行数据发送引脚(SCITXD)相连。这是由于标准异步串行通讯中数据线上既包含了帧同步信息,也包含了数据信息。SCI的串行数据接收引脚(SCIRXD)与McBSP的DX相连。

由于TMS320C6711D与TMS320LF2407A的接口电压均为3.3V,二者引脚可直接相连,不需要电平转换。McBSP与SCI的串行异步通讯接口电路如图4所示。

3 软件参数的配置与计算

3.1 针对TMS320C6711D

(1)波特率的计算

TMS320C6711D内部生成的串行时钟由系统时钟频率SYSCLK和采样率发生寄存器决定。MCBSP的内部数据时钟频率即异步波特率由以下公式确定:

MCBSP异步波特率=采样率发生寄存器输入时钟频率/(CLKGDV+1)

其中:CLKGDV=采样率发生寄存器输入时钟频率/McBSP异步波特率-1。

当采样率发生寄存器的CLKSM=1时,采样率发生寄存器输入时钟频率=CPU内核输入时钟/2;

当采样率发生寄存器的CLKSM=0时,采样率发生寄存器输入时钟频率=CPU内核输入时钟。

在本系统中,TMS320C6711D的内核输入时钟为150MHz,采样率发生寄存器的CLKSM位设置为1。若使McBSP异步通讯波特率为312.5kb/s,则依据以上公式,采样率发生寄存器的CLKGDV段参数应配置为239,即十六进制的0xEF。

(2)特殊功能寄存器的初始化

TMS320C6711D内部与McBSP配置相关的特殊功能寄存器主要有:串口控制寄存器(SPCR)、接收控制寄存器(RCR)、发送控制寄存器(XCR)、采样率发生器寄存器(SRGR)、多通道控制寄存器(MCR)、接收通道使能寄存器(RCER)、发送通道使能寄存器(XCER)、管脚控制寄存器(PCR)。

TMS320C6711的McBSP与TMS320LF2407的SCI模块通讯时,系统对McBSP的配置要求为:数据为单项帧;每帧一个数据单元;数据单元字长为8bit;时钟下降沿处接收数据;在上升沿处发送数据;帧同步信号高有效;帧同步有效后,在其后的第一个时钟周期启动该帧的传输,即数据延迟为0;异步通信波特率为312.5kb/s。

根据以上控制要求,TMS320C6711D内部与McBSP相关的特殊功能寄存器的配置参数如表1所示。

3.2 针对TMS320LF2407A

(1)波特率的计算

TMS320LF2407A内部生成的串行时钟由系统时钟SYSCLK频率和波特率选择寄存器决定。串行通信接口使用16bit波特率选择寄存器,数据传输速度可以被编程为65000多种不同的方式。

不同通信模式下的串行通信接口异步波特率由下列方法决定:

BRR=1~65 535时的串行通信接口异步波特率为:

SCI异步波特率=SYSCLK/[(BRR+1)8]

其中:BRR= SYSCLK/(SCI异步波特率8)-1

BRR=0时的串行通信接口异步波特率为:

SCI异步波特率=SYSCLK/16

这里BRR等于波特率选择寄存器的16位值。

在本系统中,TMS320LF2407A的系统输入时钟为25MHz,若使SCI异步通信波特率为312.5kb/s,则依据以上公式,波特率选择寄存器参数应配置为9,即十六进制的0x0009。

(2)特殊功能寄存器的初始化

TMS320LF2407的SCI模块的异步串行通讯配置包括管脚配置、通讯模式配置和中断配置三方面,相关的特殊功能寄存器包括复用控制寄存器(MCRA)、端口数据和方向控制寄存器(PADATDIR)、串行通讯接口控制寄存器1和2(SCICTL1和SCICTL2)、通讯控制寄存器(SCICCR)、波特率选择高字节寄存器和低字节寄存器(SCIHBAUD和SCILBAUD)、优先级控制寄存器(SCIPRI)、接收状态寄存器(SCIRXST)等。

为了实现通讯波特率为312.5kb/s的标准异步数字通讯,SCI模块应配置为串行通信功能模式,并将特殊功能寄存器配置如表2所示。

4 软件设计

系统中TMS320C6711通过McBSP将图像处理结果采用主动发送的方式发送给TMS320LF2407,后者通过响应SCI中断的方式接收数据信息。这两部分软件流程框图如图5所示。

5 串行通讯初始化程序

TMS320C6711与TMS320LF2407进行串行通讯的软件设计难点是McBSP与SCI的初始化程序设计。初始化程序包括对芯片的管脚配置、通讯模式配置和中断配置等方面。以下分别给出TMS320C6711的McBSP模块和TMS320LF2407的SCI模块的初始化程序模块。

(1)TMS320C6711的McBSP模块初始化程序

voidinit_mcbsp0_master(void)

{

MCBSP_Config mcbspCfg0=

{

0x00010001,//配置spcr寄存器

0x000D0000,//配置rcr寄存器

0x00040020,//配置xcr寄存器

0x200000ef,//配置srgr寄存器,

//波特率设定为312.5kb/s

0x00000000,//配置mcr寄存器

0x00000000,//配置rcer寄存器

0x00000000,//配置xcer寄存器

0x00000b0c//配置pcr寄存器

};

hMcbsp0=MCBSP_open(MCBSP_DEV0, MCBSP_OPEN_RESET);

//选用port 0

MCBSP_config(hMcbsp0,mcbspCfg0);

IRQ_map(IRQ_EVT_RINT0,13);//映射接收中断0为

//13号中断

IRQ_reset(IRQ_EVT_RINT0);

IRQ_enable(IRQ_EVT_RINT0);//开中断

MCBSP_enableRcv(hMcbsp0);

MCBSP_enableSrgr(hMcbsp0);//Handle to SRGR

MCBSP_enableFsync(hMcbsp0);

}

(2)TMS320LF2407的SCI模块初始化程序

void sci_INIT(void)

{

MCRA=MCRA|0x0003; //设置引脚SCITXD/IOPA0和

//SCIRXD/IOPA1为串行通讯功能

PADATDIR=0X0100; //设PA口为输入口

SCICTL1=0x13;//使能接收和发送

SCICTL2=0x02; //禁止发送中断,使能接收中断

SCICCR=0X07; //8位字长,1个停止位,空闲线多处

//理器模式,无奇偶校验

SCIHBAUD=0x00; //波特率设为312.5kb/s

SCILBAUD=0x09;

SCIPRI=0x00; //接收为高优先级中断

SCIRXST=SCIRXST0xbf;//清除SCI接收中断标志

SCICTL1=0x33; //保存设置

}

利用TMS320C6711的McBSP和TMS320LF2407的SCI可以实现异步串行数据通讯,具有电路简单、设置灵活、数据传输速度快、性能可靠稳定等特点。在此基础上可成功构建主从式双DSP数据处理系统,有效解决单一DSP系统数据处理能力与控制能力难以兼顾的问题。本文所介绍的设计方案已在实际应用系统中采用,并经长时间运行检验。实践证明,此设计方案是一种有效的多DSP数据交换手段。

评论