基于DDS的高精度函数信号发生器的研制

摘要:基于直接数字频率合成技术(DDS),采用单片机实现对DDS芯片AD9852的控制,提出一种高精度函数信号发生器的实现方案。重点介绍了单片机与AD9852的硬件接口电路、整个系统的软件设计以及单片机中对48 b频率控制字的处理方法。此方法在单片机程序设计中处理多于32 b的整型数据时具有借鉴意义。此系统具有高频率、高精度的主要特

点,且控制灵活方便,具有广阔的应用前景。

关键词:DDS;AD9852;频率控制字;信号发生器

直接数字频率合成技术(Direct Digital Frequency Synthesis,DDS)是从相位概念出发直接合成所需波形的一种新的频率合成技术。DDS技术具有相对带宽宽、频率转换时间短、频率分辨率高等优点,广泛用于高精度频率合成和任意信号发生。本文采用单片机控制DDS芯片,设计实现了一种高精度多波形的信号源。

1 DDS原理

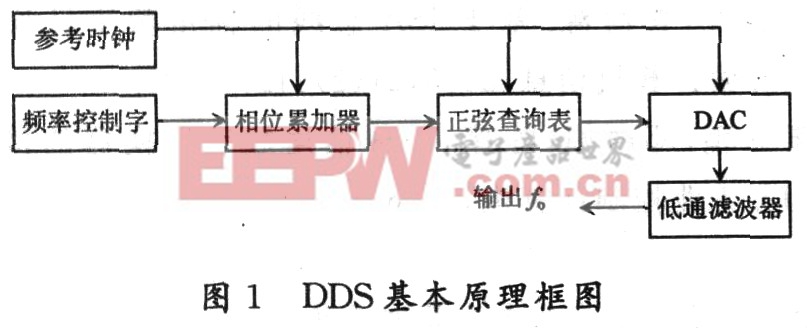

DDS的基本结构包括:相位累加器、正弦查询表、数模转换器(DAC)及低通滤波器等。DDS原理如图1所示。

图1中信号输出频率和参考时钟频率的关系表达式为:

![]()

其中:fo为输出频率,fosc为参考时钟频率,FTW为频率控制字,N为频率控制字的位数。由于N是一个固定值,那么只要改变FTW的大小就能得到所需要的频率值,而且频率的分辨率由N值决定,当N值越大则分辨率越高。由Nyquist取样定理可知,要恢复理想波形,在理想低通滤波器的条件下,输出频率必须小于时钟参考频率的用50%,即fo1/2fosc,若超过这个范围,则一阶镜像频率就会落在Nyquist带宽内。而实际的LPF都有一个过渡带的问题,所以为了更好地去除一阶镜像带来的杂散,一般将DDS的输出频率限制在O.4fosc内。可见当AD9852参考时钟频率为300 MHz时,完全可以满足输出频率为50 MHz的设计要求。

2 系统设计

2.1 硬件设计

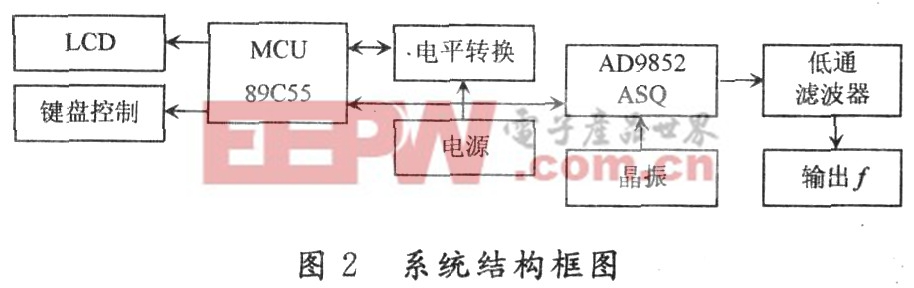

系统设计原理如图2所示。该设计选用单片机AT89C55作为控制核心,其与DDS芯片AD9852之间采用并口通信方式。单片机P1口作为LCD液晶显示的数据总线,P0口用于AD9852地址总线和并口传输的数据总线,使用锁存器74ALS573实现P0口复用,74ALS573锁存输出的六位数值为AD9852内部寄存器的地址。P2和P3口作为控制口用于键盘芯片HD7279和AD9852的控制。

由于AD9852使用CMOS工艺,供电电压是3.3V,而单片机使用的是TLL电平,所以要在TLL电路与CMOS电路之间进行电平转换。该系统选择了74LVTl6245作为5 V逻辑电平到3.3V逻辑电平的转换器件。所需要输出的频率可通过按键设定得到,进行的操作同时在液晶上进行显示。AD9852内部系统时钟频率由外部有源晶振倍频得到。

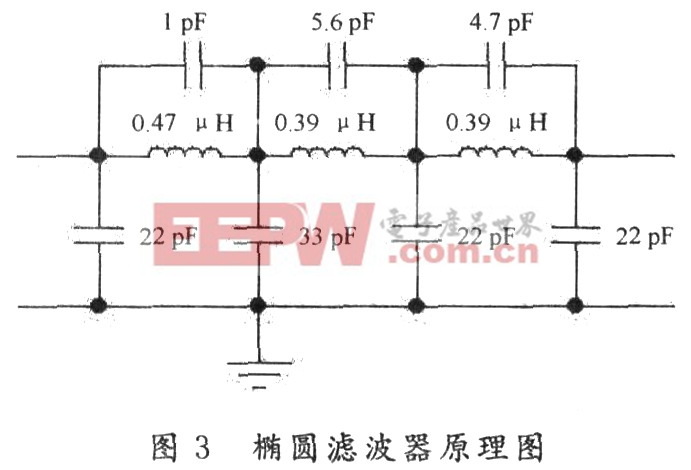

由于AD9852的内部没有低通滤波器,因此经过内部余弦DAC输出的扫频信号不可避免地含有高频噪声,所以信号输出端口需外接低通滤波器抑制高频干扰。该设计采用七阶椭园函数滤波器。七阶椭圆滤波器电路图如图3所示。

2.2 软件设计

评论