单片机与单总线A/D转换器DS2450的接口设计

时的功耗为25μW。多个DS2450或其它功能的具有MicroLAN接口的单总线芯片可以并联,CPU只需一根端口线就能与诸多单总线芯片通信,而且占用微处理器的端口较少,因此可节省大量的引出脚和逻辑电路。

1 DS2450的引脚排列和内部结构

1.1 引脚功能

DS2450采用8脚SOIC封装,其管脚功能描述如下:

1脚(VDD):工作电源接入端;

2脚(N.C):悬空引脚;

3脚(DATA):串行数据输入/输出端;

4脚(GND):接地端;

5脚(AIN-A):A路模拟电压输入端;

6脚(AIN-B):B路模拟电压输入端;7脚(AIN-C):C路模拟电压输入端;

8脚(AIN-D):D路模拟电压输入端。

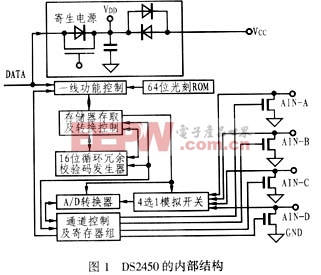

1.2 内部结构

DS2450的内部结构如图1所示。其中光刻ROM中的64位序列号是出厂前被光刻好的,它可以被看作是该DS2450的地址序列码。64位光刻 ROM的排列是:开始8位(20H)为产品类型标号,接着的48位是该DS2450自身的序列号,最后8位是前面56位的循环冗余校验码(CRC=X8+X5+X4+1);光刻ROM的作用是使每一个单总线器件的地址都各不相同,以便在一根总线上挂接多个单总线芯片。

对于一线端口,在ROM功能建立之前,其它功能是无法实现的。总线控制器必须首先通过DATA引脚为DS2450提供一个ROM功能控制命令(8位)。它的7个功能控制命令为:

(1)读ROM,命令字[33H];

(2)匹配ROM[55H];

(3)搜索ROM[F0H];

(4)跳过ROM[CCH];

(5)条件搜索ROM[ECH];

(6)超速跳过ROM[3CH];

(7)超速匹配ROM[69H]。

其中超速跳过ROM或超速匹配ROM命令执行后可使串行通信速率高达142kbps。如果多个器件连接在一线上,这些命令可对每个器件的64位ROM 部分进行操作,并挑选出一个特定的器件。然后对选中的DS2450执行下一步的A/D转换控制命令以及读写存储器命令,所有命令或数据的读/写均从最低位开始。

1.3 存储器

DS2450内部有24个地址相连的8位存储器,可将其分成3页,每页8字节。第0页为A/D转换结果存储器,每个通道占2个字节共16位。当芯片上电复位时,该页清0;第1页为A/D转换控制与状态存储器;第2页为各通道输入高/低限报警值存储器。

2 转换与读/写控制

2.1 转换控制

DS2450的转换控制首先通过其DATA端串行送出转换命令字[3CH],然后送出通道选择字和预置控制字,最后启动A/D转换器进行转换。DS2450的通道选择字和预置控制字的各位含义如表1所列。

在通道选择字中,对应位为1表示该通道参与转换。在同时选择多个通道时,其转换顺序为A→B→C→D,未选中的通道将被跳过。其A/D转换的时间可近似为:

转换时间=通道数×转换精度位数×80μs+160μs。

当所有通道转换完毕后,系统将发出读存储器命令以获得转换结果和对应的状态。

预置控制字可用于对相应通道的转换结果存储器进行预置。当SET、CLR=00时,为不预置,即保持上次转换值;当SET、CLR=01时,转换前预置为全0;当SET、CLR=10时,预置为全1;而

SET、CLR=11为无效组合。

2.2 存储器读/写控制

读存储器命令可用于读取转换结果、工作状态和门限设定值等。总线管理器首先送出读存储器命令字[AAH],然后送出两字节的16位“起始数据”存储器地址,并在总线上读取一个字节的数据后,地址自动加1,紧接着读取下一个数据;当一页读完后,随后读取的两个字节为内部自动产生的16位循环冗余校验码,它是由前面送出的命令字、地址和读取的存储器数据并根据下列表达式生成的:

CRC16=X16+X15+X2+1

写存储器命令主要针对第1页和第2页存储器,其目的是写入各通道的工作方式控制字和对应通道的高、低门限设定值。总线管理器首先送出写存储器命令字[55H],然后送出两字节的16位存储器起始地址,接着逐个送出要写入的数据,其地址也是自动加1。若在刚写完一个数据后执行读操作,读出的数据应刚好为前一次写入的数据,可利用这一特点对写入和读出的数据进行比较,以判断传输的正确性。

如果在软件校验时发现读/写中的传输错误,则必须对DS2450芯片进行初始化,并重新进行读/写操作。

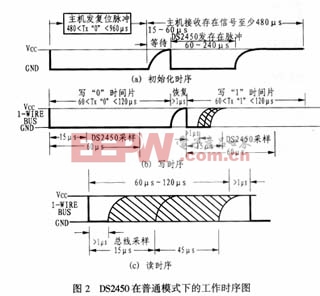

2.3 DS2450的工作时序

DS2450的一线工作协议流程是:初始化→ROM功能命令→存储器读写/转换控制功能命令→传输数据。其工作时序包括初始化时序、写时序和读时序,图2给出了普通工作模式下的工作时序。

3 DS2450与单片机的典型接口设计

图3是MCS-51系列单片机与DS2450的典型连接电路。其中DS2450的DATA端接AT89C51的P1.0,该电路采用外接电源供电方式,其DS2450的VCC端用 5V电源供电。此例仅对D通道进行A/D转换,AIN-D接模拟信号输入;AIN-A和AIN-B外接上拉电阻到电源,其输出可作为D通道的高、低限报警信号。

如果单片机系统所用的晶振频率为12MHz,那么可根据DS2450的初始化时序、写时序和读时序来分别编写三个子程序:其中INIT为初始化子程序,可用于发送复位脉冲并接收存在脉冲;WRITE为写(命令或数据字节)子程序;READ为读数据子程序。所有要读写的命令或数据字节均被放在A寄存器中。

评论