基于ISD4004单片机的火车站自动语音播报系统

笔者成功应用ISD4004和AT89C51单片机设计了火车站信号自动语音播报系统,通过对火车站铁路线的上行和下行控制、车辆调度、系统主副电源的启用等多路信号进行检测并采集,根据安全隐患的防范要求,由单片机控制查询安全警示语音信息并播报,实现安全操作提示及报警。系统在火车站信号室控制台上安装使用,运行稳定,信号播报准确,取得了很好的效果。

本文引用地址:https://www.eepw.com.cn/article/173248.htm1 硬件电路设计

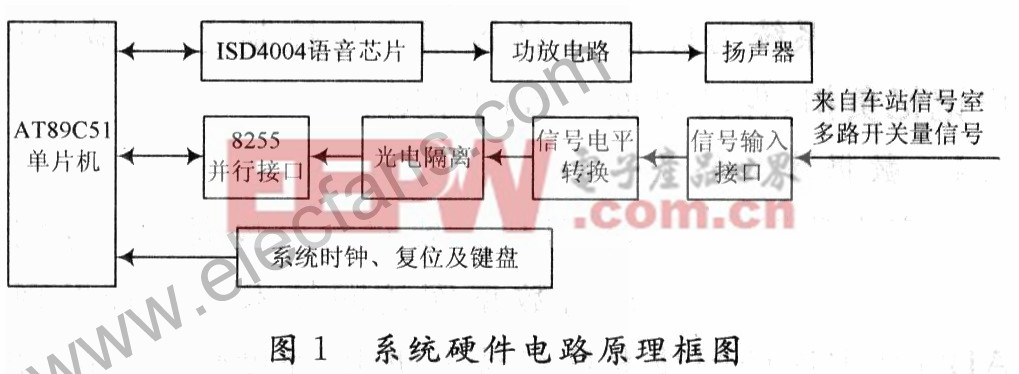

系统硬件电路设计原理框图见图1,由微控制器AT89C51、ISD4004语音电路、音频功率放大电路、可编程并行接口8255、光电隔离、电平转换、信号输入接口、系统时钟、复位及键盘等单元电路组成。

1.1 ISD4004的特性

ISD4004系列语音存储芯片采用CMOS技术,内含振荡器、防混淆滤波器、平滑滤波器、音频放大器、自动静噪及高密度多电平闪烁存贮陈列,内置微控制器串行通信接口。芯片所有操作必须由微控制器控制,操作命令可通过串行通信接口(SPI或Microwire)送人。外部的音源信号在芯片内采用多电平直接模拟量存储技术,信息可进行多段处理,每个采样值直接存贮在片内闪烁存贮器中,因此能够非常真实、自然地再现语音、音乐、音调和效果声。存于片内闪烁存贮器中的信息,可在断电情况下保存100年。芯片工作电压为3 V,工作电流为25~30 mA,维持电流1μA,不耗电,单片录放时间8~16 min,可反复录音10万次。

1.2 ISD4004的引脚及封装形式

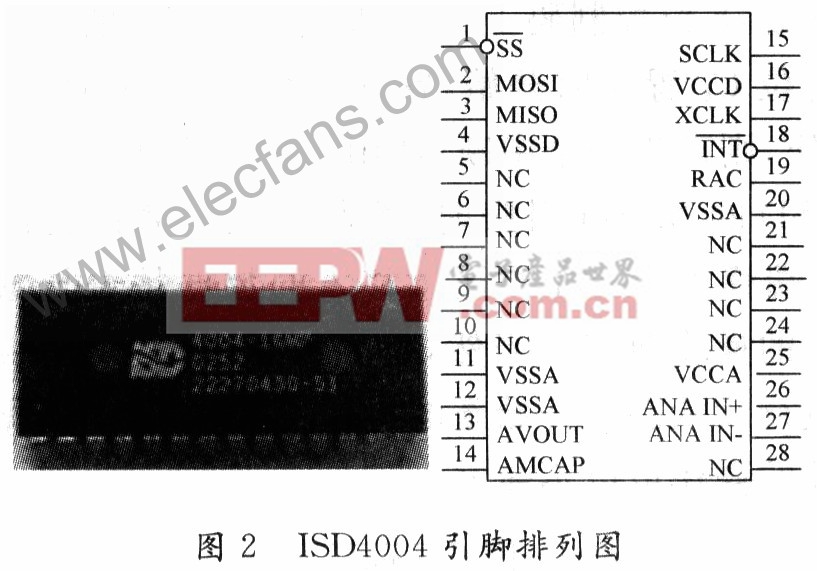

ISD4004采用28脚的SOIC封装,其引脚排列如图2所示。

1.3 ISD4004与AT89C51单片机的接口

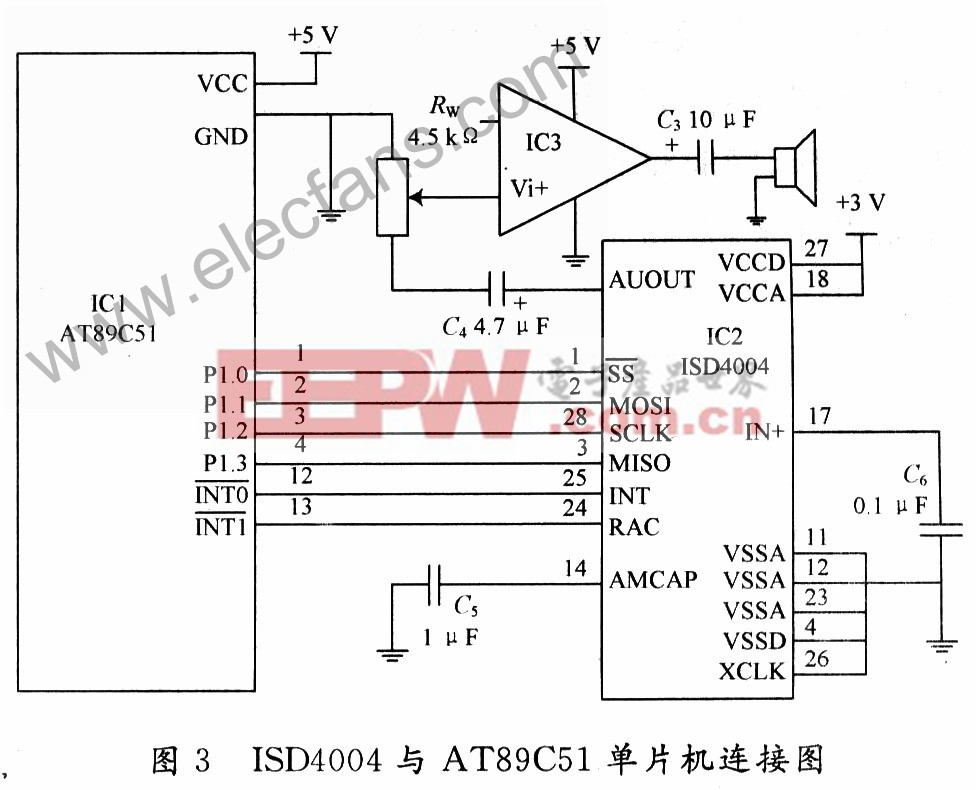

ISD4004工作于SPI串行接口,按照同步串行数据传输的SPI协议,所有串行数据传输开始于单片机主控器发送给ISD4004的片选信号SS下降沿。SS在传输期间必须保持为低电平,在两条指令之间则保持为高电平。来自串行数据输入端MOSI引脚的数据在串行同步时钟上升沿被锁存,对ISD4004串行数据输出端MISO引脚的数据在SCLK的下降沿被移出。ISD4004的任何一个录音和放音操作(含快进),都是按分段地址进行的,每段包含若干行,每行相当于存储单元,在行地址时钟信号RAC的控制下进行录放信息的存储管理。RAC信号周期为200 ms,高电平占空比为3/4。当录音和放音操作到内部存储单元地址的末尾时,会产生一个OVF或EOM结束标志信号,如果遇到EOM或OVF,则产生一个低电平有效的INT中断信号,该中断状态在下一个SPI周期开始时被清除。ISD4004与AT89C51单片机连接如图3所示。

ISD4004的片选信号SS引脚与AT89C51单片机的I/O口P1.0连接,由程序指令产生有效的低电平信号。串行数据输入MOSI引脚和串行数据输出MISO引脚分别与P1.1和P1.3连接,串行收发的数据信息在程序指令的控制下,由片内移位寄存器锁存,其同步时钟信号SCLK由单片机P1.2控制。行地址时钟RAC和中断请求信号INT分别与P3.2(INT1)和P3.3(INTO)连接。

1.4 音频输出

系统信号所对应的提示语音,如“上行列车开过来了,区间占用”、“请求上行发车,信号开放”等信息,已通过专用设备按地址分段固化到ISD4004内部E2PROM的存储单元。在程序控制下,相应的语音信号由ISD4004的13脚(AUOUT)输出,经耦合电容C4和音量控制电位器RW,送入低噪声功率放大集成电路进行放大,推动扬声器发声。为使输出语音噪声达到最小,系统的模拟地和数字地分开走线,尽可能在靠近供电端处相连,并且分别引到ISD4004芯片的VSSA和VSSD管脚上,退耦电容也应尽量靠近芯片。

1.5 I/O口的扩展

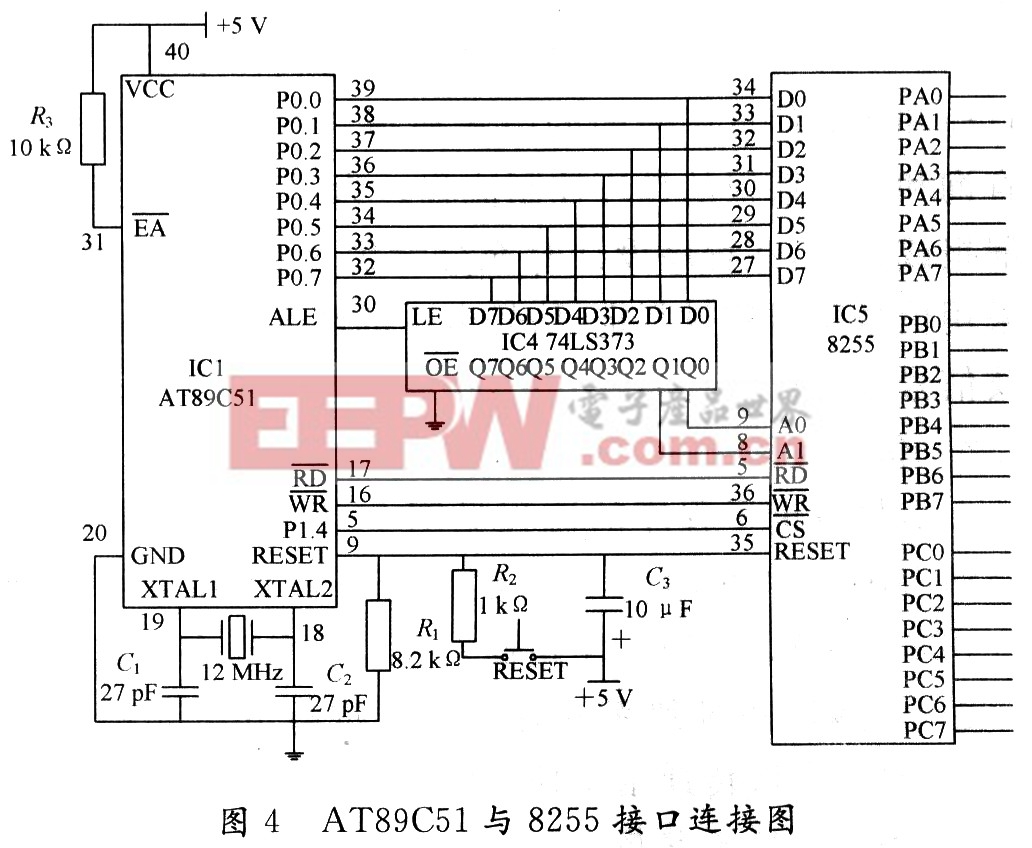

系统36路信号要经微控制器处理,至少要36个I/O口线才能满足需求,靠AT89C51剩余的I/O口显然是不够的,必须进行I/O口的扩展。系统采用可编程序并行输入输出接口芯片8255扩展不足的I/O口,具体硬件连接见图4。8255是微处理器扩展系统所用的标准外围并行接口电路,采用NMOS工艺制造,40脚双列直插式DIP封装形式。8255与外部设备交换信息通过A口、B口、c口的24条I/O线来完成的,每个口都是8位。其中C口又分为上C口(PC7~PC4高4位)和下C口(PC3~PC0低4位)。可通过编程的方法来规定端口的工作方式为输入,在主控程序初始化时完成。8255片选信号由P1.4完成,地址总线A0和A1通过地址锁存器74LS373锁定。

评论