定点DSP中高精度除法的实现方法

引 言

本文引用地址:https://www.eepw.com.cn/article/170751.htm各种集成化单片数字信号处理器(DSP)以其功能强、集成度高、应用灵活、性价比高等优点,在信号处理和系统控制中的主导性地位日益明显。许多信号处理和控制需要运用除法运算。一般的数字信号处理器中没有现成的除法指令。十多年前诞生的浮点DSP,由于其用硬件完成浮点数的运算,在数据处理和运算能力上大大超出定点DSP,处理除法运算也比定点DSP更为简单。但是定点DSP每器件产品的价格更低,这对大规模的大众市场应用而言是相当重要的优势,也是定点器件至今仍是业界主流的主要原因。所以,讨论定点DSP中除法的实现仍不失其意义。在定点DSP中虽然已经有人给出除法的算法,但是由于其运算的复杂和精度难以如愿,致使一些带有除法的好的算法在信号处理中难以得到应用。

为了提高运算结果的精度,本文在已有除法算法的基础上进行了一些改进,最大限度地保证了结果的精度。最后在TI公司的TMS320C5416芯片里具体实现并验证了这一高精度除法。

1 经典算法

DSP中没有现成的除法指令,除法是靠被除数与除数之间的移位相减来实现的。在C54X系列里利用减法指令SUBC和循环指令RPT实现2个16位数的相除。下面以C54X为例来具体实现经典的除法:

C54X提供的SuBC指令仅对无符号数进行操作,所以在移位相减开始之前必须先将被除数和除数取绝对值,仅考虑2个正数的除法。此时除法运算有两种情况:

当|被除数||除数|时,将|被除数|存放在累加器的高16位,然后用SUBC完成15次移位相减,相减之后在累加器A的低16位中存放商的绝对值。根据运算前被除数和除数的符号是否相同来决定是否要改变所得结果的符号。

当|被除数|≥|除数|时,将|被除数|存放在累加器的低16位,然后用SUBC完成16次移位相减,相减之后在累加器A的低16位中存放商的绝对值。根据运算前被除数和除数的符号是否相同来决定是否要改变所得结果的符号。

从实现的过程分析,当|被除数||除数|时,移位相减开始时|被除数|和|除数|的小数点位置正好相差一位。第一次相减后在累加器A的O位最低位存进的数值正是商的最高位,该位为商的小数点后第一位。在15次移位相减之后,累加器A低16位所得的结果为Q值为15的小数。当|被除数|≥|除数|时,在第l6次相减时,|被除数|位于A的高16位(30~15位)上,小数点位在A的15位后,和|除数|的小数点位正好对齐,则此次相减后在A的0位加上的值正好是商的最低有效整数位,相当于十进制数中的个位。所以在16次移位相减之后,累加器A低16位所得的结果为Q值为0的整数。以此分析,当商的精确值不是整数,或者超出Q值15所表示的范围时,此算法所得结果就达不到16位数据所能表达的精确度。

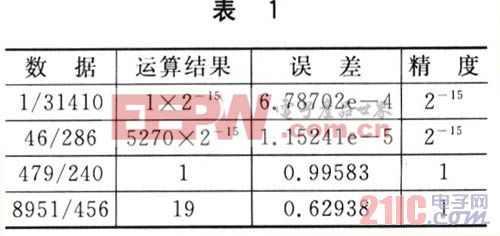

表1中任取几组数据来说明。

评论