基于DSP 的PCI 通用运动控制卡的硬件设计

2.1 PCI 总线接口

PCI 总线是一种高性能、32 位地址/数据复用总线,数据传输速率高达132MB/s。目前实现PCI 接口的有效方案有使用可编程逻辑器件和使用专用接口芯片两种。前者实现PCI接口比较灵活,但是设计难度很高。后者虽没有前者那么灵活,但其优越性非常明显:能够有效降低接口设计的难度,缩短开发时间,同时其还具有较低的成本和通用性,并能够优化数据传输,提供配置空间等。这里采用PCI9052 实现PCI 总线接口,并选用EEPROM93LC46B 对其进行配置,电路框图如图2 所示。中断信号这里只用到一条中断线INTA#。

2.2 局部总线接口

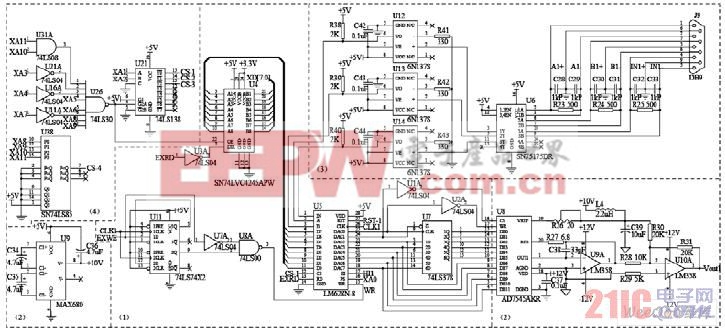

为了满足DSP 与上位机之间大量数据的高速交换,这里采用主从式共享双口RAM 的通信方案,接口电路如图3 所示。由于IDT7133 是2K×16 位的SRAM,因此将PCI9052的局部总线设置为16 位宽的数据总线,即将LBE1#单独接到IDT7133 的A0L 端。BUSYL经非门接到PCI9052 的LRDYi#端,这是因为当BUSYL 为高时才允许外部设备访问,而局部总线准备好信号LRDYi#为低电平有效。BUSYR 经电平转换后直接接到TMS320F2812 的READY 端。当BUSYL 或BUSYR 任何一个引脚被置低,其所属设备就等待一个访问周期,直到BUSY 被拉高,即双口RAM 不再忙,这样便保证了数据传输的准确性和可靠性。因此,采用双口RAM 通信不但简化了接口电路的设计,而且提高了上下位机数据交换的速度。

图 3 局部总线接口电路

2.3 LM628 伺服控制单元

控制卡共有 3 路输出,其中一路如图4 中虚线框(1)所示,其余两路与此类似。XD0~XD7为DSP 的低八位数据线,LM628 所需的32 位数据由其经总线驱动芯片SN74LVC4245 分四个写周期写入。DSP 经CS-1 选通LM628 后,再结合XA0 就可实现对其读写。为了提高控制精度,这里采用12 位输出模式,即在每一个采样周期,LM628 的18~23 脚输出两个周期,前一个输出低6 位数据,后一个输出高6 位数据。为了让12 位数据能同时输入到后续的DAC芯片中,这里采用了一片6 位数据锁存器74LS378。当LM628 输出低6 位时,DA0 是输入触发器的时钟信号,DA1 是触发器的允许信号,此时,锁存器的G 端为高,数据锁存,接着LM628 输出高6 位数据,此时DA0 是给DAC 芯片的写信号,DA1 是片选信号,锁存器的G 端为低,数据不锁存。这样便从8 位输出合成了12 位的DAC 输入信号DAC0~DAC11。

2.4 数/模转换和放大电路

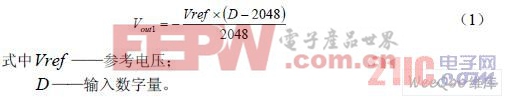

如图 4 中虚线框(2)所示,DAC 参考电压Vref 由Maxim 公司的MAX680 提供,而LM358的±12V电源则可直接从PCI 插槽获得。LM628 输出的12 位数字量经AD7545A 转换为相应的模拟量,再由LM358 两级运算放大成-10V~+10V 电压信号送往交流伺服驱动器,从而驱动电机运转。电阻R26 和R27 用来调整满刻度输出电压和抑制零点漂移,电容C38 则用来加快DAC变换速度和对其输出进行频率补偿。最终输出电压Vout1 可由式(1)计算得出:

评论