TSMC与生态环境伙伴连手推出16FinFET及三维集成电路参考流程

TSMC近日宣布,在开放创新平台(Open Innovation Platform®, OIP)架构下成功推出三套全新经过硅晶验证的参考流程,协助客户实现16FinFET系统单芯片(SoC)与三维芯片堆疊封装设计,电子设计自动化领导厂商与TSMC已透过多种芯片测试载具合作开发并完成这些参考流程的验证。

本文引用地址:http://www.eepw.com.cn/article/170022.htmTSMC全新的参考流程如下:(一)16FinFET数字参考流程提供完整的技术支持协助解决后平面式(Post-Planar)芯片设计的挑战,包括粹取(Extraction)、量化线距布局(Quantized Pitch Placement)、低VDD电压操作、电迁移、以及电源管理;(二)16FinFET客制化设计参考流程提供包括模拟、混合信号、客制化数字与内存等晶体管级客制化设计与验证;(三)三维集成电路(3D IC)参考流程能够克服以三维堆栈方式进行垂直整合时所带来的新挑战。

TSMC研究发展副总经理侯永清博士表示:「这些参考流程让设计人员能够立即采用TSMC的16FinFET工艺技术进行设计,并且为发展穿透晶体管堆栈(Through Transistor Stacking, TTS)技术的三维集成电路铺路。对于TSMC及其开放创新平台设计生态环境伙伴而言,及早并完整地提供客户先进的硅芯片与生产技术着实是一项重大的里程碑。」

16FinFET数字参考流程

16FinFET数字参考流程使用ARM CortexTM-A15多核心处理器做为验证载具,协助设计人员采用此项新技术克服与FinFET结构相关的挑战,包括复杂的三维电阻电容模型(3D RC Modeling)与量化组件宽度(Quantized Device Width)。此参考流程亦提供改善16纳米工艺功耗、效能与面积的方法,包括低电压操作分析、高电阻层绕线优化以便将电路电阻降到最低、以及针对以路径与绘图为基础的分析(Path-Based Analysis and Graphic-Based Analysis)进行比对以改善自动布局绕线(Automatic Place and Route, APR)的时序收敛(Timing Closure)。

16FinFET客制化设计参考流程

16FinFET客制化设计参考流程藉由解决在16FinFET工艺下复杂度提升的挑战来协助客户实现客制化设计,并提供符合16纳米制造及可靠性之设计法则。

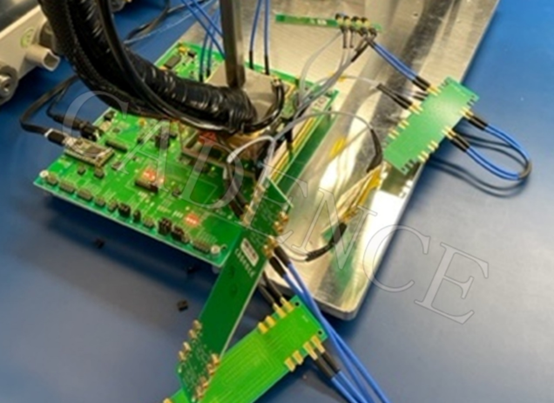

三维集成电路参考流程

三维集成电路工艺藉由整合多个芯片于同一系统上以显著提升在尺寸微缩、功耗与效能方面的优势,TSMC提供的三维集成电路参考流程能够解决以三维堆栈方式进行垂直整合时所带来的新挑战,其主要特性包括穿透晶体管堆栈技术、硅穿孔(Through Silicon Via, TSV)/微凸块及背面金属绕线(Microbump and Back-side Metal Routing)、以及硅穿孔对硅穿孔耦合粹取(TSV-to-TSV Coupling Extraction)。

pic相关文章:pic是什么

评论