基于高分辨率CMOS传感器图像采集系统的实现

随着CMOS技术的发展,原来CMOS图像传感器比CCD噪声大的特点得到大大改善,并且以其成本低、功耗低、单一工作电压、集成AD转换器、数字形式数据输出、图像大小可编程控制等优点,在摄像头、微型数码照相机、扫描仪、手机、可视电话、视频会议等众多领域应用。但要将CMOS的图像采集到DSP芯片中的硬件设计成本较高,实现难度较大。现阶段,比较多的方案是采用带视频控制器的DSP芯片,如TI6000系列中带有3个VPO接口的TMS320DM642和ADI公司带PPI接口的Blackfin处理器。很多低价通用的DSP如TI55x系列和67x系列的DSP,与CMOS图像传感器都没有直接接口,需要设计硬件电路。本文便是针对这种低价通用的DSP,提出的一种低成本的采集方案。

1 系统设计

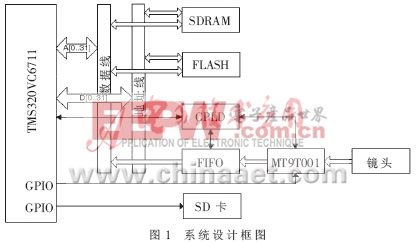

由于大部分DSP都有与SDRAM、Flash、SRAM、FIFO等存储器接口的EMIF接口,而没有直接与CMOS/CCD固体图像传感器接口的控制器。所以采用CPLD作为图像传感器到FIFO以及FIFO到DSP的一个时序协调控制器。同时由于图像传感器的像素时钟PIXCLK很高,最高可以达到48MHz,固体图像传感器的图像数据量大,而FIFO的容量有限,一般都是几K、几十K字节,对于高像素的图像来说,FIFO只能充当线缓冲的作用,要作为帧缓冲,除非系统对速度要求很高,否则成本太高。由于采集到DSP中的图像数据量很大,靠写文件的方式来验证采集的数据非常慢,所以本系统采用GPIO设计了一个SD卡的控制器,通过写BMP文件,对采集的图像进行验证。系统设计框图如图1所示。

本系统设计的关键在于DSP采用何种方式去读取FIFO中的图像数据。很多方案中都是启动EDMA读取FIFO中的图像数据,当FIFO半满时中断DSP启动EDMA读取数据,这样对FIFO读时钟的频率要求很高,需要读时钟为写时钟的2倍。但这种方案存在问题,即FIFO时钟的选择问题。EMIF口的 在EDMA启动的过程中都是一些不稳定不规则的负脉冲信号,难以选择作为FIFO的读时钟。这种采用EDMA的方案在TMS320DM642中可行,因为TMS320DM642能与FIFO无缝连接。

在EDMA启动的过程中都是一些不稳定不规则的负脉冲信号,难以选择作为FIFO的读时钟。这种采用EDMA的方案在TMS320DM642中可行,因为TMS320DM642能与FIFO无缝连接。

2 硬件设计

2.1 硬件电路图

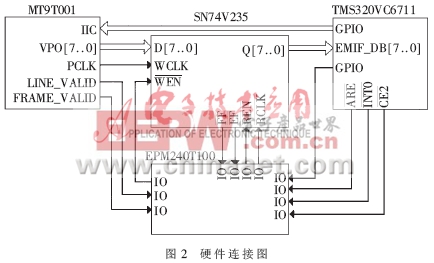

本系统硬件连接如图2所示,所采用的图像传感器型号是MT9T001,它是一款主要针对数码相机领域的CMOS图像传感器。与其他的CMOS图像传感器相比,MT9T001有以下明显的特点:

(1)像素大小可以通过IIC接口改变相应寄存器进行硬件裁剪。

(2)高的帧速,输出为QXGA分辨率(2 048×1 536)时,可以达到12f/s,而输出为VGA分辨率(320×240)时,有93f/s。

(3)高性能的低照度成像性能。

(4)具有AF对焦窗口的图像输出格式,如图3所示,(2 048×512)时,可以达到30f/s。

评论