AD9847的原理及其在CCD 成像系统中的应用

(9)片上时序发生器,可在外部同步信号的作用下给CCD芯片提供所需的时序信号(H1,H2,RG),配合另外提供的V、VSUB信号,可以驱动CCD工作;

(10)48脚LQFP封装,大大节省电路板空间。

AD9847在基准信号VD、HD、CLI 作用下,通过FPGA对三线串口进行编程,为系统设置适当的寄存器配置。AD9847各个功能的实现建立在内部寄存器正确配置的基础上。三线串口为SLOAD、SCLOCK、SDATA,共有两种配置方式:一种是串行写操作,连续写入8位地址信号和6位数据信号,SLOAD信号在写入数据期间一直处于低电平状态,在此期间SCLOCK信号表现为时钟信号,其他时间维持高电平,SDATA的数据在SCLOCK的时钟上升沿被锁存;另一种是连续的串行写操作,只有一个8 bit地址位作为首地址,后面依次为以6 bit为一组的数据位,每6 bit对应一个地址,地址以首地址为基准依次递增,最终将数据写进对应的寄存器,SLOAD在此期间一直为低,直到最后一个寄存器被装载。AD9847的配置主要是完成对CDS采样信号的置位、驱动信号波形、可变增益放大器的增益、钳位电平以及其他功能等的设置。AD9847基本工作流程为CCD模拟视频信号经过射随器之后送给AD9847,在AD9847内部首先经CDS进行相关双采样,消除噪声干扰,然后通过增益放大再送至ADC进行A/D转换,最终将转换后的数字信号送至下一步电路进行处理。DOUTPHASE寄存器可以设置输出数字信号的最佳位置。

3.1 寄存器配置

该系统中AD9847与FPGA作为核心,FPGA作为AD9847的上位机控制AD9847 的工作。AD9847作为AFE又有着无法替代的优势,它将很多视频信号处理电路集成起来替代了很多复杂的分电路。系统中AD9847和FPGA由同步时钟控制,上电初始化后FPGA经三线串口配置AD9847。AD9847共有164个寄存器,有些寄存器为双宽度寄存器,占有两个地址,对于这样的寄存器必须两个地址都写入数据才能使其作用。对于寄存器中有些数据位宽不足6 bit的,在配置时需补足6 bit。大部分寄存器地址是连续的,仅有一些不连续。根据参考文献[3]中要求的AD9847寄存器配置的顺序,有些地址偏后的寄存器可能需要先配置,这样就导致有些寄存器只能采用串行写操作模式,对于地址连续的寄存器可采用连续的串行写操作模式。故在对AD9847寄存器配置过程中,将串行写操作模式和连续串行写操作模式结合起来,只需注意每个bit数据与SCLOCK对应位置即可。

3.2 驱动电路

系统工作首先需要驱动CCD,为减轻FPGA的负担,AD9847承担产生一部分驱动信号的任务。HBLK、H1-H4、RG等相关寄存器可产生所需要的驱动信号。对垂直时钟H1行空白期间电平极性应当设置为低,因为后续的电压转换电路中对其进行了反相,参考文献[2]中H1信号波形图。由FPGA产生的水平转移驱动信号配合AD9847产生的驱动信号经由电压转换电路驱动CCD工作。CCD在驱动信号作用下,输出模拟视频信号如图2。图中,1通道为CCD视频信号,4通道为H1信号。

3.3 相关双采样

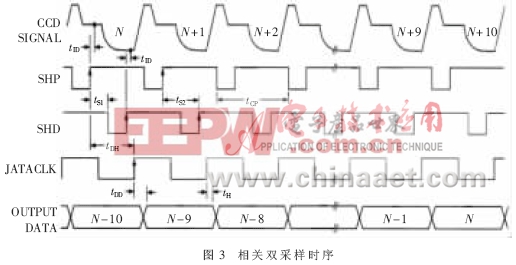

视频信号在AD9847内部首先经内部相关双采样电路对每个CCD像素信号进行两次采样,以提取视频信息和抑制低频噪声。由于CCD每个像素的输出信号中既包含有光敏信号,也包含有复位脉冲电压信号,若在光电信号的积分开始时和积分结束时,分别对输出信号采样,并且使得两次采样的间隔时间远小于时间常数RonC(Ron为复位管的导通电阻),则这样两次采样的噪声电压相差无几,而这两次采样的时间又是相关的[4]。若将两次采样值相减,就基本消除了复位噪声的干扰,得到信号电平的实际有效幅值。通过设置SHPPOSLOC和SHDPOSLOC寄存器来决定SHP和SHD的采样位置,SHP采样参考电平,SHD采样有效电平,采样位置的设定是得到好的CCD信号的关键。因AD9847的SHP、SHD均在内部产生,外部并没有输出管脚,故无法用示波器显示采样信号。相关双采样时序如图3所示。

3.4 箝位及增益放大电路

评论