AD9847的原理及其在CCD 成像系统中的应用

经CDS处理的CCD信号送至下一个电路。箝位电路用来消除信号链中的残留偏压,并且跟踪CCD暗像素的频率成份,错误的信号将被过滤掉,所以噪声降低,去掉偏压还可减小对增益改变的影响。AD9847内部箝位信号为CLPDM、CLPOB,箝位位置通过配置寄存器来改变。具体的寄存器配置内容需根据AD9847 datasheet和CCD的datasheet的要求进行配置,只需根据CCD行转移信号找出black pixel、effective pixel的位置即可。

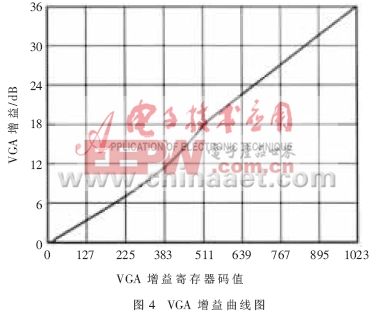

AD9847的增益放大器有PxGA(像素增益放大器)和VGA(可变增益放大器),两个增益放大器共同工作,对弱信号放大、强信号缩小,使图像灰度处于比较理想的状态。其中,PxGA为单个的彩色像素提供单独的增益调整。一个可编程增益放大器有4个单独值,PxGA可将增益值分配给单个像素。PxGA可以用于白平衡调整彩色信号,可减少后续的数字处理工作量,并很方便地为CCD摄像机系统提供了白平衡功能。配置ctlmode寄存器可以选择PxGA的工作模式,ctlmode可针对不同类型的CCD彩色滤波阵列设置7种不同的彩色引导模式,彩色引导起着正确分开R、G、B分量的增益值的作用,并由垂直(VD)和水平(HD)同步信号控制同步。四个通道的PxGA增益范围为-2 dB~+10 dB,对应64 steps,通过串行口配置pxga gain寄存器来控制,其缺省值对应为4 dB。VGA的增益范围2 dB~36 dB,通过寄存器VGA gain,以10-bit分辨率即1 024 steps进行配置。结合PxGA的4 dB增益,AD9847总的增益范围为6 dB~40 dB。当ADC的输入信号最大范围值为2 V时,最小增益6 dB须对应1 V输入信号。当对应1 V最大范围系统时,增益相当的范围为0 dB~34 dB。VGA增益曲线分为两个区域,当VGA增益寄存器码对应范围0~511时,曲线对应(1+x)/(1-x)的形状;512~1 023时,曲线对应linear-in-dB的形状,如图4。VGA实际的增益值相应寄存器中的增益值的计算公式如下:

码值为0~511时:

Gain=20log10([658+code]/[658-code])-0.4

码值为512~1 023时:

Gain=(0.0354)(code)-0.04

经过以上信号预处理后,信号进入A/D转换器,AD9847使用一个高性能的10-bit ADC结构,高速低耗。差分非线性性能优于0.4LSB。ADC输入范围为2 V,大的全量程ADC范围带来很好的性能。系统中AD转换后的数字信号送入FPGA进一步处理。

4 AD9847的外部电路设计

在PCB板的设计过程中,数模混合电路的设计一直是一个瓶颈。模拟信号向数字信号的转变是否实时、精确,是电路设计的重要指标。通常的电路中,模拟信号上由于存在随时间变化的连续变化的电压和电流有效成分,在设计和调试过程中,需要同时控制这两个变量,而且它们对于外部的干扰更敏感,因而通常作为被干扰对象来分析;数字信号上只有随时间变化的门限量化后的电压成分,相比模拟信号对干扰有较高的承受能力,但是这类信号变化快,特别是变化沿速度快,还有较高的高频谐波成分,对外释放能量,通常作为干扰源[5]。

AD9847即有模拟电路又含数字电路部分,它的电路设计一定要谨慎。本系统采用单点接地方式,将AD9847的数字地与模拟地分开布线,单点用铜皮或 FB 磁珠连接。系统使用单独的地层,地层尽量连续,退耦电容要尽量靠近芯片放置,尤其是管脚25~35,以减少退耦电容在电源和旁路引脚以及其接地引脚之间产生的电阻回路。串联电阻离数字输出管脚越近,数字码字转换噪声越小。如果数字输出要驱动一个大于20 pF的负载,建议用缓存来降低数字编码传输噪声,还可以放置一系列的电阻降低该噪声。为得到低噪声性能,电源退耦非常重要。经设计,AD9847最终外围电路连接图如图5所示。

评论