利用SoC平台设计并验证MPEG-4/JPEG编解码IP

如图1所示,对一般的设计而言,IP、嵌入式处理器、内存和逻辑闸使用数目的增加所造成的复杂度上升,将导致设计与验证人力也随之上升。因此,设计的复用性变成了一种可推进设计生产力的有效途径。

尽管基于IP可复用的设计方法已经推广了将近十年,但大多数的设计方式仍然大量地采用基于模块的堆积,并且需要用户去进行整合。使用预先设计好的模块时,工程师必须了解模块如何工作,以及在设计中如何与其它模块整合并且工作正常。第三方IP增加了整合的难度,即便是那些在商业上取得成功的,并且经过流片验证的IP,在使用时也经常出现问题。

使用预先设计好的模块不能保证一次流片就能成功。在过去的几年中,几家公司尝试改变设计方法,藉由标准化的内部IP或虚拟组件(virtual components)以及软件完全整合在共同的架构中,这样的产品可建立起共同的功能而

在SoC的技术挑战之外,还有一些问题很少被提到,但它们却对基于平台的SoC设计至为重要。其中之一的挑战就是SoC设计团队对于众多子群――例如IP提供商、软件工具提供商、EDA工具提供商、验证团队、系统设计团队和代工厂之间的整合。不幸的是,大部分的平台SoC提供者一般只对上述所提的一两项比较熟悉。缺乏沟通将会严重地限制SoC设计步骤顺利执行。理想的SoC设计团队和子群间应该是相互紧密联系的,这样设计中出现的问题才能快速地被解决。

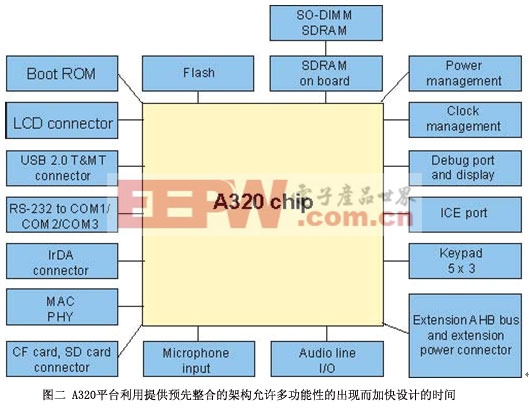

智原科技是一家老字号的设计服务公司,聚结上述众多子群于公司内。积累大量的虚拟组件, 包括ARM V4指令兼容的32位嵌入式处理器和高速I/O。如图二提供A320平台利用提供预先整合的架构允许多功能性的实现而加快设计的时间。我们又如何利用这个SoC平台设计自己的MPEG4编解码器IP在上头?

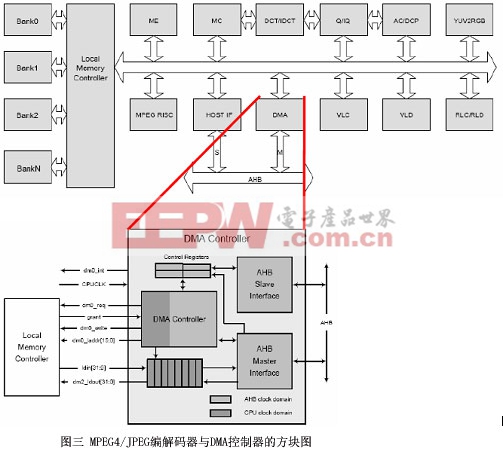

智原科技设计的这个MPEG-4/JPEG编解码器IP,首先要符合AHB的时序,目的是用以加速多媒体视频。包含运动评估(Motion Estimation)、离散余弦变换/反离散余弦变换(DCT/IDCT)、量化运算(Quantization)/反转量化运算(Inverse Quantization)和运动评估等全硬件的加速器。

智原科技的ARM CPU-FA526为32位嵌入式CPU,是智原科技自行研制开发且合法的产品。该CPU采用哈佛结构,拥有六级流水线(pipeline),与ARM V4的结构兼容。FA526使用16K/16K bytes I-cache/D-cache和8K/8K bytes instruction / data scratchpads,采用JATG ICE接口使得编程调试极为方便,高性能低功耗让该款CPU的使用领域变得十分广泛。

FA526利用AHB从接口控制编解码器。初始化编解码器的控制寄存器,运动估计对整个16x16或8x8的块(block)计算的任务(task)能由编解码器自行完成。离散余弦变换/量化,反离散余弦变换/反转化,AC/DC 预测,锯齿状扫描(Zigzag Scan)和可变长编解码器(VLC/VLD)计算的任务也能由编解码器自行完成。

还要再设计一个内部的DMA控制器执行在系统内存与MPEG4/JPEG编解码器本地内存的数据搬移的任务。DMA控制器包含一个AHB主接口和一个AHB从接口,AHB主接口使DMA控制器由AHB总线访问数据,AHB从接口由AHB总线用以编程DMA控制器的控制寄存器。我们接着确定MPEG4/JPEG编解码器IP的规格如下:

全硬件的MPEG4/JPEG编解码器.

符合MPEG-4 (ISO/IEC 14496-2) simple profile L0 ~ L3标准

-支持标准分辨率(sub QCIF, QCIF, CIF, VGA and 4CIF )和non-standard on 16-pixel steps

-最大支持D1 @ 30 fps, XGA @ 15fps, SXGA @ 10fps

-全双工工作时,帧率为半双工时的一半

-支持MPEG4 short header format (H.263 baseline)

-运动估计的搜索范围:-16 ~ +15.5 (optional to C32 ~ +31.5) 在半个pixel精度的情况下

-支持4MV

-支持不变速率 (Constant Bit Rate) 和可变速率(Variable Bit Rate)控制

-支持下面的两种错误恢复工具

-编码:重新同步标志(re-synchronization marker)和头扩展码(header extension code)

-解码:重新同步标志(re-synchronization marker),头扩展码(header extension code),数据分割(data partition)和RVLC

符合JPEG (ISO/IEC 10918-1) baseline 标准

-4个用户自定义的Huffman tables (2AC和2DC)

-4个可编程的量化表

-隔行和逐行扫描

-YCbCr 4:4:4, 4:2:2 和4:2:

-图片尺寸最大到64kx64k

-60fps 在640x480的分辨率

MPEG4 影像压缩是将取得的影像经过动态估计,取得其移动向(Motion Vector)以及绝对差值和(SAD),当绝对差值和太大时,将原的影像送入离散余弦变换(Discrete Cosine Transform),反之,则将现在的影像与前一张还原的影像做差值运算,将差值送入离散余弦变换。之后再将离散余弦变换完成的资作化运算,并将化后的资作AC/DC预测器(AC/DC prediction),之后再将直交预测完毕的资传入可变长编码器(Variable Length Code),将原始的影像资压缩成基本比特流(Base Layer Bitstream)的方式传出,客户端在接收到基本比特流之后,可以在经过解码器的解压缩将视频还原,另外一方面,化运算完毕的资除传入AC/DC预测器,也将同时传入反转化器(Inverse Quantization),再将反转化后的资传入反离散余弦转换,再依据之前动态预估时计算的结果做动态补偿(Motion Compensation),以重建出一张影像作为下一张影像的参考影像。确认规格后,将编解码器的模块架构定义好,如下图三所示。我们对其中一些模块做说明。

运动估计(Motion Estimation, ME):运动估计单元能基于快速搜索算法(fast search algorithm)对整个搜索窗口(Search Window)进行运动估。简单就是去估算当前的帧(Frame)某一个N×N 区块(Macro block)和早先的帧(Reference block)最相似的区块位移的向,称之为移动向。这个区块所要搜寻的范围在这区块四周往外扩展固定值w,称为搜索区(Search Area)。

DCT/IDCT:MPEG4算法的核心是一种称为离散余弦变换(DCT)的操作。DCT的基本原理是取像素块的平方并除去观察者察觉不到的冗余信息。为了解压缩数据,还需要反离散余弦(IDCT)运算。DCT/IDCT单元就是负担离散余弦变换和反离散余弦的运算。IDCT与DCT共享相同的硬件资源,产生的结果兼容IEEE 1180-1990规格,在解码的状态送到运动估计单元。DCT产生的结果在编码的状态送到量化单元。

量化(Quantization, Q)/ 反转化(Inverse Quantization, IQ):化主要用配合DCT 的结果减少资的大小,以增加之后VLC 的压缩比。反转化加上DCT将编码后的影像资进译码动作,用结合运动估计时计算的结果做动态补偿,以重建出一张影像作为下一张影像的参考影像。量化/反转化单元支持H.263/MPEG/JPEG量化方法。量化产生的结果在编码的状态送到AC/DCP单元。IQ产生的结果在解码的状态送到IDCT单元。

AC/DCP(AC/DC Prediction):AC/DC 预测目的是参考块(Block)周围其它区块(Macro Block) 的量化值,对其参考块作预测,减少资的大小,以增加VLC 的压缩比。AC/DC预测单元支持MPEG-4AC/DC预测和JPEG DC预测方法。AC/DC预测单元产生的结果在编码的状态送到Zigzag Scan单元。反AC/DC预测单元产生的结果在解码的状态送到反转化单元。

评论