基于SoC的音频IP模块设计

随着集成电路设计技术和深亚微米制造技术的发展,集成电路已进入了片上系统时代。由于SoC结构极其复杂,对于设计者而言,数百万门规模的系统级芯片设计不可能一切从头开始,随着集成电路设计技术的发展,IP核的开发己成为不可忽视的发展趋势,它的出现为SoC的实现和发展提供了基础。IP称之为知识产权,它可以认为是封装在硬件设计中的可重复利用的软件,就功能而言,IP核可以定义为SoC的基本电路功能块又称为内核,可由用户或专用IC公司或独立的公司开发而成,IP核的显著特点是具有重用性。鉴于SoC系统设计者很难独自开发、维护和移植所有必须的IP核,所以在Soc设计中必然要用到第3方的IP核,当IP核被转移到用户设计与制造工艺中时,IP核被重复利用了,具有自主知识产权的IP核的复用是Soc设计中解决设计层次、产品成本、设计周期和降低风险的关键环节是SoC设计中的关键技术。IP核重复利用可以提高设计能力,节省设计人员可以缩短上市时间,更好的利用现有的工艺技术,降低成本。基于此笔者设计了基于SoC的音频接口IP模块。

1 APB与IIS总线

APB(Advanced Peripheral Bus)是AMBA(Advanced Microcontrollel Bus Architectrure)组成部分,是用于低功耗和减少接口复杂度而设计的。APB用于带宽,低速,低性能要求,无管线操作的外围设备。APB总线操作包括Setup和Enable两个状态。其中APB读操作只需在Enable状态数据有效,写操作要求写数据在整个写操作期间保持有效。

APB协议规定每个传输只与时钟上升沿相关。这就使APB外围设备很容易被集成在设计之中,特点如下:

(1)在高频操作的性能改进;

(2)独立的脉冲时钟;

(3)静态时钟分析比较简单,因为用单时钟沿触发;

(4)自测试逻辑插入没有特别的条件需要考虑;

(5)在ASIC库中有性能很好的上升沿寄存器;

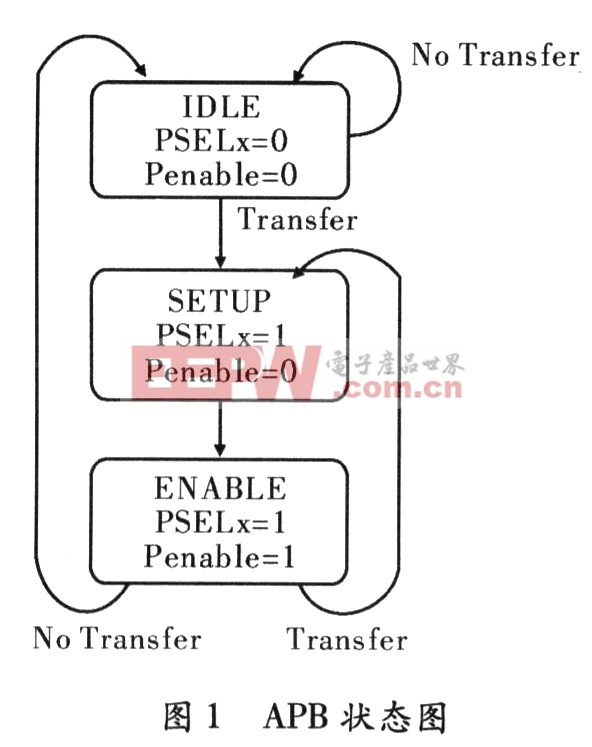

APB状态机,如图1所示。

APB这3个状态描述如下:

IDLE:默认初始状态。

Setup:当有一个传输请求,总线将进入Setup状态,当PSELx,信号被选择。总线只在Setup状态停留一个周期,并将在时钟的上升沿进入Enable状态。

评论