基于VHDL的XRD44L60驱动时序设计

1 引言

本文引用地址:https://www.eepw.com.cn/article/163811.htm电荷耦合器件(Charge Coupled Devices,简称CCD)是一种光电转换式图像传感器。它利用光电转换原理将图像信息直接转换成电信号,实现非电量测量。由于CCD的输出信号是负极性的离散模拟信号,并且混杂有幅度较大的复位脉冲干扰,为了获得高质量信号,必须对CCD输出信号进行直流箝位、相关双采样、低通滤波和放大等预处理,以消除各种干扰和噪声。同时,为了便于计算机处理和大容量存储,还必须对CCD输出信号进行数字化处理。目前市场上CCD专用的视频信号处理器件不仅具有双采样技术,而且还具有自动暗电平补偿、自动增益和A/D转换等功能。这里给出了一款CCD专用的视频信号处理器件XRD44L60,并介绍了基于VHDL 的XRD44L60CPLD逻辑控制电路。

2 XRD44L60简介

XRD44L60是Exar公司CCD专用的视频信号处理器件。该器件是针对CCD影像应用产品而设计的。XRD44L60采用相关双采样 (Correlated Double Sampling,简称CDS)技术提取图像信息,可编程增益(Programmable Gain Amplifier,简称PGA)控制范围可达6 dB+38 dB,具有良好的输人信号箝位和CDS输入偏移校正性能,并提供暗电平箝位,给出准确的暗电平参考。XRD44L60还有一个10位A/D转换器,转换速率高达16 MHz,便于CCD阵列信号的数字处理。此外,XRD4-4L60的串行接口包括一个10位的移位寄存器和多个并行寄存器,可用于编程设置其工作参数。 XRD44L60的电源电压为3.0 V,功率为120 mW,适用于小型化嵌入式CCD数字相机系统。

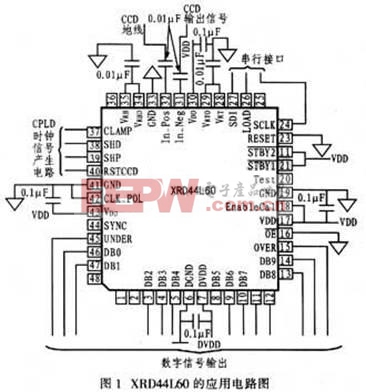

3系统电路设计

XRD44L60硬件电路设计如图1所示。其中,In_Pos和In_Neg为模拟信号输入端口,用于连接CCD的输出信号。CLAMP,SHD,SHP 及RSTCCD为时钟信号控制引脚,用于连接CPLD信号的输出端,以控制器件工作。LOAD,SDI,SCLK为串行接口可编程设置XRD44L60的工作参数。DB0~DB9为10位数字信号输出,可与信号处理单元连接。

4 XRD44L60的时序控制

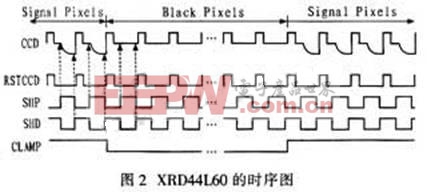

采用可编程逻辑器件(CPLD)技术和VHDL语言实现对CCD视频信号处理器件XRD44L60的控制,使其完成CCD视频信号的放大、噪声处理及数字化,并输出对应的数字信号。XRD44L60的工作时序需要根据具体的CCD器件来确定。下面以TCD1501D型CCD为例,介绍XRD44L60的工作时序。TCD1501D的工作频率为1 MHz,CCD输出信号周期为2μs,其外部时钟输入由有源晶体振荡器提供,频率为8 MHz。当CLK_POL为低电平时,XRD44L60的时序如图2所示。驱动脉冲包括CCD复位脉冲RSTCCD、相关双采样暗电平时钟SHP、相关双采样信号电平时钟SHD、相关双采样箝位控制脉冲CLAMP。

4.1 RSTCCD脉冲的产生

由图2可知,RSTCCD的周期为2μs,占空比为1:7。因此,可对输入时钟脉冲16分频,其高电平占2个周期的时钟脉冲;低电平占14个周期的时钟脉冲。当计数器计数到15时,计数器清零,重新计数,相关程序源代码如下:

4.2 SHD和SHP脉冲的产生

由图2判断出,SHD和SHP的周期均为2μs,占空比为1:1。因此,可采用上述方法获得这两个脉冲。

4.3 CLAMP脉冲的产生

CLAMP脉冲由CCD的输出决定,即当CCD的输出信号为像元信号时,CLAMP为高电平;当CCD的输出信号为暗像元信号时,CLAMP为低电平。

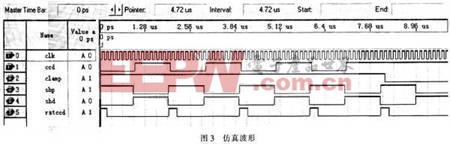

5驱动脉冲仿真波形

该没计采用QuartusⅡ仿真软件进行仿真。仿真波形如图3所示。其中,CLK和CCD为输入信号;CLAMP,SHD,SHP及RSTCCD为XRD44L60的驱动信号。

6 结语

基于VHDL的XRD44L60逻辑控制电路能够产生满足系统要求的驱动脉冲,整个系统设计能够达到预期效果。将VHDL应用于XRD44L60时序电路设计,系统设计更简单、灵活、可靠,因此可广泛用于使用CCD的影像产品中。

评论