基本触发器的逻辑结构和工作原理分析介绍

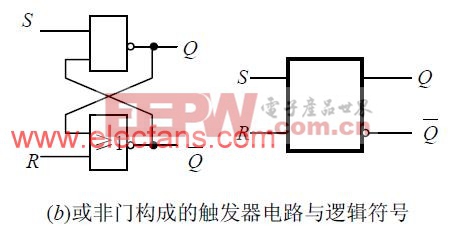

基本触发器的逻辑结构如图13-1所示。它可由两个与非门交叉耦合构成,图13-1(a)是其逻辑电路图和逻辑符号,也可以由两个或非门交叉耦合构成,如图13-1(b)所示。

本文引用地址:https://www.eepw.com.cn/article/160942.htm

现在以两个与非门组成的基本触发器为例分析其工作原理。

在图13-1(a)中,A和B是两个与非门,它可以是TTL门,也可以是CMOS门。Q和 是触发器的两个输出端。当Q=0,

是触发器的两个输出端。当Q=0, =1时,称触发器状态为0,当Q=1,

=1时,称触发器状态为0,当Q=1, =Q时,称触发器状态为1。触发器有两个输入端SR、,字母上的非号表示低电平或负脉冲有效(在逻辑符号中用小圆圈表示)。根据与非逻辑关系可写出触发器输出端的逻辑表达式:

=Q时,称触发器状态为1。触发器有两个输入端SR、,字母上的非号表示低电平或负脉冲有效(在逻辑符号中用小圆圈表示)。根据与非逻辑关系可写出触发器输出端的逻辑表达式:

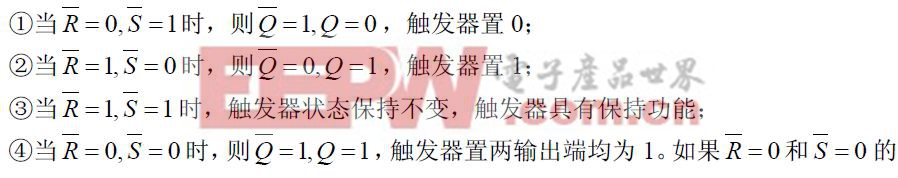

根据以上两式,可得如下结论:

持续时间相同,并且同时发生由0变到1,则两个与非门输出都要由1向0转换,这就出现了所谓的竞争现象。假若与非门A的延迟时间小于B门的延迟时间,则触发器将最终稳定在Q=0, =1的状态。因此,在

=1的状态。因此,在 而且又都同时变为1时,电路的竞争使得最终稳定状态不能确定。这种状态应尽可能避免。但假若

而且又都同时变为1时,电路的竞争使得最终稳定状态不能确定。这种状态应尽可能避免。但假若 后,

后, 和

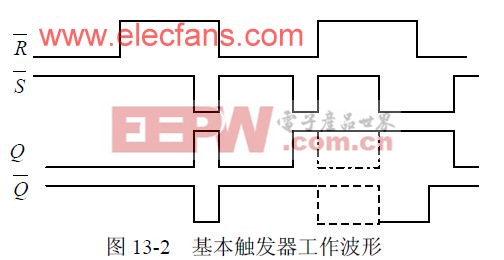

和 不是同时恢复为1,那么最后稳定状态的新状态仍按上述①或②的情况确定,即触发器或被置0或被置1。图13-2所示为基本触发器的工作波形。图中虚线部分表示不确定。

不是同时恢复为1,那么最后稳定状态的新状态仍按上述①或②的情况确定,即触发器或被置0或被置1。图13-2所示为基本触发器的工作波形。图中虚线部分表示不确定。

由上述分析可见,两个与非门交叉耦合构成的基本触发器具有置0、置1及保持功能。通常称 为置1端,因为

为置1端,因为 =0时被置1,所以是低电平有效。

=0时被置1,所以是低电平有效。 为置0端,因为

为置0端,因为 =0时置0,所以也是低电平有效。基本触发器又称置0置1触发器,或称为RS触发器。

=0时置0,所以也是低电平有效。基本触发器又称置0置1触发器,或称为RS触发器。

需要强调的是,当 =0,

=0, =1,触发器置1后,如果

=1,触发器置1后,如果 由0恢复至1,即

由0恢复至1,即 =1,

=1, =1,触发器保持在1状态,即Q=1。同理,当

=1,触发器保持在1状态,即Q=1。同理,当 =1,

=1, =0时,触发器置0后,

=0时,触发器置0后, 由0恢复至1,即

由0恢复至1,即 =1,

=1, =1时,触发器保持在0状态,即Q=0。这一保持功能和前面介绍的组合电路是完全不同的,因为在组合电路中,如果输入信号确定后,将只有唯一的一种输出。

=1时,触发器保持在0状态,即Q=0。这一保持功能和前面介绍的组合电路是完全不同的,因为在组合电路中,如果输入信号确定后,将只有唯一的一种输出。

评论