数字差分BPSK扩频接收机的设计与FPGA实现

关键字:FPGA,扩频,同步

1引言

随着软件无线电技术的发展,传统的基于复杂模拟硬件的接收设备逐渐向数字IC产品过渡,而FPGA作为ASIC产品原型设计的可编程逻辑器件,以其丰富的逻辑资源和可重新配置的优势,成为人们前期研究与开发的重要手段。因此,在可编程逻辑器件上实现数字扩频接收机关键技术进行研究,具有重要的应用价值。

本文给出了一种数字差分BPSK直接序列扩频接收机的方案,并通过simulink进行了仿真,同时本文深入探讨了方案中的关键技术在FPGA中的实现结构,在保证系统稳定性,和不影响系统性能的前提下降低硬件复杂度的问题上提出了FPGA实现方案,并最终在Xilinx XC2V500 FPGA上实现了整个系统,对工程实践有一定的指导意义。

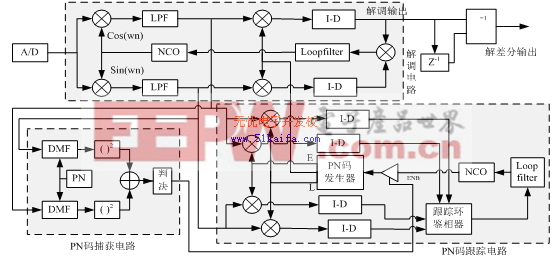

数字BPSK扩频接收机原理图见图1,系统主要可以分为三个部分:解调电路、PN码捕获电路和PN码跟踪电路。

图1 数字差分BPSK扩频接收机原理图

*本文工作得到国家自然科学基金资助(批准号:60171037) |

通过Simulink仿真该系统,同时结合Xilinx公司FPGA特点,对硬件电路实现进行探讨,在保证系统性能的前提下,减小硬件实现复杂度。 下面将具体介绍电路各部分原理与硬件实现。

2.1 数字解调

BPSK信号的解调通常采用相干解调的方式,已经证明跟踪低信噪比的抑制载波信号的最佳装置是Costas环及平方环[1],并且这两种结构是等效的,在数字域中通常采用Costas环实现载波同步。

Costas环电路结构见图1解调电路,电路各部分实现如下。

(1)数控振荡器(NCO)

数控振荡器采用查找表结构,即预先将正弦信号样本存储在ROM中,通过相位进行累加,将结果作为ROM地址信号进行查表,得到的输出即为正弦信号,此处的ROM可由FPGA中的块RAM实现。

(2)解扩单元

直扩通信中,需要先解扩才能使Costas环正常工作,下变频后的数据先利用已经同步的PN码进行解扩处理。解扩过程并不需要乘法器,可以利用异或逻辑完成。本系统实现中将PN码事先存入FPGA的基本单元-查找表(LUT)中,令LUT实现移位寄存器功能,利用跟踪单元生成的同步PN码时钟进行移位,移位输出的PN码与输入信号进行异或,完成解扩。

(3)积分清零器(I-D)

积分清零器对一个PN码周期的数据进行累加,输出与信息码元相同速率的比特流,完成相关运算,同时起到低通滤波的作用。

(4)环路低通滤波器

乘法鉴相器的输出经过环路滤波器后,去修正数字控制振荡器的频率控制字,完成闭环控制。Costas环采用二阶环路,对应一阶环路滤波器,滤波器的传输方程为[2]:

其中系数C1,C2可以由理论推导得出,实际应用中也经常采用经验比值 ,具体数值根据实际仿真结果选择。

,具体数值根据实际仿真结果选择。

2.2 PN码捕获

PN码捕获在载波恢复之前。PN码同步分为捕获和跟踪两个阶段:捕获完成粗同步,使PN码同步误差在一个码元之内;跟踪完成精确同步,使本地PN码与输入序列PN码精确对准。PN码捕获存在多种算法,匹配滤波法具有捕获时间短的特点,因此本文采用这种方法。

匹配滤波器的原理比较简单(电路见图1 PN码捕获电路),捕获过程利用本地PN码对I、Q两路同时进行相关处理,然后能量求和后检测峰值。通常为了降低虚警同步的概率,可以设计同步状态机,当峰值超过某阈值时,认为PN码达到预同步,经过一个PN码周期,再检测阈值,这样经过多次检测,每次都超过阈值时认为捕获成功,这样设计可以大大减小PN码捕获的虚警概率。

传统的并行数字匹配滤波器在实现上存在资源占用率大的缺点,本设计中针对FPGA内部特点,采用折叠型匹配滤波器[3]。折叠型滤波器允许使用者更加灵活的从占用芯片资源与芯片处理速度之间做出折衷的选择,给实际应用带来了很大的方便。

具体地,系统中的PN码长为15位,4倍过采样率,对应折叠型匹配滤波器结构如下图。

图2 折叠型匹配滤波器原理图

如图2所示,PN码折叠存放,因为PN码长15位,所以图中的第16位码并不参加运算。每输入一个数据,滤波器以4倍输入数据的时钟频率进行处理。在第一个时钟周期,Code 0,Code 1,Code 2,Code 3与输入数据作相关,并与前一级的SRL输出相加,此时最左端加法器加0,最后一级SRL的值移至保持寄存器;第二、三个周期操作相同,分别选用接下来的两组PN码做相关,最左端的加法器输入为保持寄存器的数值,最后一级仍移位至保持寄存器;第四个周期前面操作与第二、三周期相同,最后一级的相关值并不参加运算,而是上一级SRL的输出直接移入本级的SRL,同时本级的SRL输出至相关输出寄存器。

其中SRL和存放PN码的移位寄存器可以用LUT实现,这样就大大节省了FPGA中相对紧俏的寄存器资源,同时折叠滤波器的处理时钟需要是输入数据速率的4倍。数据位宽是影响资源占用的一个重要因素,设计中为了兼顾硬件资源和系统精度,截断数据位宽为8bit。

2.3 PN码跟踪

当捕获信号的检测统计量大于预先设定的门限时,跟踪电路就被开启。跟踪的基本方法是利用锁相环路来调整本地时钟的相位,常用的跟踪环路有延迟锁相环(Delay locked Loop,DLL)及 抖动锁相环(Tau dither Loop,TDL)。本系统采用延迟锁相环法。

延迟锁相环是一种非相干跟踪环路,如图1 PN码跟踪电路所示,相关原理请查阅参考文献[4]。

在PN码捕获之后,得到了粗同步后的PN码,然后进入跟踪环。其中PN码发生器产生超前和滞后1/2PN码码元周期的两个码组E和L,分别与I、Q两路进行相关,之后得到四路相关值记为 此部分电路结构与Costas环中解扩和积分清零相同,不再赘述。

此部分电路结构与Costas环中解扩和积分清零相同,不再赘述。

(1)跟踪环鉴相器

跟踪鉴相器存在多种算法[1],本文采用超前减去滞后能量的运算,即

鉴别器输出=

在 个码片的输入误差范围内,它跟超前减去滞后包络的运算有相同的DLL鉴别器误差性能,却降低了硬件实现的复杂度。

(2)NCO

码跟踪环的NCO结构比较简单,容易设计,通常采用累加器跟一个固定频率控制字和来自环路滤波器的误差控制信号共同构成。其中固定的频率控制字根据累加器时钟和PN码钟以及累加器所用的位数计算得出,累加器不断的进行累加,这样累加寄存器的最高位不断的产生“0”“1”变化,从而形成一定周期的脉冲,用此脉冲作为PN码移位寄存器时钟。NCO累加器输入端的误差控制信号,即环路滤波器的输出,可以改变产生的脉冲频率,从而使本地PN码更加精确地对准输入信号PN码,完成跟踪。

NCO的跟踪精度和累加器的累加时钟以及累加寄存器大小有关,累加时钟频率通常较高,可以采用FPGA中时钟管理单元DCM对低频时钟进行倍频得到。

3 仿真结果

Simulink仿真所采用的接收机参数如下:

l PN码长度:15

l PN码码片速率:5Mbps

l 载波频率:10MHz

l 采样频率:40MHz

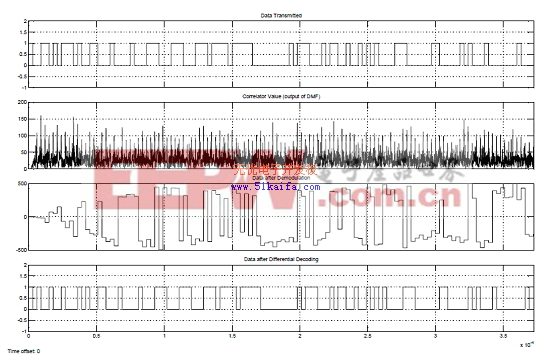

下面给出了在SNR= -5dB,多普勒频移100Hz的高斯信道下的Simulink仿真结果。为了解决BPSK解调的相位模糊问题,在发送端对信号进行了差分编码调制,在接收端进行差分译码。从最后的差分译码的结果可以看出,在经过几个码元周期后,信号能够被正确的解调。仿真结果表明,误码率可以达到10-5以下,满足系统既定要求。

图3 Simulink仿真结果

4 FPGA实现

实验用电路板上包括Xilinx公司FPGA XC2V500,AD公司的模数转换器AD9238,同时板上提供了与TI公司C6000系列评估板的接口。中频信号经过AD采样,利用FPGA实现扩频系统的解扩和解调等功能,通过EMIF接口将数据传给DSP,进一步完成通信系统中其他应用与设计,整个系统构成软件无线电通用平台。

系统采用同步设计方法,时钟源由电路板上40MHz石英振荡器提供。XC2V500高达50万门,其中集成了大量的乘法器,DCM以及全局时钟布线资源,给系统实现带来了很大的方便。系统在实现时需要多个时钟,主要由DCM分频和倍频得到。实现中,除了上述对电路进行的优化设计,在不影响系统性能的情况下,对运算的中间结果进行尾数截断,很大程度提高了硬件资源的利用率。

利用Verilog编程,XST综合,布局布线后,通过Modelsim后仿真验证电路的正确性,并最终在FPGA芯片上实现。芯片资源占用如下表,其中使用的Slice占FPGA中Slice总量的14%。

基本单元 | Slice | IO | BRAM | MULT18X18 | GCLK | DCM_ADV |

使用数量 | 451 | 19 | 1 | 9 | 7 | 2 |

5结论

本文作者创新点是提出了一种全数字差分BPSK扩频接收机的完整方案,并针对Xilinx公司FPGA特点,对系统电路结构进行优化设计,降低了硬件复杂度,实现了高速信号传输和低误码率的扩频接收机系统。

本中给出了系统的Simulink仿真结果,以及利用Verilog编程,通过综合和验证,在Xilinx XC2C500芯片上实现的结果,对工程实践有一定的指导意义。文中讨论的方法具有通用性,实际应用中可根据具体情况修改电路参数,以适用不同要求。

6参考文献

[1] 张欣 著. 扩频通信数字基带信号处理算法及其VLSI实现. 科学出版社. 2004.8.

[2] Jen-Shi Wu, Ming-Luen Liou, Hsi-Pin Ma, and Tzi-Dar Chiueh. A 2.6-V, 44-MHz all-digital QPSK direct-sequence spread-spectrum transceiver IC. IEEE Journal of solid-state circuits, vol. 32 No.10. October 1997

[3] 卿敏,沈业兵,安建平. 用FPGA实现数字匹配滤波器的优化方法. 微计算机信息. 2004年第20卷第11期.

[4] 郑继禹,林基明著. 同步理论与技术. 电子工业出版社. 2003.3

评论