某型数字射频存储器模数转换接口设计研究

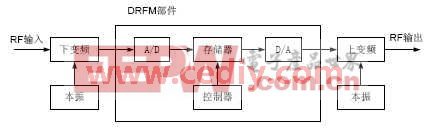

数字射频存储器(DRFM)采用高速采样和数字存储作为其技术基础,具有对射频和微波信号的存储和再现能力。DRFM技术作为存储和复制射频信号的一种方法广泛应用于雷达和电子对抗等领域。数字射频存储(DRFM)的基本工作原理:首先将输入射频信号下变频为中频信号,经A/D变换后成为数字信号,写入高速存储器中。当需要重发这一信号时,在控制器控制下读出此数字信号并由D/A变换为模拟信号。然后用同一本振作上变频,得到射频输出信号,完成对输入信号的存储转发。

DRFM的基本原理框图如下:

数字射频存储器的模拟前端-¬―即A/D、D/A部分,负责将中频信号数字化。模拟前端的设计质量直接关系到了整个系统能否满足高精度、高速、高可靠性的数据采集及回放。该部分的设计一直是数字频储系统的设计难点和重点。

二、模拟前端设计分析

目前高精度的ADC以及DAC器件信号均采用差分方式输入或者输出,这样可在转换性能上相对于单端信号有较大的优势,所以需要单端-差分的转换,一般有两种方法,一种是放大器方式,一种是变压器耦合方式。

采用放大器方式的优点是可以直流耦合。如果输入信号中含有丰富的低频分量,只能采用这种方法。但是采用放大器直流耦合将会带来以下4个问题:

1) 信号失真,主要由放大器的传输非线性造成。但是考虑到在本设计中输入信号幅度很小,放大器可以呈现出很好的线形特性,而且一般放大器的失真度很小,以典型的放大器差分AD8138为例,其谐波失真度均高于85dBC,远高于ADC本身的SFDR,所以在采样分辨率不是非常高的设计中由放大器带来的失真可以忽略。

2) 电源噪声。由于各种器件的功耗激增,现在电路系统几乎都采用高频、高效率的开关电源,虽然模拟电路中线性稳压器的采用不可避免,但是完全隔离这些开关噪声非常困难以致不太可能,还需要依赖放大器的电源抑制(Power Supply Rejection)特性。事实上普通放大器的电源抑制比均能达到70dB以上,只要电源处理得当,在本设计中电源噪声基本不用考虑。

3) 放大器偏移(Offset)。即放大器在输入为0时其输出并不为0,这样造成输入信号达不到满刻度输入范围,从而限制了变换的有效位数。差分放大器的偏移取决于差分两路信号的对称性,以AD8138为例,在通常器件下其偏移量在60mV左右。在本设计中信号输入的峰-峰值为1100mV,如果考虑放大器偏移可以算得真实有效位数为9.8位。

4) 放大器噪声。放大器各级均会引入噪声成分,因为放大器含有较多有源器件,将引入较多的有源噪声,以AD8138为例,其输入噪声为 ,并假设输入电路增益为+1,并且无滤波器,即3dB带宽为320MHz,可以算得输出噪声为90μV,能够满足在输入1100mV时10Bits分辨率的要求,但是难以达到比10Bits更高的采样精度。

,并假设输入电路增益为+1,并且无滤波器,即3dB带宽为320MHz,可以算得输出噪声为90μV,能够满足在输入1100mV时10Bits分辨率的要求,但是难以达到比10Bits更高的采样精度。

如果采用变压器耦合方式,由于其为无源器件,上面放大器所有的4个问题并不存在,但是变压器耦合会隔离直流以及一部分的低频信号,一般射频变压器的3dB带宽下限为数百KHz,这个损耗是否能被接收取决与详细设计要求。

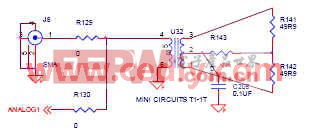

由以上分析可知,由于采用放大器的前端设计在偏移、噪声等指标上已经逼近10-bit采样精度的极限,由于在电路实现过程中的一些不可预知的因素将造成性能指标的进一步下降,所以采用放大器的方案几乎不可能实现指标要求。另外最近推出的一系列高性能ADC所附评估板设计中均只推荐了变压器耦合方式,如Maxim的MAX1215,ADI的AD9430、AD9446以及TI的ADS5500等。所以本系统中所有ADC和DAC前端设计均采用了变压器的耦合形式,如下原理图所示:

在一般情况下模拟电路对开关电源的开关脉冲非常敏感,通常模拟电路均使用线性电源,所以在设计模拟电路电源时,需要加入线性稳压器。在本设计中,正模拟电源需要1.8V,3.3V,5V三种。如果采用变压器耦合方式,可以在设计中避免需要负电源,所以变压器耦合方式不但可以简化信号前端处理,同时也可简化电源设计。

如果直接将机箱电源经过线性稳压后直接生成模拟电源,会面临两个问题:

1) 现代开关电源为了兼顾较高的效率并为了降低所用元器件的体积,一般开关电源的开关频率比较高,这样对线性稳压器件的纹波抑制性能提出了较高的要求。

2) 线性稳压的效率直接受输入和输出电压压差影响,这个压差越大,在稳压器上损耗的功率就越大。

为了缓解这2个问题,可以加入一级开关电源预降压,将电源的开关频率转为几十KHz,而线性稳压器对这样频率的纹波典型的抑制比为40dB,假设开关电源预降压后纹波为100mv,不考虑其它噪声源,则经过线性稳压后纹波电压降为1mv,相对于Max1124所给出的1.6mv/V的电源抑制比,这个纹波可以被忽略。模拟电路的所有正电压可以由下图所示方案生成:

在上图方案中未考虑负电源的生成。数字电路虽然对电源噪声不太敏感,但是其消耗的功率很大,并且对于上电初始化的要求比较严格。以FPGA为例,如果在上电时电源波动太大并且这些电源直接供给FPGA的话,FPGA上电初始化就可能无法顺利完成,这个现象我们已经在几种Pentium IV机箱中发现。我们在研制的一个PCI板卡上发现如果FPGA的I/O电压直接采用来自底板的+3.3V电源,在机箱上电时会因为+3.3V的波动较为剧烈而造成FPGA程序加载过程失败,而解决这个问题比较好的方法是在板上应用稳压器件生成所需要的各种电源,同时还提供了对板上各种昂贵的器件提供保护。这也是大部分商用板卡所采用的电源方案。

为了减小电路板尺寸和板上器件数,可以采用多路开关电源控制器,同时生成FPGA以及其它器件所需的核电压和外围电压。因为一般机箱电源+5V输出功率最大,所以各种电压最好用+5V来生成。由于开关电源控制器均可提供一定的软上电(Soft Start)功能,可以使DSP或者FPGA之类的芯片能够正常初始化。在本设计中即采用了SEMTECH的SC2446开关电源控制器,其能同时控制两路电源输出。这样FPGA的内核电压以及I/O电压即可按照一定的时序关系给出,保证了FPGA上电初始化的正常进行。而SC2446输出的两路电源之间还具有良好的跟踪特性,这个特性非常适合作为DDR SDRAM的稳压器件,由其同时输出DDR SDRAM所需要的2.5V I/O电压以及1.25V端接和参考电压可以保持很好的同步关系,提高了存储系统的抗噪能力。所以在本板设计中还采用了SC2446作为DDR SDRAM的电源提供器件,由2片SC2446生成了所有数字电路所需要的+3.3V、+1.5V、+2.5V、+1.25V四种电压。

三、结论

在本数字射频存储器的模拟前端设计过程中,采用了变压器耦合方式来解决了单端至差分的转换问题,并给出了实现原理图。同时采取了多项措施,解决了直接将机箱电源经过线性稳压后直接生成模拟电源,所带来的对线性稳压器件的纹波抑制性能要求较高和稳压器损耗功率较大的问题。

评论