FIR数字滤波器的FPGA实现研究

2.4 3种结构实现的比较

改进串行结构、并行结构、DA结构实现的比较如下:

1)改进串行结构 ①优点:使用资源少,只需一些寄存器、乘累加器便可完成整个滤波运算;②缺点:滤波速度慢,一次滤波所需的时钟数由滤波器的阶数决定。阶数较高的滤波器,滤波周期很大,无法实现高速滤波。

2)并行结构 ①优点:完成滤波的速度快,直接并行滤波器可以在一个时钟周期内完成一次滤波;②缺点:消耗大量的乘累加器,器件延迟较大,工作频率不可能太高。

3)DA结构 与串行结构实现相比,DA实现滤波速度较快,其滤波周期由数据宽度决定而与滤波器的阶数无关;而与并行实现相比,DA实现消耗的资源较少。且容易实现流水线处理,提高电路的执行速度。

在设计中,当资源成本为主要制约时,根据速度要求,选择串行结构实现或DA结构实现;而当速度成为主要制约时,则根据资源成本因素,选择并行实现结构或DA结构实现。在一般的应用设计中,一般采用DA结构实现。

3 实例设计与仿真

3.1 FIR滤波器的设计

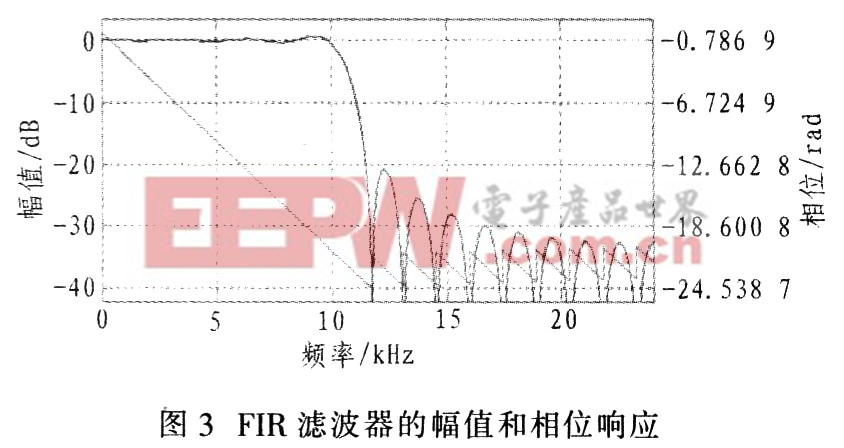

利用Matlab中的FDATool工具设计一个33阶,Fs=48kHz,Fc=10.8 kHz的FIR滤波器,其幅值、相位响应见图3。为了便于FIR滤波器的FPGA实现,减小误差,将滤波器的系数量化取整后,在FPGA中实现采用的滤波系数为{-11,14,18,-11,-25,4,32,6,-38,-21,43,45,-47,-96,50,319,457,319,50,-96,-47,45,43,-21,-38,6,32,4,-25,-11,18,14,-11}。本文引用地址:https://www.eepw.com.cn/article/157476.htm

3.2 FIR滤波器的FPGA实现与仿真

在Xilinx 10.1 ISE平台中,选用Virtex-5系列的XC5VSXT50T器件,用Verilog HDL语言设计串行结构、并行结构的、以及DA结构,并在ModelSim中对3种结构实现进行仿真。设计中输入数据的位宽设为16位,而输入数据在运算处理前位宽扩展到17位。所用仿真激励为单位阶跃响应,时钟周期为Tck=10 ns。ModelSim中的仿真结果如图4所示。

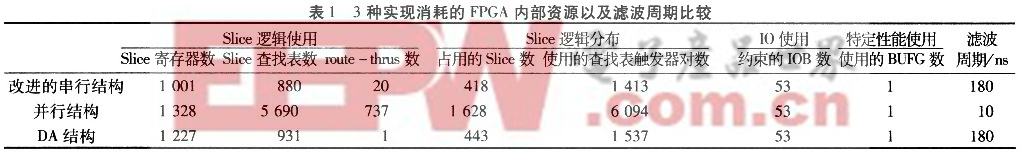

图4中依次为改进的串行实现,并行实现和DA实现的仿真结果,其滤波周期分别为180 ns,10 ns和180 ns。上述设计的改进串行结构、并行结构和DA结构分别在XC5VSX50T中实现后,所消耗的FPGA内部各种资源如表1所示。

从表l可以看出,并行实现消耗的资源最多,其次是DA实现,最小是串行实现。而从滤波速度上来看,并行滤波速度最快,1个时钟周期便可滤波1次;而串行实现速度慢,其滤波周期取决于滤波器的阶数,对17阶的对称滤波器而言,滤波一次占9个时钟周期,滤波输出占1个时钟周期;相对串行实现和并行实现,DA实现的滤波周期取决于处理的数据宽度,上述设计中DA实现的滤波处理数据位宽是17位,所以滤波一次占17个时钟周期,滤波输出占用1个时钟周期。

4 结束语

在实际应用中,当滤波器设计对滤波速度要求不高时,可采用串行结构或改进串行结构来实现,这样可以选取资源较少的器件,降低设计成本;当对滤波速度有较高要求时,可以考虑采用并行或DA来实现。并行实现滤波周期为时钟周期,速度快,但消耗的资源多,成本高;DA实现速度较快,消耗的资源较少,成本耗费较低。在数字多普勒接收机的实现过程中,根据接收机的性能要求以及所选用的FPGA器件资源,选取最优的FlR滤波器实现结构。随着FPGA查找技术的发展,具有较快的滤波速度和消耗较少资源的DA算法在FIR数字滤波领域得到了广泛应用。

评论