基于单片机和DDS的高精度频率信号实现

介绍了专用DDS芯片AD9854的特性和工作原理,叙述了利用该芯片设计高精度频率信号发生器的简易方法,并给出了MCS51系列单片机与AD9854的硬件接口设计和软件编程方法。

本文引用地址:https://www.eepw.com.cn/article/156230.htm高精度的频率信号源对科研、通信系统、电子对抗以及各种电子测量技术十分重要。目前,国内低频信号合成器通常使用多个分立的锁相环元件,电路复杂、价格昂贵、精度低、易受外界环境影响,而且信号的建立时间长而动态范围较小。九十年代迅速发展起来的直接数字合成技术(DDS)将先进的数字处理技术与方法引入信号合成领域,优越的性能和突出的特点使其成为现代频率合成技术中的佼佼者。DDS器件采用高速数字电路和高速D/A转换技术,具备了频率转换时间短、频率分辨率高、频率稳定度高、输出信号频率和相位可快速程控切换等优点,可以实现对信号的全数字式调制。

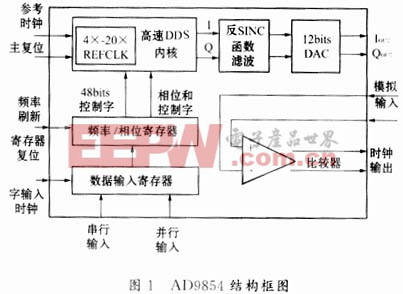

1 AD9854芯片介绍

AD9854是美国ADI公司最近推出的单片DDS芯片,简单结构框图如图1所示。它的主要特点为:内部高速、高性能的正交D/A转换器和高速比较器实现数字合成的正交的I和Q路输出。当输入一准确的参考频率,AD9854就产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本机振荡器用于通信、雷达等方面。AD9854的DDS核具有48bit的频率分辨率(1mHz步进),相位截断17bit保证了优良的无杂散动态比(SFDR)指标。

AD9854采用了先进的35微米CMOS技术,使它只需+3.3V的电源供应,它的电路工艺使同步正交信号输出的频率最高达150MHz,平均每秒产生100百万新频率。正弦信号输出经过外部平滑滤波后,可以通过内部比较器转化成方波,用于时钟产生。在高速时钟产生器的应用中,若12bit的“控制”DAC与内部的比较器相结合,能实现脉宽调制和静态周期控制。两个12bit的数字乘法器能实现数字幅度调制、波形成形和正交输出的准确的幅度控制。AD9854中4~20整数倍频器,能把外部输入的低速时钟转变成内部高速时钟(最高300MHz)。参考时钟可以选择单端输入和差分输入。

AD9854合成的信号频率稳定度高,DDS是一个信号波形的合成过程,是以标准参考振荡源的固定时钟作取样时钟,对所需频率的信号进行相位取样,合成信号的频率不同,只反映了一个信号周期内的相位取样的数量不同。合成信号的稳定度直接由参考源的相位噪声决定,甚至还要低。合成信号的稳定度高,理论上可达STCLK/242Hz,这是传统方法难以实现的。频率变化速度快,在AD9854中,由于无需相位反馈控制,因而频率建立及切换快,并且与频率分辨率、频谱纯度相互独立。在芯片中,NCO的相位改变是线性过程,形成的信号具有良好的频谱。此外,由于合成信号的频率、相位、幅度均可由数字信号控制,所以可以通过预置相位累加器的初始值来精确控制合成信号的相位,非常容易实现灵活的高精度的数字调制,如AM、PSK、FSK、MSK等,而且容易实现高精度的正交调制。

2 用AD9854快速开发频率信号发生器的实例

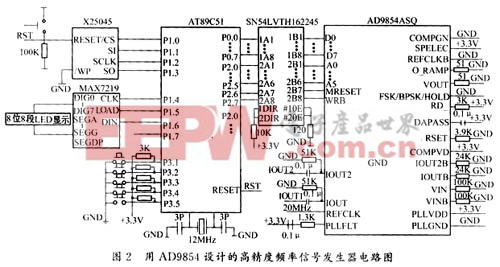

下面给出一种用AD9854开发高精度频率信号发生器的简易方法,开发者只需要熟悉MCS-51单片机编程即可。该系统具有开发周期短,开发成本低的特点,也可以作为探索AD9854功能的一种方法,它的电路原理图见图2。

系统主要由DDS芯片AD9854、单片机AT89C51、看门狗定时器X25045和LED显示驱动芯片MAX7219组成。在这个系统中提供了8位七段LED显示器,其中前五位为输出频率值,显示范围为00.000~99.999MHz,后三位为幅度显示位,显示范围为0~999,表示幅值从零幅度到满幅度的变化。

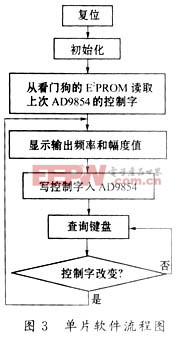

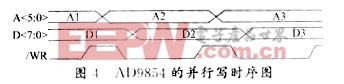

对AD9854进行初始化控制时,首先,主复位脚(71脚)必须置高10个系统周期以上,主复位的作用是初始化系统总线,置控制寄存器以缺省值。在系统中,用MCS-51系列单片机对AD9854进行控制,软件流程图如图3所示。实现并行写时序时序图如图4所示,可以使用以下语句:

MOV p0,#10h

MOV A,#1DH

ADD A,#40H

MOV P2,A

CLR WRITE

NOP

SETB WRITE

MOV A,#1DH

ADD A,#40H

MOV P2,A

CLR WRITE

NOP

SETB WRITE

NOP

在这个系统中,有5个按键,分别完成光标(回车)、光标左移、光标右移、加1和减1的功能,变换后的值经光标(回车)确认后,乞讨变单片机内RAM地址区所对应的AD9854的频率和幅度控制字,然后写入到AD9854缓存内。每一次上电时,单片机从看门狗的E2PROM中读取上一次断电时保存在里面的AD9854的控制参数,LED显示器显示与断电前相同的频率和幅度值,并完成对AD9854相同的初始化。

SN54LVTH16625是一个电平转换芯片,它把单片机P0口和P2口输出的5V电平转换成3.3V电平,实现和AD9854的接口。由于AT89C51的P0口内部没有上拉电阻,在实际调试过程中,外接了8个4.7kΩ的上拉电阻,P0口和P2口本身都具有锁存功能。

AD9854是一个高性能、多功能,但又使用简单的芯片,它只需写入少量的控制字,即可实现不同的功能。在编程调试的过程中,它的刷新时钟值得重视,通过写端口写入AD9854的控制字暂时寄存在I/O缓冲寄存器中,需要一从低到高的时钟信号由20脚从外部输入,或者由内部32bit的刷新时钟把I/O缓冲寄存器中的控制字传送到DDS的内核。AD9854分为AST型和ASQ型,后者属于耐热型,内部倍频后的时钟可达300MHz,前者只能倍频至200MHz。在图2所示的系统中,提供给AD9854的参考时钟为20MHz,在芯片内部进行10倍频,并且使用的是内部刷新时钟,这时,UPDATE脚(20脚)是作为输出脚,在主复位之后,写入的控制字还没有送入DDS内核时,20脚输出10倍于系统周期的时钟信号,完成初始化之后,则输出2倍于系统周期的时钟,这也是判断控制字是否送入AD9854内核的一个标志,在调试中要特别注意。在本例中,屏蔽了反SINC滤波模块,因为它的功耗高达1W,需要给芯片提供良好的散热条件。

输出I或Q路信号,是经AD9854内部12bitD/A转换之后的模拟波形,但并非平滑的正弦波,需经低通滤波器平滑后,即可得到预期的波形。把滤波后的I和Q通过42、43脚输入,经过高速比较器,即可得到方波信号,方波信号经简单的变换,可得到三角波、锯齿波等。

3 结束语

本文介绍的基于AD9854的高精度频率信号发生器的设计方法设计的信号源,已经用于科研项目中。它体积小、重量轻,而且在此基础上,通过给AD9854提供数据源,简单地改变写入AD9854的控制字,可以实现AD9854所能提供的各种调制信号。把DDS技术与FPGA器件、计算机技术结合到一起,其操作更灵活,应用范围更广泛。由于市场上好几个系列的FPGA器件都能在一定程度上具备动态重构的能力,可以利用可视化编程工具Visual C++,实现并口数据位线给FPGA下载AD9854的控制程序,用FPGA器件实现AD9854的不同控制。实验表明,上述方法都能够达到AD9854给定的性能指标。AD9854作为一个性价比较高的DDS芯片,具有极广阔的应用前景。

评论