基于MPSoC的以太网接口设计与实现

2.1 帧格式定义

图3所示为两种协议的数据格式定义。以太网IP核用户接口数据以帧格式定义数据的输出或输入,数据宽度为8位,帧数据长度范围为64~1 518 Byte,在具体硬件设计中一般选择固定数据长度传输,使硬件结构设计简单。具体格式如图3(a)所示,先输入的数据为目的网卡的网络地址,数据长度为6Byte。其次是6 Byte的源片网络地址。接着为帧传输定义的类型或数据传输长度,长度占2 Byte,数据长度通常在数据帧比较短情况指定。如0010,表示后面传输的16个数据是有效的,传输多余长度的数据,以太网控制器IP核默认为无效数据。而采用类型定义来传输帧,在数据传输长度范围内,结束控制信号以前的数据都表示为有效数据。文中选用512的固定数据传输长度和8 000标识的帧类型完成硬件设计。本文引用地址:https://www.eepw.com.cn/article/155185.htm

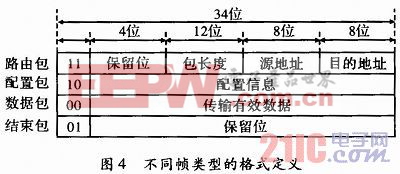

网路接口数据包格式如图3(b)所示,数据深度定义为变长,数据宽度为34位,为多核系统实时高效的数据传输提供良好的协调作用。第一个数据为系统网络协议的路由包,其后一个数据为配置信息,称为配置包。接着为不定长度有效数据包。有效数据包发送结束后,紧接着发送一个数据结束包。

网路数据包中不同包类型的格式定义,具体描述如图4所示,数据高2位标识不同包格式类型。当高2位为11 B时,标识为路由包,其中第28~17位表示传输的数据长度,第16位到第9位定义数据源传播的网络坐标地址,低8位定义为数据通讯的目的网络地址,剩下数据位定义为保留位。当高2位为10B时,标识为配置包,其他位根据通信需求,设置不同配置信息。当高2位为00B时,标识为数据包,剩余位为传输的有效数据信息。当高2位为01B时,标识为结束包,其它位为保留位。

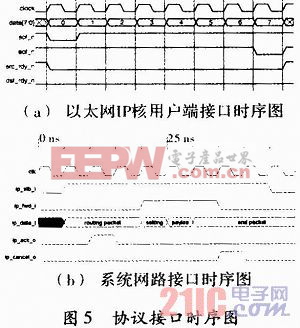

2.2 接口时序图

以太网控制器IP核接口时序如图5(a)所示。主要有3类信号:时钟信号、控制信号和数据信号。时钟信号为clock。而控制信号有sof_ n、eof_n、scr_rdy_n,其中sof_n表示帧传输开始控制信号,eof_n为帧传输结束控制信号,scr_rdy_n为传输有效控制信号,控制信号均为低电平有效。用户端数据信号为Data。网路接口侧时序图如图5(b)所示。信号包括ip_stb、ip_ack、ip_fail、ip_fwd、ip_cancal、ip_sus pond。它们为多核系统网络通讯的完成握手应答传输机制。控制信号均为高电平有效,ip_data是数据传输信号。

2.3 发送模块设计

发送模块完成数据以太网IP核接口到网路的数据接口协议转换,如图2所示。该模块包括发送读控制器,发送数据缓存模块和发送写控制器。发送读控制器完成目的地址、源地址和数据类型的数据信息截断,把传播的有效数据写入发送数据缓存模块中,设计通过一个有限状态机结合计数器来完成功能的实现。发送数据缓存模块用一个异步FIFO来承担,同时完成数据8~32位的数据宽度扩展,同时完成跨时钟域数据传输任务。由于该模块数据读入是高时钟频率的8位数据,数据读出是系统时钟频率下的32位数据,数据的流动是由慢到快的传递过程,因此选用一个深度为64的FIFO单元来承担。发送写控制模块通过读取缓存模块中的数据,配置发送数据的有效信息,完成网络数据包格式封装,最后传输至多核系统通信网络资源接口。

2.4 接收模块设计

接收模块承担网络数据包协议到以太网IP核接口协议转换,包含接收写控制器、接收数据缓存模块和接收读控制器。接收写控制器模块设计,通过网络控制信号和FIFO标识信号以及当前状态改变状态机的状态跳转。根据不同状态产生控制信号,实现网络包、配置包、结束包和负载信息的截取,把传播的有效数据写入数据缓冲模块。数据缓存模块把32位网络数据转换到8位宽的以太网控制器接口数据,同时实现数据跨时钟域传输任务。该数据流动方向,速度是由快到慢的过程,结合硬件逻辑资源和任务请求的频度,该设计选用一个深度为1 024,宽度为32的异步FIFO单元来承担。接收读控制器模块通过读取缓存FIFO中数据,配置发送数据的源和目的网卡地址及帧类型,完成以太网数据帧的封装,传输至以太网IP核用户端接口。

评论