嵌入式系统降低功耗的方法研究

摘要 低功耗嵌入式系统设计的能量消耗问题是近几年来在嵌入式系统设计中普遍关注的难点与热点,它严重制约着嵌入式系统的应用及发展。本文以降低嵌入式系统所耗电能为目标,提出了嵌入式系统降低功耗的综合措施,并对低功耗嵌入式系统各种经典措施进行优化改进,使之充分发挥降低功耗的作用。最后阐述了该解决措施尚存在的一些关键问题,并对低功耗嵌入式系统的前景和发展进行了评述。

关键词 低功耗硬件设计 低功耗软件设计 DVS DPM

引 言

随着嵌入式系统应用的迅速发展,PDA和移动电话等便携式装置深入到生产生活的各个角落,嵌入式系统市场有迅速增长趋势。嵌入式系统一般是由电池来供给电能的,而且大多数嵌入式设备都有体积和重量的约束。减少电能消耗不仅能延长电池的寿命,缩短用户更换电池的周期,而且能提高系统性能与减小系统开销,甚至能起到保护环境的作用。

1 嵌入式系统功耗分析

研究微处理器的低功耗设计技术,首先必须了解它的功耗来源。如图1所示,从高层次仿真得出的结论可以看出,通过开关级功率模拟所获得的高性能CPU的功率分布关系。其中,时钟功耗所占比例最大,包括时钟发生、驱动器、时钟树、锁存器和所有时钟负担的器件;数据通路的功耗仅次于时钟,主要包括执行单元、总线和寄存器文件;片上存储器的功耗主要由存储器的大小以及存储阵列的电路和物理结构所决定;控制单元和I/O的功耗通常占整个芯片功耗的一小部分。

2 嵌入式系统低功耗设计

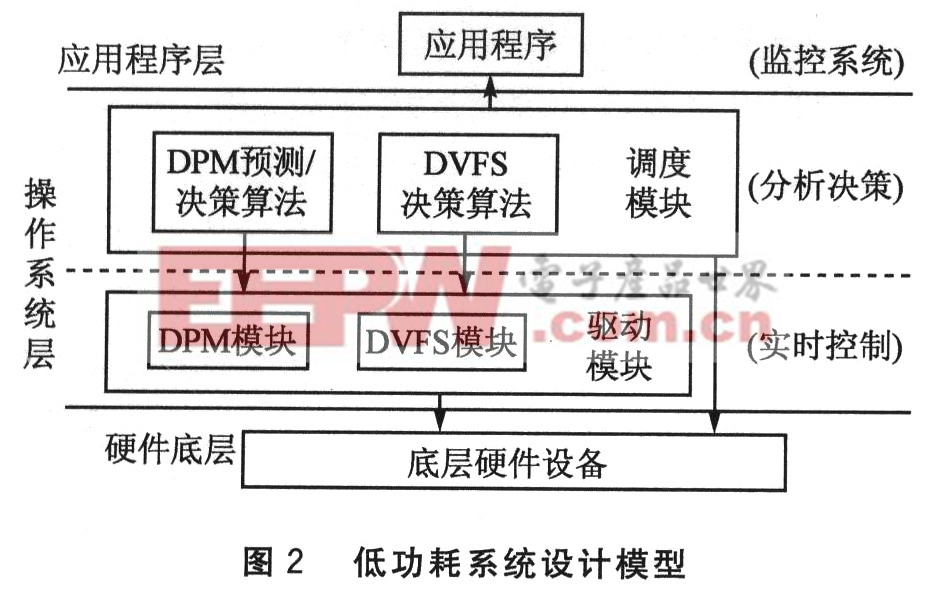

低功耗设计是一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自硬件底层至应用程序层的所有抽象层次,而目前低功耗设计大都在操作系统层实施,如图2所示。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面根据各部分在嵌入式系统中的不同层次,讨论常用的低功耗设计技术及具体应用。

2.1 低功耗硬件设计

低功耗硬件设计是嵌入式系统降低功耗的重要内容。因此,需要从系统内部结构设计、系统时钟设计和低功耗模式等几方面采用特定的方法(例如,门控时钟和可变频率时钟、并行结构与流水线技术、低功耗单元库、低功耗状态机编码、Cache低功耗设计等)来实现系统硬件节能设计。下面介绍门控时钟和可变频率时钟的应用。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产生很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而显著降低开关功耗。图3为采用“与”门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

评论